Aging Modeling and Simulation of the Gate Switching Instability Degradation in SiC MOSFETs

Subject:

Reliability

Device modeling

Silicon Carbide (SiC)

Gate Switching Instability (GSI)

Publication date:

Editorial:

IEEE

Abstract:

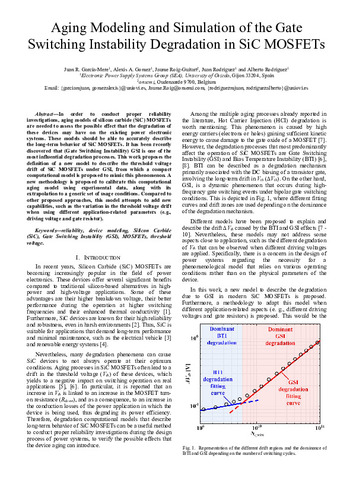

In order to conduct proper reliability investigations, aging models of silicon carbide (SiC) MOSFETs are needed to assess the possible effect that the degradation of these devices may have on the existing power electronic systems. These models should be able to accurately describe the long-term behavior of SiC MOSFETs. It has been recently discovered that (Gate Switching Instability) GSI is one of the most influential degradation processes. This work proposes the definition of a new model to describe the threshold voltage drift of SiC MOSFETs under GSI, from which a compact computational model is proposed to mimic this phenomenon. A new methodology is proposed to calibrate this computational aging model using experimental data, along with its extrapolation to a generic set of usage conditions. Compared to other proposed approaches, this model attempts to add new capabilities, such as the variation in the threshold voltage drift when using different application-related parameters (e.g., driving voltage and gate resistor).

In order to conduct proper reliability investigations, aging models of silicon carbide (SiC) MOSFETs are needed to assess the possible effect that the degradation of these devices may have on the existing power electronic systems. These models should be able to accurately describe the long-term behavior of SiC MOSFETs. It has been recently discovered that (Gate Switching Instability) GSI is one of the most influential degradation processes. This work proposes the definition of a new model to describe the threshold voltage drift of SiC MOSFETs under GSI, from which a compact computational model is proposed to mimic this phenomenon. A new methodology is proposed to calibrate this computational aging model using experimental data, along with its extrapolation to a generic set of usage conditions. Compared to other proposed approaches, this model attempts to add new capabilities, such as the variation in the threshold voltage drift when using different application-related parameters (e.g., driving voltage and gate resistor).

Description:

Applied Power Electronics Conference and Exposition (2024. Long Beach, USA)

Patrocinado por:

This work was supported in part by Ministerio de Ciencia e Innovación, by Agencia Estatal de Investigación and by FEDER under Project PID2022-136969OB-I00, and in part by the Principality of Asturias under “Severo Ochoa” Program Grants no. BP20-181 and BP21-114 and under Project SV-PA-21-AYUD/2021/51931.

Collections

Files in this item