Design of a high performance VLC-LED driver for Visible Light Communication based on the split of the power

Palabra(s) clave:

Light emitting diodes

DC-DC power converters

Task analysis

High frequency

Fecha de publicación:

Editorial:

IEEE

Resumen:

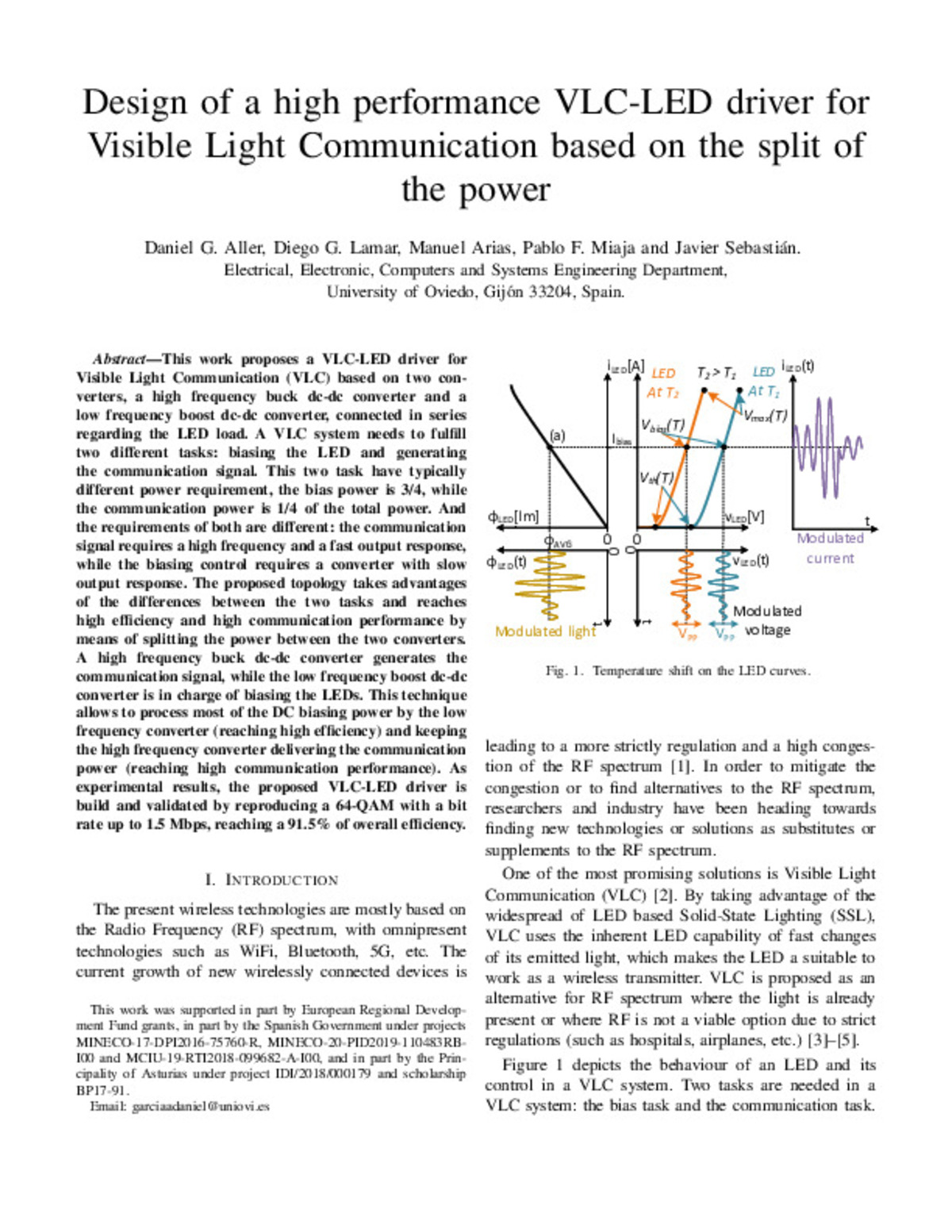

This work proposes a VLC-LED driver for Visible Light Communication (VLC) based on two converters, a high frequency buck dc-dc converter and a low frequency boost dc-dc converter, connected in series regarding the LED load. A VLC system needs to fulfill two different tasks: biasing the LED and generating the communication signal. This two task have typically different power requirement, the bias power is 3/4, while the communication power is 1/4 of the total power. And the requirements of both are different: the communication signal requires a high frequency and a fast output response, while the biasing control requires a converter with slow output response. The proposed topology takes advantages of the differences between the two tasks and reaches high efficiency and high communication performance by means of splitting the power between the two converters. A high frequency buck dc-dc converter generates the communication signal, while the low frequency boost dc-dc converter is in charge of biasing the LEDs. This technique allows to process most of the DC biasing power by the low frequency converter (reaching high efficiency) and keeping the high frequency converter delivering the communication power (reaching high communication performance). As experimental results, the proposed VLC-LED driver is build and validated by reproducing a 64-QAM with a bit rate up to 1.5 Mbps, reaching a 91.5% of overall efficiency.

This work proposes a VLC-LED driver for Visible Light Communication (VLC) based on two converters, a high frequency buck dc-dc converter and a low frequency boost dc-dc converter, connected in series regarding the LED load. A VLC system needs to fulfill two different tasks: biasing the LED and generating the communication signal. This two task have typically different power requirement, the bias power is 3/4, while the communication power is 1/4 of the total power. And the requirements of both are different: the communication signal requires a high frequency and a fast output response, while the biasing control requires a converter with slow output response. The proposed topology takes advantages of the differences between the two tasks and reaches high efficiency and high communication performance by means of splitting the power between the two converters. A high frequency buck dc-dc converter generates the communication signal, while the low frequency boost dc-dc converter is in charge of biasing the LEDs. This technique allows to process most of the DC biasing power by the low frequency converter (reaching high efficiency) and keeping the high frequency converter delivering the communication power (reaching high communication performance). As experimental results, the proposed VLC-LED driver is build and validated by reproducing a 64-QAM with a bit rate up to 1.5 Mbps, reaching a 91.5% of overall efficiency.

Descripción:

IEEE Workshop on Control and Modeling for Power Electronics (COMPEL) (21st. 2020. Aalborg, Denmark)

ISBN:

Patrocinado por:

Este trabajo fue apoyado en parte por European Regional Development-subvenciones del Fondo de mentores, en parte del Gobierno español en proyectos MINECO-17-DPI2016-75760-R, MINECO-20-PID2019-110483RB-I00 y MCIU-19-RTI2018-099682-A-I00, y en parte por el Principado de Asturias bajo proyecto IDI / 2018/000179 y beca BP17-91.

Colecciones

Ficheros en el ítem