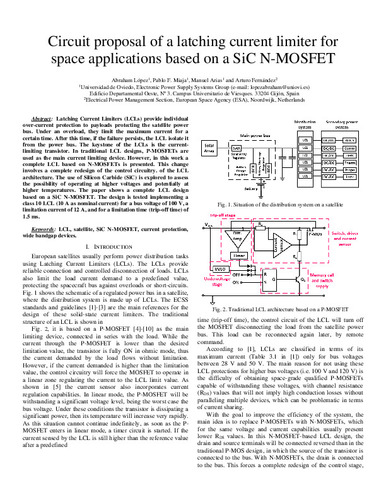

Circuit proposal of a latching current limiter for space applications based on a SiC N-MOSFET

Palabra(s) clave:

LCL

Current protection

Wide bandgap devices

Satellite

Fecha de publicación:

Editorial:

IEEE

Versión del editor:

Citación:

Resumen:

Latching Current Limiters (LCLs) provide individual over-current protection to payloads protecting the satellite power bus. Under an overload, they limit the maximum current for a certain time. After this time, if the failure persists, the LCL isolate it from the power bus. The keystone of the LCLs is the current-limiting transistor. In traditional LCL designs, P-MOSFETs are used as the main current limiting device. However, in this work a complete LCL based on N-MOSFETs is presented. This change involves a complete redesign of the control circuitry. of the LCL architecture. The use of Silicon Carbide (SiC) is explored to assess the possibility of operating at higher voltages and potentially at higher temperatures. The paper shows a complete LCL design based on a SiC N-MOSFET. The design is tested implementing a class 10 LCL (10 A as nominal current) for a bus voltage of 100 V, a limitation current of 12 A, and for a limitation time (trip-off time) of 1.5 ms.

Latching Current Limiters (LCLs) provide individual over-current protection to payloads protecting the satellite power bus. Under an overload, they limit the maximum current for a certain time. After this time, if the failure persists, the LCL isolate it from the power bus. The keystone of the LCLs is the current-limiting transistor. In traditional LCL designs, P-MOSFETs are used as the main current limiting device. However, in this work a complete LCL based on N-MOSFETs is presented. This change involves a complete redesign of the control circuitry. of the LCL architecture. The use of Silicon Carbide (SiC) is explored to assess the possibility of operating at higher voltages and potentially at higher temperatures. The paper shows a complete LCL design based on a SiC N-MOSFET. The design is tested implementing a class 10 LCL (10 A as nominal current) for a bus voltage of 100 V, a limitation current of 12 A, and for a limitation time (trip-off time) of 1.5 ms.

Patrocinado por:

This work has been carried out by funding from the Spanish government through the RTI2018-099682-A-I00 project, the PID2021-127707OB-C21 project, the PRE2019-088425 grant, and from the European Space Agency (ESA) through the “SiC Latching Current Limiter Study” contract.

Colecciones

Ficheros en el ítem