Análisis y diseño de un limitador de corriente de enclavamiento basado en un MOSFET tipo N de SiC

Autor(es) y otros:

Palabra(s) clave:

LCL

SiC

Dispositivos WBG

Fecha de publicación:

Resumen:

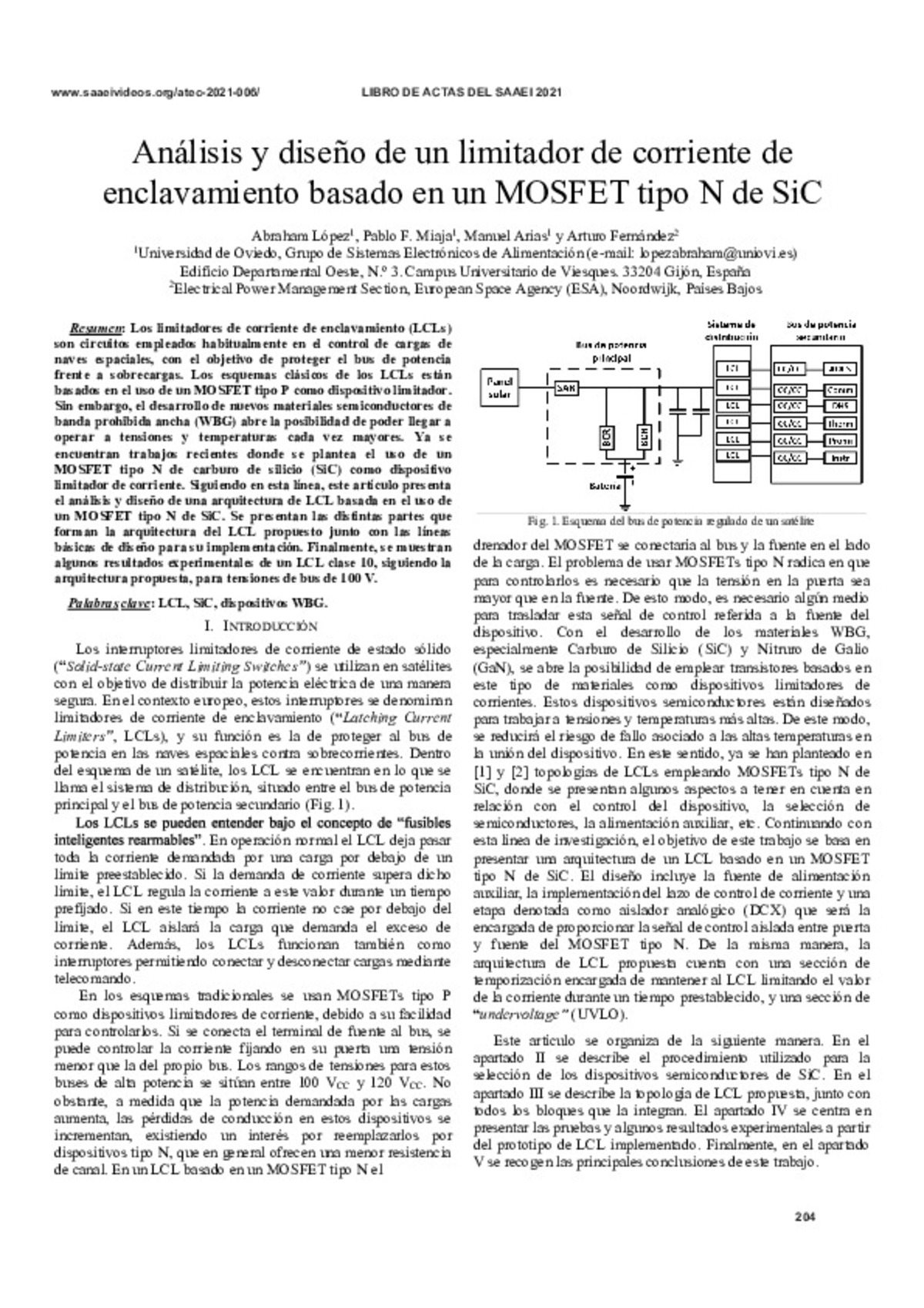

Los limitadores de corriente de enclavamiento (LCLs) son circuitos empleados habitualmente en el control de cargas de naves espaciales, con el objetivo de proteger el bus de potencia frente a sobrecargas. Los esquemas clásicos de los LCLs están basados en el uso de un MOSFET tipo P como dispositivo limitador. Sin embargo, el desarrollo de nuevos materiales semiconductores de banda prohibida ancha (WBG) abre la posibilidad de poder llegar a operar a tensiones y temperaturas cada vez mayores. Ya se encuentran trabajos recientes donde se plantea el uso de un MOSFET tipo N de carburo de silicio (SiC) como dispositivo limitador de corriente. Siguiendo en esta línea, este artículo presenta el análisis y diseño de una arquitectura de LCL basada en el uso de un MOSFET tipo N de SiC. Se presentan las distintas partes que forman la arquitectura del LCL propuesto junto con las líneas básicas de diseño para su implementación. Finalmente, se muestran algunos resultados experimentales de un LCL clase 10, siguiendo la arquitectura propuesta, para tensiones de bus de 100 V.

Los limitadores de corriente de enclavamiento (LCLs) son circuitos empleados habitualmente en el control de cargas de naves espaciales, con el objetivo de proteger el bus de potencia frente a sobrecargas. Los esquemas clásicos de los LCLs están basados en el uso de un MOSFET tipo P como dispositivo limitador. Sin embargo, el desarrollo de nuevos materiales semiconductores de banda prohibida ancha (WBG) abre la posibilidad de poder llegar a operar a tensiones y temperaturas cada vez mayores. Ya se encuentran trabajos recientes donde se plantea el uso de un MOSFET tipo N de carburo de silicio (SiC) como dispositivo limitador de corriente. Siguiendo en esta línea, este artículo presenta el análisis y diseño de una arquitectura de LCL basada en el uso de un MOSFET tipo N de SiC. Se presentan las distintas partes que forman la arquitectura del LCL propuesto junto con las líneas básicas de diseño para su implementación. Finalmente, se muestran algunos resultados experimentales de un LCL clase 10, siguiendo la arquitectura propuesta, para tensiones de bus de 100 V.

Descripción:

XXVIII Seminario Anual de Automática, Electrónica Industrial e Instrumentación 2021 (SAAEI'21), 7-9 de julio, Ciudad Real (España)

Patrocinado por:

Trabajo realizado mediante la financiación del Ministerio de Ciencia e Innovación a través del proyecto RTI2018-099682-AI00, la financiación de la Agencia Espacial Europea mediante el contrato SiC Latching Current Limiter Study y la beca predoctoral con referencia PRE2019-088425.

Colecciones

Ficheros en el ítem