# DEPARTAMENTO DE INGENIERÍA ELÉCTRICA, ELECTRÓNICA, DE COMUNICACIONES Y DE SISTEMAS

# PROGRAMA DE DOCTORADO EN INGENIERÍA ELÉCTRICA Y ELECTRÓNICA

#### TESIS DOCTORAL

# ESTUDIO Y DESARROLLO DE CONVERTIDORES MODULARES PARA APLICACIONES ESPACIALES

ABRAHAM LÓPEZ ANTUÑA

DEPARTAMENTO DE INGENIERÍA ELÉCTRICA, ELECTRÓNICA, DE COMUNICACIONES Y DE SISTEMAS

PROGRAMA DE DOCTORADO EN INGENIERÍA ELÉCTRICA Y ELECTRÓNICA

#### TESIS DOCTORAL

# ESTUDIO Y DESARROLLO DE CONVERTIDORES MODULARES PARA APLICACIONES ESPACIALES

#### ABRAHAM LÓPEZ ANTUÑA

#### DIRECTORES DE TESIS:

MANUEL ARIAS PÉREZ DE AZPEITIA / PABLO FERNÁNDEZ MIAJA

#### RESUMEN DEL CONTENIDO DE TESIS DOCTORAL

| 1 Título de la Tesis        |                                  |  |  |  |

|-----------------------------|----------------------------------|--|--|--|

|                             | Inglés: Analysis and development |  |  |  |

| desarrollo de convertidores | of modular converters for space  |  |  |  |

| modulares para aplicaciones | applications                     |  |  |  |

| espaciales                  |                                  |  |  |  |

| 2 Autor                                                    |  |  |  |  |

|------------------------------------------------------------|--|--|--|--|

| Nombre: Abraham López                                      |  |  |  |  |

| Antuña                                                     |  |  |  |  |

|                                                            |  |  |  |  |

| Programa de Doctorado: Programa de doctorado en ingeniería |  |  |  |  |

| eléctrica y electrónica                                    |  |  |  |  |

| Órgano responsable: Centro internacional de postgrado      |  |  |  |  |

#### **RESUMEN** (en español)

El objetivo de este trabajo es proporcionar soluciones para hacer más eficientes tanto el bus de potencia principal, como el sistema de distribución, presentes en los satélites. Dada la proliferación y el uso masivo de satélites hoy en día, se hace necesario contar con implementaciones que permitan reutilizar ciertos bloques funcionales presentes en los mismos, entre las distintas misiones espaciales. De esta forma, se podrían reducir costes y tiempos de desarrollo.

Este trabajo de tesis comienza con una introducción a los sistemas en naves espaciales. De esta forma, en el <u>Capítulo 1</u> se introducirá el concepto de satélite, dese el punto de vista de sistema, así como también se describirán los principales subsistemas que lo forman. De igual forma, se hará una breve introducción histórica sobre el uso de los satélites, así como también sobre la continua y creciente evolución en su uso y en su demando de potencia.

El <u>Capítulo 2</u> se centra en el bus de potencia regulado de los satélites. Se aborda la posibilidad de replantear dicho subsistema a nivel de convertidor, con el objetivo de desarrollar una única topología válida para implementar los distintos bloques que lo forman. De esta forma, el tiempo de rediseño para cada misión se vería prácticamente eliminado. Finalmente, se planeta el uso de una etapa, llamada transformador electrónico, con el objetivo de independizar el bus de potencia principal, del panel solar utilizado, haciendo un escalado de los distintos niveles de tensión y potencia, desde un punto de vista modular.

El Capítulo 3 aborda el análisis y diseño de la etapa transformador electrónico, desde un punto de vista modular. Dicha etapa estará formada por varios convertidores CC/CC, que, a través de la conexión en serie o paralelo de sus entradas, se encargarán de adaptar los niveles de tensión y potencia, en función del panel solar empleado. En primer lugar, se hará una breve descripción de la topología seleccionada en base al cumplimiento de los requisitos impuestos. A continuación, se analizará el modo de operación modular empleando el transformador electrónico. Este análisis se complementará con simulaciones У resultados experimentales aue validan funcionamiento modular propuesto.

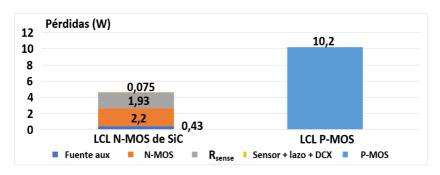

El <u>Capítulo 4</u> se centra en el sistema de distribución del satélite, planteando un diseño de un limitador de corriente de enclavamiento. Estos dispositivos se encargan de proteger al bus de potencia principal frente a sobrecorrientes. Las arquitecturas tradicionales están basadas en semiconductores P-MOS, lo cuales, debido a sus elevados valores de resistencias de canal, presentan altas pérdidas de conducción ante niveles de corriente elevados. De esta forma, este capítulo presenta el análisis y diseño de una arquitectura de LCL basada en el uso de semiconductores N-MOS de SiC como dispositivo limitador de corriente. Se analizarán las distintas partes que forman esta nueva arquitectura, junto con una guía de diseño de aquellas más complejas. Finalmente, se mostrarán resultados experimentales que validan el funcionamiento de la topología planteada.

Finalmente, en el <u>Capítulo 5</u> se presenta un resumen de las conclusiones más relevantes de este trabajo, así como también líneas de investigación futuras en este contexto.

#### RESUMEN (en Inglés)

The objective of this work is to present solutions in order to make more efficient the main power bus and the distribution system on satellites. Due to the massive use of satellites nowadays, it is necessary to have main blacks that can be reuse in different space missions. This way, costs and developing times can be reduced.

This thesis begins with an introduction of the aerospace systems. Therefore, <u>Chapter 1</u> introduces the satellite concept from the system point of view, describing the main subsystems on it. In the same way, a brief historical introduction will be made regarding the increasing use of satellites and the rise of the power demanded by them. At the end of this chapter, the objectives and main contributions of this work will be displayed.

<u>Chapter 2</u> focuses in the regulated power bus on satellites. This chapter presents the idea of reconsidering the main power bus at converter level, with the objective of having only one topology which will be valid to implement the main building blocks of the power subsystem. This way, the developing times between missions will be reduced. Finally, this chapter presents the use of a stage called 'Electronic Transformer' (ET), making possible the independency of the main power bus from the solar array. The voltage and power levels adaptations will be made in a modular way.

<u>Chapter 3</u> addresses the analysis and design of the ET stage from the modular point of view. This stage will be composed by DC/DC converters connected in series or parallel at their inputs making possible to achieve a correct voltage and power sharing between modules depending on the solar array used. First, a description of the topology will be displayed. After that, a modular operation behaviour of all the modules connected in the ET stage will be explained. This

analysis will be complemented with simulation and experimental results for the implemented prototypes.

<u>Chapter 4</u> is focused on the satellite distribution system presenting a new design of a latching current limiter (LCL). These devices provide overcurrent protection for the main power bus. Traditional LCL architectures are based on P-MOS devices which, due to its higher on-state resistance values, they present high conduction losses at higher power. This way, this chapter presents an analysis and design of a LCL structure based on SiC N-MOS devices. The different stages that formed the SiC LCL architecture will be analysed, presenting a design guide for them. Finally, the experimental results of the prototypes develop using this new architecture will be displayed.

Finally, <u>Chapter 5</u> presents a summary and conclusions, as well as the proposal of future work related to this thesis.

SR. PRESIDENTE DE LA COMISIÓN ACADÉMICA DEL PROGRAMA DE DOCTORADO EN

### Resumen

El objetivo de este trabajo es proporcionar soluciones para hacer más eficientes tanto el bus de potencia principal, como el sistema de distribución, presentes en los satélites. Dada la proliferación y el uso masivo de satélites hoy en día, se hace necesario contar con implementaciones que permitan reutilizar ciertos bloques funcionales presentes en los mismos, entre las distintas misiones espaciales. De esta forma, se podrían reducir costes y tiempos de desarrollo.

Este trabajo de tesis comienza con una introducción a los sistemas en naves espaciales. De esta forma, en el <u>Capítulo 1</u> se introducirá el concepto de satélite, dese el punto de vista de sistema, así como también se describirán los principales subsistemas que lo forman. De igual forma, se hará una breve introducción histórica sobre el uso de los satélites, así como también sobre la continua y creciente evolución en su uso y en su demando de potencia. En la parte final de este capítulo se detallan los objetivos y contribuciones originales de este trabajo.

El <u>Capítulo 2</u> se centra en el bus de potencia regulado de los satélites. Se aborda la posibilidad de replantear dicho subsistema a nivel de convertidor, con el objetivo de desarrollar una única topología válida para implementar los distintos bloques que lo forman. De esta forma, el tiempo de rediseño para cada misión se vería prácticamente eliminado. Finalmente, se planeta el uso de una etapa, llamada transformador electrónico, con el objetivo de independizar el bus de potencia principal, del panel solar utilizado, haciendo un escalado de los distintos niveles de tensión y potencia, desde un punto de vista modular.

El <u>Capítulo 3</u> aborda el análisis y diseño de la etapa transformador electrónico, desde un punto de vista modular. Dicha etapa estará formada por varios convertidores CC/CC, que, a través de la conexión

en serie o paralelo de sus entradas, se encargarán de adaptar los niveles de tensión y potencia, en función del panel solar empleado. En primer lugar, se hará una breve descripción de la topología seleccionada en base al cumplimiento de los requisitos impuestos. A continuación, se analizará el modo de operación modular empleando el transformador electrónico. Este análisis se complementará con simulaciones y resultados experimentales que validan el funcionamiento modular propuesto.

El <u>Capítulo 4</u> se centra en el sistema de distribución del satélite, planteando un diseño de un limitador de corriente de enclavamiento. Estos dispositivos se encargan de proteger al bus de potencia principal frente a sobrecorrientes. Las arquitecturas tradicionales están basadas en semiconductores P-MOS, lo cuales, debido a sus elevados valores de resistencias de canal, presentan altas pérdidas de conducción ante niveles de corriente elevados. De esta forma, este capítulo presenta el análisis y diseño de una arquitectura de LCL basada en el uso de semiconductores N-MOS de SiC como dispositivo limitador de corriente. Se analizarán las distintas partes que forman esta nueva arquitectura, junto con una guía de diseño de aquellas más complejas. Finalmente, se mostrarán resultados experimentales que validan el funcionamiento de la topología planteada.

Finalmente, en el <u>Capítulo 5</u> se presenta un resumen de las conclusiones más relevantes de este trabajo, así como también líneas de investigación futuras en este contexto.

# **Agradecimientos**

En primer lugar, quiero agradecer a mis directores de tesis Manuel Arias y Pablo Fernández, verdaderos autores de este trabajo, por la ayuda, dedicación y paciencia a lo largo de estos cuatro años de tesis. De la misma manera, quiero agradecer al profesor José A. Villarejo su trabajo, revisando íntegramente capítulos de este documento.

En segundo lugar, quiero tener un recuerdo para los distintos profesores que forman el grupo SEA, Javier, Marta, Aitor, Diego, Alberto, Juan, etc, por haber aprendido cosas escuchándolos, y por los buenos momentos en el laboratorio, comidas, paseos, congresos, etc. Gracias también al resto de integrantes del SEA, doctorandos pasados y presentes por los buenos momentos en el día a día del trabajo en el laboratorio, y muy especialmente al clásico grupo de las comidas formado por Miguel, Tania, Juan Ramón, Theyllor, y un servidor, por los disparatados diálogos que allí se creaban.

En tercer lugar, a muchos de los compañeros de la carrera/instituto con los que he seguido en contacto y que me han seguido animando con este trabajo, muy especialmente a Isa, Vanesa, Carlos, Marcos, Alberto, Santi, Paula, Cañón, Ainoa, Aida, Bárbara y, seguramente más a los que me dejaré. Dentro de este apartado quiero agradecer también a Andrea sus correos, sus ánimos, visitas y conversaciones a lo largo de este tiempo, en el que yo hacía algo llamado "tesis" y ella hacía su vida entre Alemania, España e Irlanda.

Finalmente, mis últimos agradecimientos son para mi padre y mi madre por su cariño, apoyo, trabajo y sacrificio constante durante todos estos años.

# Índice de contenidos

#### Capítulo 1: Introducción a los sistemas embarcados en satélites 9

- 1.1.- Introducción 18

- 1.2.- Subsistemas del satélite 21

- 1.2.1.- Subsistema de procesamiento de datos y telemetría 21

- 1.2.2.- Subsistema de control de órbita y orientación 22

- 1.2.3.- Subsistema de potencia 23

- 1.2.4.- Subsistema de control térmico 27

- 1.2.5.- Subsistema de propulsión 28

- 1.3.- Evolución en el uso de los satélites 29

- 1.3.1.- Paradigma "new space" 30

- 1.4.- La creciente demanda de potencia en las naves espaciales 33

- 1.4.1.- Problemática y motivación 34

- 1.5.- Objetivos y contribuciones originales de este trabajo 36

- 1.6.- Bibliografía 37

#### Capítulo 2: Estandarización del bus de potencia en satélites 45

- 2.1.- Motivación 46

- 2.2.- Requisitos empleados en la selección y comparativa de topologías modulares 46

- 2.2.1.- Análisis de la fiabilidad 47

- 2.2.2.- Selección de componentes 52

- 2.3.- Posibles topologías básicas 63

- 2.4.- Estandarización basada en etapa intermedia 69

- 2.5.- Conclusiones 71

- 2.6.- Bibliografía 72

#### Capítulo 3: El transformador electrónico 73

- 3.1.- Introducción 74

- 3.2.- Descripción del concepto de transformador electrónico 77

- 3.3.- El módulo DCX del TE 80

- 3.3.1.- Descripción de la topología seleccionada y cumplimiento de las condiciones impuestas 81

- 3.3.2.- Operación modular 91

- 3.3.3.- Análisis de la fiabilidad 99

- 3.3.4.- Análisis de las tolerancias y del envejecimiento en los componentes resonantes 102

- 3.4.- Resultados experimentales de la etapa TE usando los módulos DCX 106

- 3.4.1.- Resultados experimentales para un solo módulo DCX 107

- 3.4.2.- Resultados experimentales con varios módulos DCX conectados en IPOP e ISOP 112

- 3.4.3.- Efecto de fallo en un módulo DCX dentro del sistema TE 117

- 3.4.4.- Emulación de panel solar a través del transformador electrónico 120

- 3.5.- Conclusiones 122

- 3.6.- Bibliografía 138

# Capítulo 4: Diseño de un limitador de corriente de enclavamiento basado en N-MOS de SiC 141

- 4.1.- Introducción 142

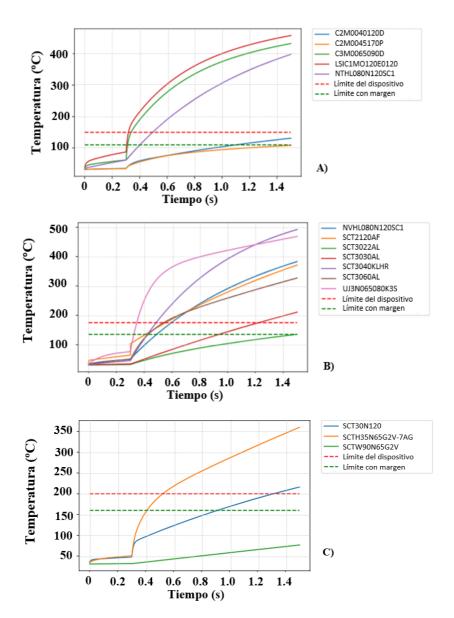

- 4.2.- Selección de semiconductores 146

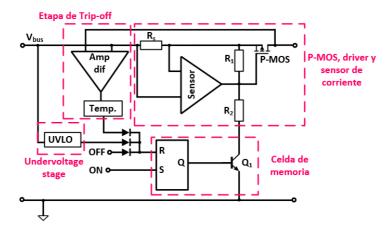

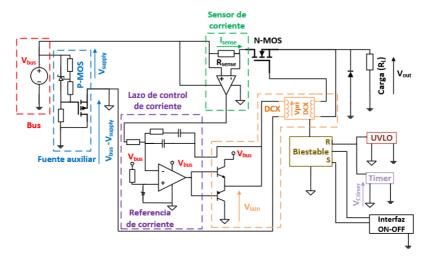

- 4.3.- Arquitectura del LCL basado en N-MOS de SiC 159

- 4.3.1.- Fuente de alimentación auxiliar 160

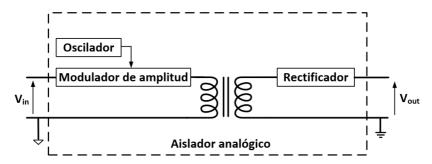

- 4.3.2.- Aislador analógico (DCX) 161

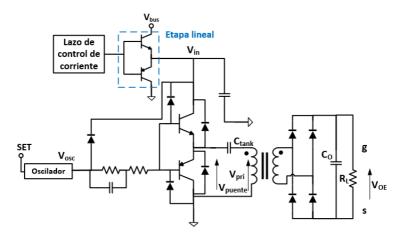

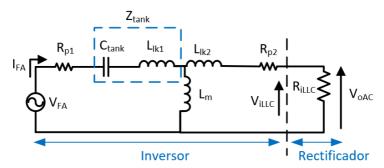

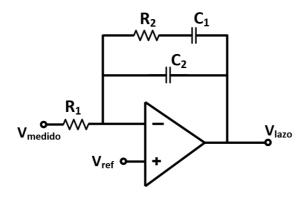

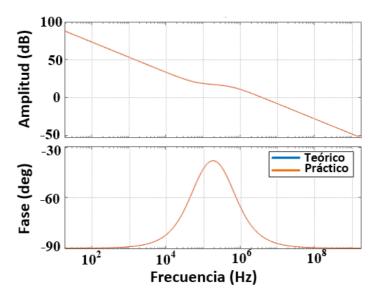

- 4.3.3.- Lazo de control de corriente 171

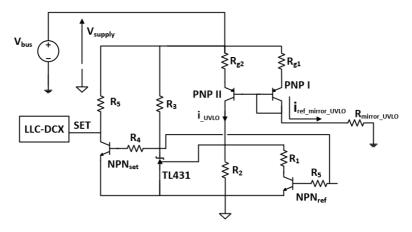

- 4.3.4.- Sección de protección contra infratensión (UVLO) 180

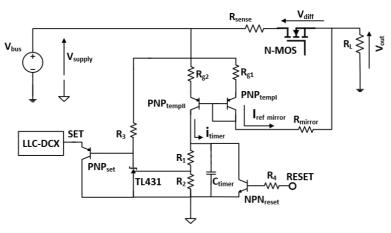

- 4.3.5.- Sección de temporización 182

- 4.3.6.- Sección de arranque suave 184

- 4.4.- Resultados experimentales 185

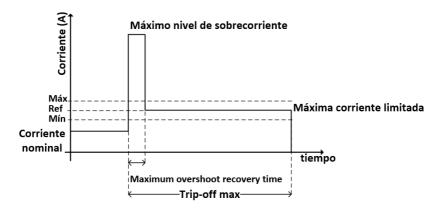

- 4.4.1.- Funcionamiento del LCL con cortocircuito a su salida 186

- 4.4.2.- Funcionamiento del LCL activándose desde cortocircuito 188

- 4.4.3.- Funcionamiento del LCL variando su impedancia de salida 190

- 4.4.4.- Proceso de carga de un condensador a través del LCL 192

- 4.4.5.- Análisis de las pérdidas en el LCL basado en N-MOS de SiC 193

- 4.5.- Conclusiones 194

- 4.6.- Bibliografía 195

#### Capítulo 5: Conclusiones y trabajo futuro 199

- 5.1.- Conclusiones 200

- 5.2.- Trabajo futuro 203

- 5.3.- Contribuciones 204

- 5.4.- Publicaciones 205

- 5.4.1.- Publicaciones en revista internacional: 206

- 5.4.2.- Publicaciones en congreso internacional: 206

- 5.4.3.- Publicaciones en congreso nacional: 207

- 5.5.- Financiación 208

#### Lista de símbolos 209

- Capítulo 2: 209

- Capítulo 3: 211

- Capítulo 4: 214

#### Lista de acrónimos 219

- Capítulo 1: 219

- Capítulo 2: 220

- Capítulo 3: 220

- Capítulo 4: 221

# Índice de figuras

- Fig.1. 1. Subsistemas del satélite según [1.1] 20

- Fig.1.2. Esquema básico del bus de potencia no regulado de un satélite 24

- Fig.1.3. Esquema básico de un sistema de potencia regulado en un satélite 26

- Fig.1.4. Número de satélites lanzados entre 1957 y 2019 [1.19] 30

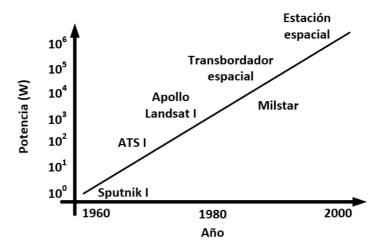

- Fig.1.5 Crecimiento en los requisitos de potencia de las navas espaciales entre la década de los 60 y los 2000 [1.18] 33

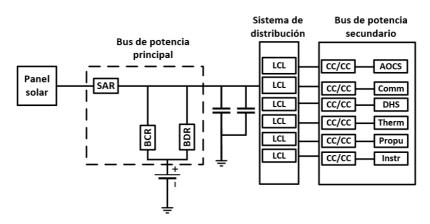

- Fig.2. 1. Esquema del bus de potencia regulado de un satélite 47

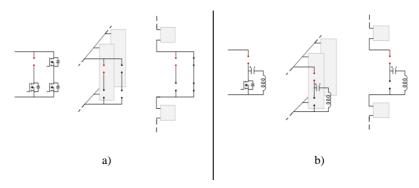

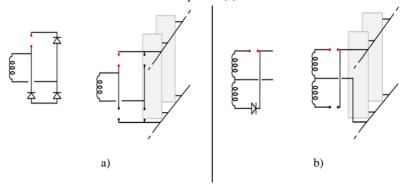

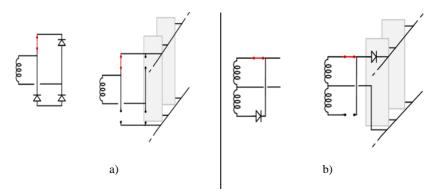

- Fig.2.2. Posibles casos de FCA en configuraciones puente completo (a) y medio puente (b) 51

- Fig.2.3. Posibles casos de FCC en configuraciones puente completo (a) y medio puente (b) 51

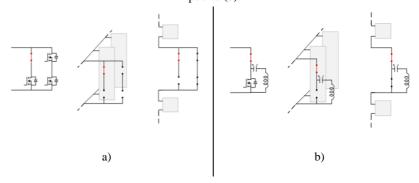

- Fig.2.4. Posibles casos de FCA en configuraciones rectificador de doble onda (a) y rectificador con toma media (b) 51

- Fig.2.5. Posibles casos de FCC en configuraciones rectificador de doble onda (a) y rectificador con toma media (b) 52

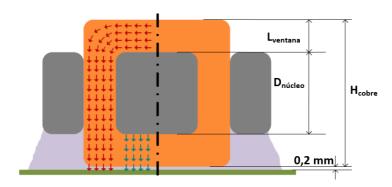

- Fig.2.6. Modelo térmico simplificado de la transferencia de calor para pérdidas en el cobre 59

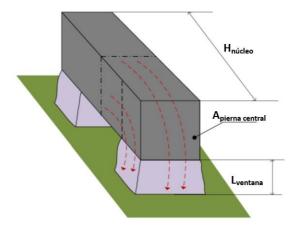

- Fig.2.7. Modelo térmico simplificado de la transferencia de calor para pérdidas en el núcleo 60

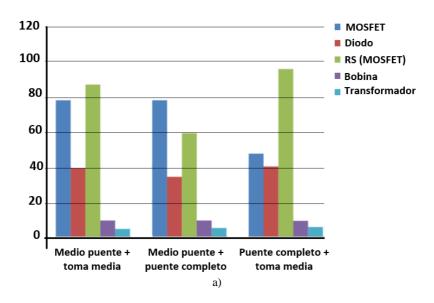

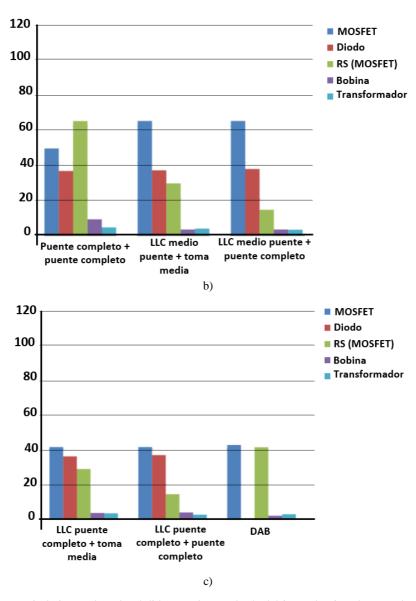

- Fig.2.8. Desglose de pérdidas para las topologías básicas seleccionadas, para la implementación del bloque SAR. Se considera redundancia 3+1 67

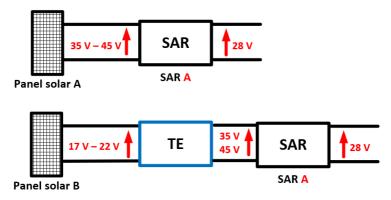

- Fig. 3.1. Ejemplo de reutilización del bloque SAR usando el TE como etapa intermedia 76

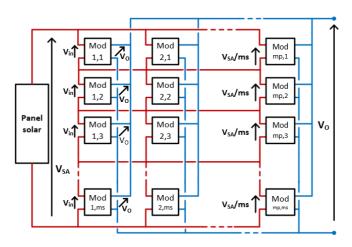

- Fig. 3.2. Esquema del método de adaptación de tensiones / potencias a través de la conexión de varios módulos diseñados con ganancia estática fija 79

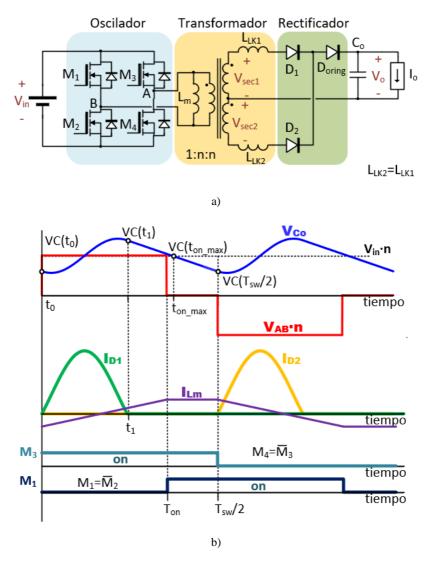

- Fig. 3.3 a) Representación del esquemático del módulo TE; b) Principales formas de onda de la topología del TE 83

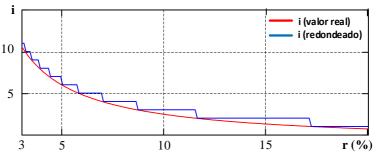

- Fig.3.4. Ángulo de conducción de los diodos en función de la ratio entre la frecuencia de resonancia y la frecuencia de conmutación. Solución numérica para la ecuación (3.10) 87

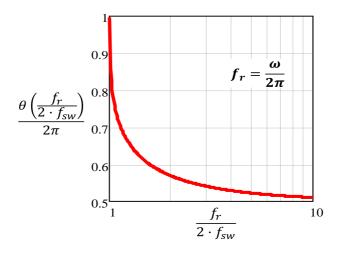

- Fig.3.5. Situación de las corrientes resonantes cuando a)  $T_{on} > T_{on\_max} y$  b)  $T_{on} = T_{on\_max} 89$

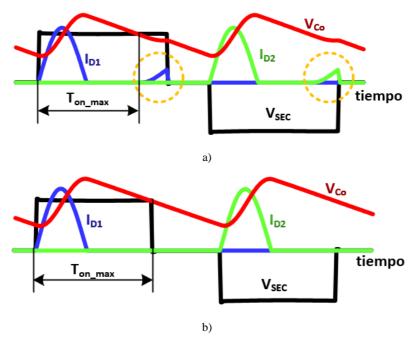

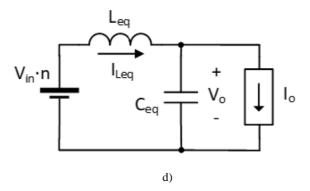

- Fig.3.6. a) Circuito simplificado de dos módulos conectados en IPOP; b) Circuito resonante equivalente; c) "n" módulos conectados en IPOP; d) circuito resonante equivalente para "n" módulos 94

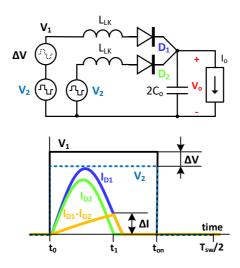

- Fig.3.7. Circuito y formas de onda para mostrar el comportamiento de las corrientes resonantes ante diferencias en los niveles de tensión en cada módulo 96

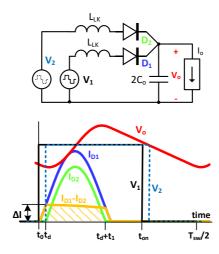

- Fig.3.8. Circuito y principales formas de onda ante errores de sincronización 97

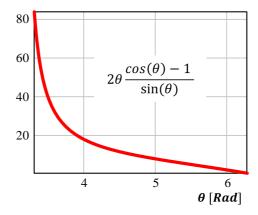

- Fig.3.9. Incremento en la variación de corriente debido a errores de sincronización en función del ángulo  $\theta$  99

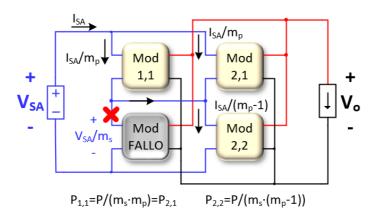

- Fig.3.10. Reparto de tensiones y corrientes en una matriz de cuatro módulos DCX cuando uno de ellos falla 102

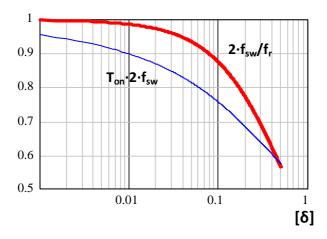

- Fig.3.11. Representación de la frecuencia de conmutación normalizada (rojo) y del valor de  $T_{on}$  normalizado (azul) en función de la tolerancia ( $\delta$ ) 105

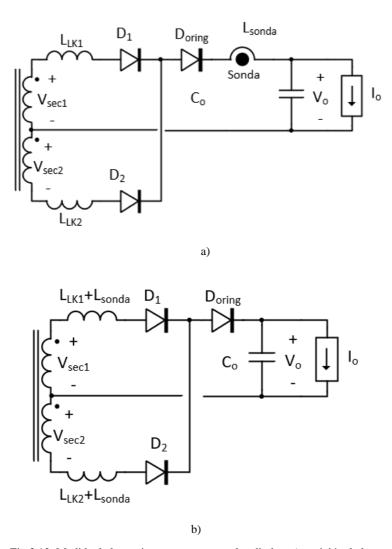

- Fig.3.12. Medida de la corriente resonantes en los diodos, a) posición de la sonda de corriente; b) Circuito equivalente considerado 108

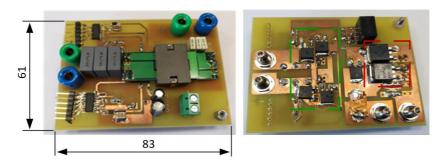

- Fig.3.13. Prototipo del módulo DCX construido 111

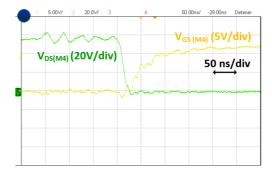

- Fig.3.14. Transición en la tensión drenador-fuente ( $V_{DS}$ ), y puertafuente ( $V_{GS}$ ) del transistor  $M_4$  donde se muestra la conmutación a tensión cero (ZVS) 111

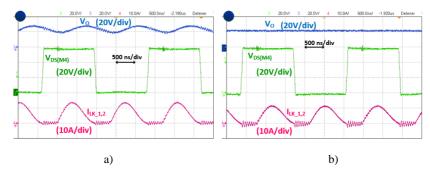

- Fig.3.15. Representación de la tensión drenador-fuente en el transistor  $M_4$  ( $V_{DSM4}$ ), de la corriente resonante ( $I_{LK}$ ), y de la tensión de salida ( $V_O$ ) cuando a) no se considera filtro EMI a la entrada del SAR; b) sí se considera filtro EMI en el SAR 111

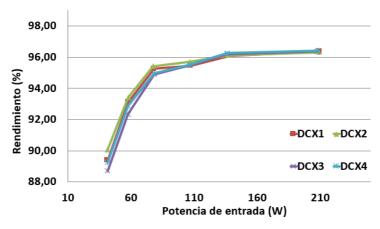

- Fig.3.16. Comparativa de los rendimientos obtenidos para los distintos módulos DCX 112

- Fig.3.17, Tensión de salida ( $V_O$ ) y corrientes resonantes ( $I_{LK1,2}$ ) en dos módulos DCX conectados en IPOP 115

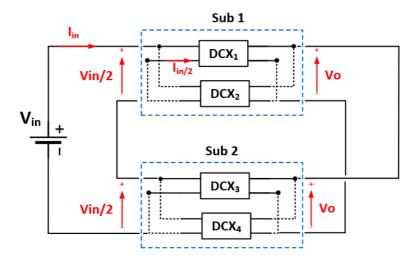

- Fig.3.18. Esquema de dos subsistemas (Sub 1 y Sub 2), de módulos DCX conectados en IPOP, conectados en ISOP 115

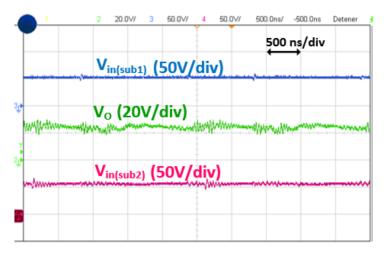

- Fig.3.19. Tensión de entrada en Sub 1 y Sub2, junto con el nivel de tensión de salida del sistema completo (V<sub>0</sub>) 116

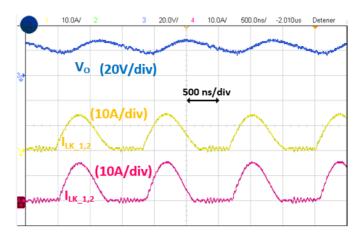

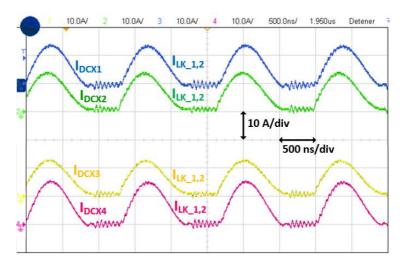

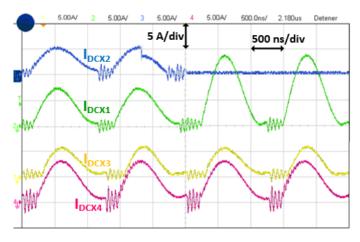

- Fig.3.20. Corrientes resonantes a través de los diodos rectificadores de los cuatro módulos DCX. La potencia procesada por cada módulo es de 200 W 116

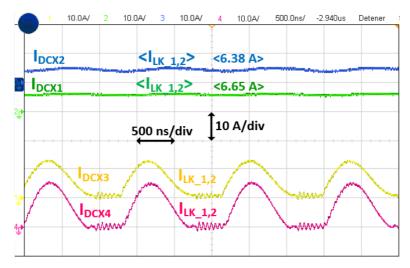

- Fig.3 21. Valor medio de la corriente resonante en los módulos DCX<sub>1</sub> y DCX<sub>2</sub>, y corrientes resonantes en los módulos DCX<sub>3</sub> y DCX<sub>4</sub> 117

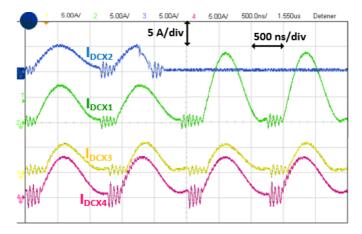

- Fig.3.22. Corrientes resonantes a través de los diodos rectificadores. El fallo en el módulo  $DCX_2$  se debe a un cortocircuito en el transistor  $M_3$  119

- Fig.3.23. Corrientes resonantes a través de los diodos rectificadores. El fallo en el módulo DCX<sub>2</sub> se debe a que M<sub>2</sub> y M<sub>3</sub> se mantienen siempre en circuito abierto 119

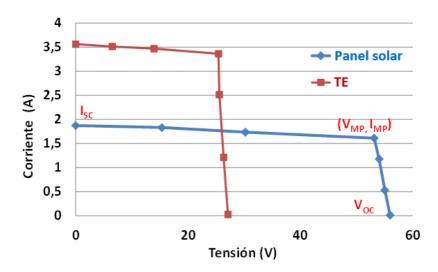

- Fig.3.24. Curvas I-V del panel solar emulado y del transformador electrónico (TE) 121

- Fig.4.1. Esquema del bus de potencia regulado de un satélite 143

- Fig.4.2. Arquitectura tradicional de un LCL basado en P-MOS 144

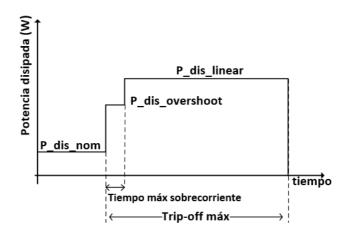

- Fig.4.3. Perfil de corriente en el LCL ante cortocircuito a la salida 151

- Fig.4.4. Perfil de la potencia disipada por el semiconductor ante cortocircuito a la salida del LCL 151

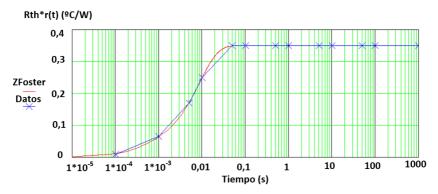

- Fig.4. 5. Respuesta térmica transitoria del modelo de Foster para el MOSFET SCT3022AL, junto con la respuesta térmica transitoria real según sus hojas de características 153

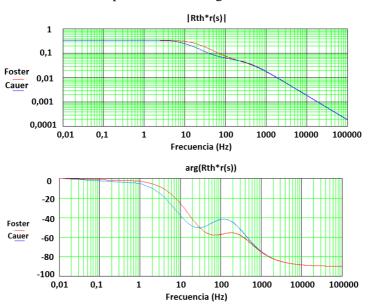

- Fig.4.6. Respuesta en frecuencia de los modelos de Foster y Cauer para el SCT3022AL 155

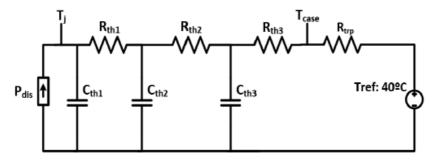

- Fig.4.7. Red de Cauer con resistencia  $R_{trp}$  extra 157

- Fig.4. 8. Respuesta térmica a) 150°C, b) 175°C y c) 200°C 158

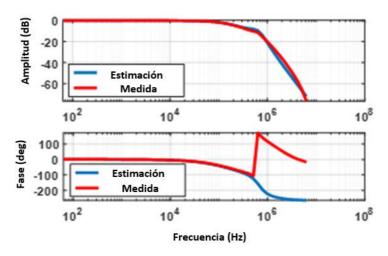

- Fig.4.9. Arquitectura del LCL basada en dispositivo N-MOS 160

- Fig.4.10. Concepto de aislador analógico 161

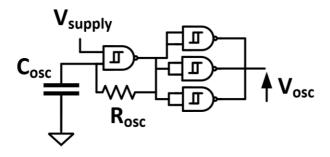

- Fig.4. 11. Implementación del oscilador en la etapa DCX 164

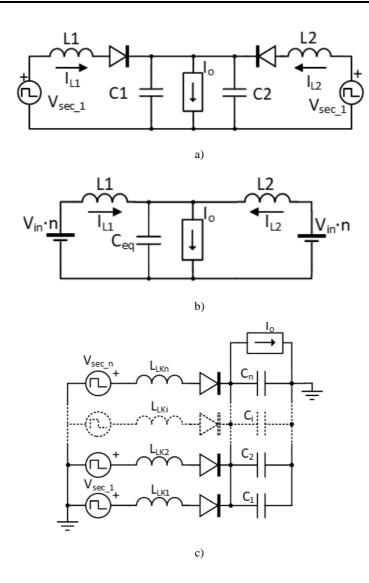

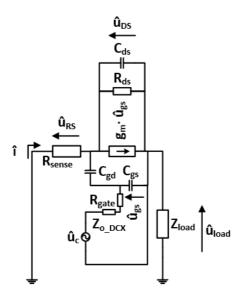

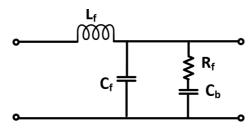

- Fig.4.12. Representación del esquemático del LLC 165

- Fig.4.13. Circuito equivalente para la topología LLC-DCX usando la FHA 165

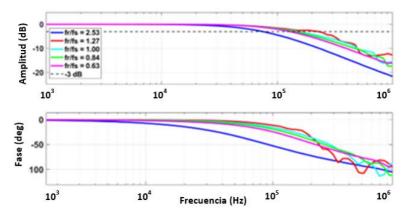

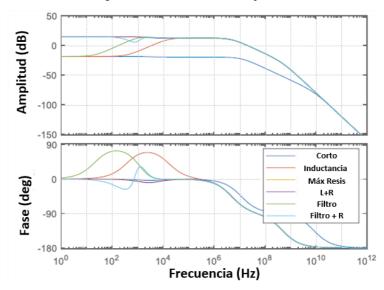

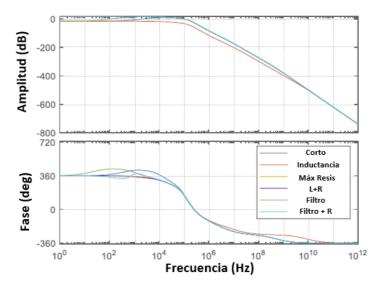

- Fig.4.14. Diagramas de Bode para un valor de  $Q_{tank}$  fijo de 0,1818 variando la ratio  $F_R/F_{SW}$  170

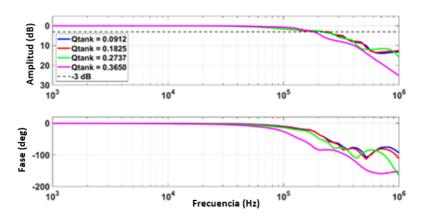

- Fig.4.15. Diagramas de Bode para un valor de la ratio  $F_R/F_{SW}$  fijo de 1,27 variando el parámetro  $Q_{tank}$  171

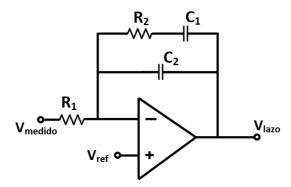

- Fig.4.16. Implementación práctica de un regulador tipo II con un amplificador operacional 172

- Fig.4.17. Audio-susceptibilidad de la etapa LLC-DCX para una  $V_{\rm in}$  de 10 V 175

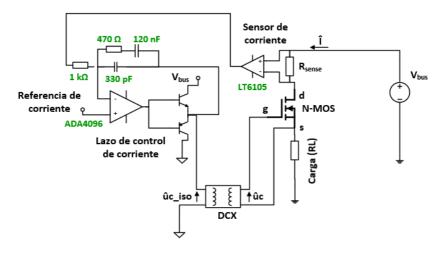

- Fig.4.18. Circuito equivalente del LCL en el modelo de pequeña señal 175

- Fig.4.19. Circuito de pequeña señal entre la salida de la etapa DCX y el dispositivo N-MOS 176

- Fig.4.20. Diseño del filtro LC implementado 177

- Fig.4.21. Diagramas de Bode la función de transferencia  $G_{i\_uc}$  para diferentes configuraciones de  $Z_{load}$  177

- Fig.4.22. Diagramas de Bode la función de transferencia  $G_{LCL}$  para diferentes configuraciones de  $Z_{load}$  178

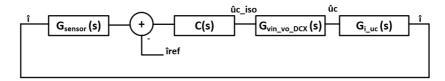

- Fig.4. 23. Diagrama de bloques del lazo de control implementado 179

- Fig.4.24. Comparativa de los diagramas de Bode del regulador implementado a nivel teórico y práctico 180

- Fig.4.25. Implementación del circuito de undervoltage 181

- Fig.4.26. Implementación del circuito de temporización 183

- Fig.4.27. Implementación del circuito de arranque suave (en rojo) en la referencia de corriente del lazo de control 185

- Fig.4.28. Prototipo del LCL diseñado, a) capa *top*, b) capa *bottom* 186

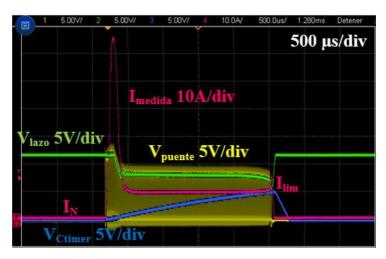

- Fig.4.29. Principales formas de onda del funcionamiento del LCL clase 10 ante cortocircuito a su salida, para una V<sub>bus</sub> de 100 V 187

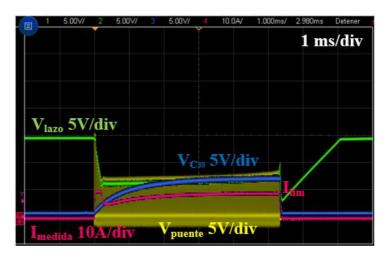

- Fig.4.30. Activación del LCL directamente desde cortocircuito para una  $V_{\text{bus}}$  de 100 V 189

- Fig.4.31. Activación del LCL directamente desde cortocircuito para una  $V_{bus}$  de 100 V, usando el circuito de arranque suave 189

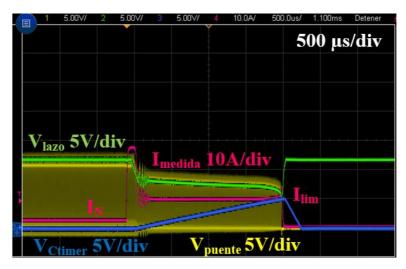

- Fig.4.32. Funcionamiento del LCL, ante cortocircuito a su saluda, usando un filtro LC entre el LCL y la carga, para una  $V_{bus}$  de 100 V y empleado el N-MOS de ROHM 191

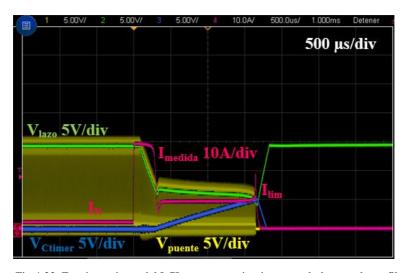

- Fig.4.33. Funcionamiento del LCL, ante cortocircuito a su saluda, usando un filtro LC entre el LCL y la carga, para una  $V_{bus}$  de 100~V y empleado el N-MOS de ST 191

- Fig.4.34. Proceso de carga de un condensador conectado entre el LCL y la carga, para una  $V_{bus}$  de  $100\ V\ 192$

- Fig.4.35. Desglose de pérdidas para la arquitectura propuesta de LCL basada en N-MOS de SiC, en comparación con un P-MOS calificado para espacio, para un LCL clase 10 y con una V<sub>bus</sub> de 100 V 194

# Índice de tablas

- Tabla 2.1. Principales requisitos eléctricos del bus de potencia 64

- Tabla 2.2. Comparativa de rendimientos entre las topologías básicas seleccionadas 68

- Tabla 3. 1. Parámetros principales de diseño del módulo DCX 110

- Tabla 3. 2. Principales características del panel solar emulado 121

- Tabla 4. 1. Clases de LCLs con sus principales características para tensión de bus de: a) 28 V y b) 50 V [4.1] 148

- Tabla 4. 2. Coeficientes del modelo de Foster para el MOSFET SCT3022AL 153

- Tabla 4.3. Coeficientes del modelo de Cauer para el MOSFET SCT3022AL 155

# Capítulo 1: Introducción a los sistemas embarcados en satélites

En este capítulo se hace una breve introducción del contexto histórico y la evolución de los subsistemas de potencia en satélites. En primer lugar, se proporcionará una definición del satélite, desde el punto de vista de sistema, para posteriormente describir los distintos subsistemas que lo forman.

En primer lugar, se exponen las principales características de estos subsistemas. Hoy en día, se ha llevado a cabo un incremento en la puesta en órbita de satélites, para distintas aplicaciones, meteorología, telecomunicaciones, investigación científica, observación, etc. Este hecho se ha visto especialmente reforzado por el incremento en el número de empresas privadas que apuestas por la investigación y el desarrollo de sistemas espaciales. Sin embargo, el proceso de diseño de los satélites sigue realizándose con poco reaprovechamiento de diseños previos, y partiendo prácticamente desde cero. En este sentido, se plantea en este trabajo la necesidad de introducir los conceptos de reusabilidad y estandarización en los diseños de los satélites.

Finalmente, se describen los objetivos y las principales contribuciones de este trabajo.

# 1.1.- Introducción

Desde el comienzo de la llamada "Era Espacial", las aplicaciones basadas en el uso de satélites se han convertido en un aspecto preponderante y crítico, año tras año. Además de los tradicionales satélites pensados para aplicaciones de telecomunicación, meteorología, e investigación científica, otras aplicaciones como la navegación o la observación terrestre, empiezan a ganar más relevancia e interés. Por ejemplo, la Comisión Europea está financiando el llamado "programa Copérnico" con el objetivo de poder tomar distintas medidas de observación terrestre, de forma continua. Su objetivo es el de proporcionar datos, en relación con medidas atmosféricas, cambio climático, uso de los suelos terrestres, medio ambiento marino, respuesta a emergencias, así como también aspectos relacionados con la seguridad. Para poder llevar a cabo estos objetivos, se ha desarrollado una flota de satélites, dentro de la llamada serie "Sentinel".

Desde el punto de vista de la navegación, la Comisión Europea se encuentra desarrollando el sistema Galileo, como alternativa al, mundialmente conocido, sistema GPS. Además de estos aspectos, hoy en día hay números campos de desarrollos, cuya expansión está resultando muy llamativa, gracias a la existencia de los satélites. Estos campos guardan relación con la observación y la exploración del espacio exterior, y de otros planetas.

En lo que respecta a la financiación, los satélites no se encuentran financiados, en la actualidad, solo a través de agencias gubernamentales o intergubernamentales como la Administración Nacional de Aeronáutica y el Espacio (NASA) o la Agencia Espacial Europea (ESA), sino que existen operadores privados de satélites como la Sociedad Europea de Satélites (SES) o Hispasat. Además, también existen compañías privadas que se dedican a la fabricación de satélites como pueden ser *Airbus*, *Thales Alenia Space* u OHB. En

este caso, se trata de compañías europeas con importantes relaciones y presencia en la industria española. Por ejemplo, CRISA, perteneciente a la sección de defensa y espacio de Airbus, es el proveedor de las "unidades de conversión de potencia y distribución" (PCDU) de satélites para usos comerciales y gubernamentales.

A continuación, se hará una definición del satélite, desde el punto de vista de sistema, y se detallarán los principales subsistemas que forman parte de este.

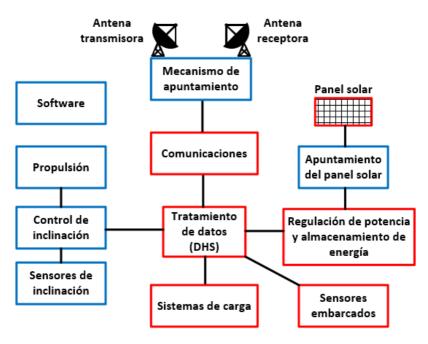

Un satélite consiste en varios sistemas diseñados para cumplir con los requisitos de una determinada misión. Todos, incluyendo los satélites más sencillos, cuentan con una serie de sistemas comunes, representados en rojo en la Fig.1. 1 [1.1]. Los satélites más complejos requieren sistemas adicionales, como los representados en azul en la Fig.1. 1. Estos sistemas se dividen en dos grandes grupos: los subsistemas de carga útil, y los de plataforma. Dentro de los subsistemas de carga útil, estarían aquellos relacionados con los equipos de comunicaciones, en los satélites comerciales, o la instrumentación de toma de medidas, en los satélites destinados a la investigación. En definitiva, aquellos que realizan la tarea o tareas propias de la misión. Por su parte, los llamados subsistemas de plataforma englobarían aquellos encargados de dar soporte a los subsistemas de carga útil. Es decir, los encargados de que el satélite sea operativo, de manera autónoma, y pueda desempeñar las tareas asociadas a la misión.

El subsistema de potencia sería uno de los sistemas de plataforma, el cual está formado por el conjunto de paneles solares, baterías, electrónica de potencia, cableado y sistemas de control. Otros subsistemas importantes, dentro de los llamados subsistemas de plataforma, serían el subsistema de comunicaciones, encargado de recibir comandos y devolver información, los subsistemas de telemetría, así como también. los subsistemas de coordinación y control de actividades del satélite. Hoy en días, incluso los satélites

más sencillos, suelen contar, además, con subsistemas encargados de determinar, la orientación dentro de la órbita, la propulsión, etc. De esta manera, el diseño de un satélite, siempre se encuentra optimizado al máximo, de modo que cualquier cambio resultaría en un coste muy elevado.

Fig.1. 1. Subsistemas del satélite según [1.1]

### 1.2.- Subsistemas del satélite

En esta sección se describen los distintos subsistemas que componen la plataforma de los satélites más habituales [1.1]:

# 1.2.1.- Subsistema de procesamiento de datos y telemetría

Una de las funciones básicas de las naves espaciales, incluso de las más simples, se basa en mantener el contacto con las estaciones de tierra, con el objetivo de llevar a cabo tareas de control, operaciones de comunicación, retorno de los datos, etc.

En este sentido, el subsistema de tratamiento de datos (*Command and Data Handling Subystem*, CDHS) se encarga de llevar a cabo el envío y la recepción de los datos en la nave espacial [1.2], [1.3]. En este caso, estarían incluidos los datos derivados de las operaciones científicas, así como también las operaciones derivadas de la carga de pago. En este caso, se trata de un subsistema de control de la información bidireccional, es decir se encarga de la recepción y demodulación de la información desde la estación de tierra al satélite, así como también de la transmisión, en tiempo real, desde el satélite hasta la estación de tierra.

Este subsistema está conectado a sendas unidades, transmisora y receptora de radiofrecuencia, que constituyen los puntos únicos de entrada o salida de datos en la nave espacial. Desde el punto de vista de la comunicación, se puede pensar en un enlace espacial, como un enlace de comunicaciones entre una nave espacial, y las estaciones de tierra, o un enlace de comunicaciones entre dos naves espaciales. De la misma manera, se puede definir al protocolo de enlace espacial como aquel protocolo de comunicaciones diseñado para ser usado sobre un enlace espacial, o en una red que contine uno o muchos enlaces espaciales. La información básica en un enlace espacial se

basa en datos de telemetría y telecomando. De esta manera, el enlace descendente de telemetría y el enlace ascendente de telecomando proporcionan el canal de comunicaciones, necesario, entre la nave espacial, y las estaciones de tierra.

En el enlace ascendente, el CDHS recibe y decodifica los datos y telecomandos de las operaciones, tanto de los sistemas de carga útil, como los de plataforma. Estos telecomandos serán dirigidos, posteriormente, a cada uno de los subsistemas o ejecutados directamente a nivel de plataforma.

Por su parte, en el enlace descendente, el CDHS toma varios tipos de datos adquiridos de los subsistemas que forman la plataforma, o generados por cargas de pago científicas. Estos datos, serán multiplexados y convertidos a tramas de datos, para su posterior transmisión a las estaciones de tierra.

# 1.2.2.- Subsistema de control de órbita y orientación

El subsistema de control de órbita y orientación (*Attitude and Orbit Control Subsystem*, AOCS) es el encargado de determinar la posición exacta del satélite respecto a su vertical, proporcionando apuntamiento preciso para las antenas de comunicaciones y para los sensores [1.4], [1.5].

El ámbito de trayectoria del satélite está determinado por el lanzador, encargado de ponerlo en órbita, y previamente definido en el proceso de fabricación del mismo. A continuación, el lazo de control a bordo del satélite se encarga de establecer y marcar la dirección y la orientación dentro de su órbita.

El principal inconveniente viene en que la orientación de los satélites puede verse afectada de numeras formas tanto desde el punto de vista de resistencia aerodinámica de las capas más exteriores de la atmósfera terrestre, la influencia de la gravedad, la radiación solar o la propia interacción entre el campo magnético terrestre y los dipolos magnéticos presentes en el satélite. Este nivel de orientación puede verse afectado también por factores internos derivados de posibles vibraciones en el propio satélite.

Estas perturbaciones, debidas a fuerzas internas y externas al satélite, deben ser contrarrestadas por el AOCS. Este subsistema incluye sensores para identificar el nivel de orientación (como giroscopios, sensores solares, magnetómetros o rastreadores de estrellas) y sistemas de puesta en marcha (como lanzadores, volantes de reacción, o pares magnéticos) para controlar las rotaciones del satélite alrededor de su centro de masas.

### 1.2.3.- Subsistema de potencia

El subsistema de potencia se encarga de generar, almacenar, controlar y distribuir la potencia con el nivel de tensión adecuado para todos los equipos y cargas conectados al satélite [1.6].

#### 1.2.3.1.- Subsistema de potencia no regulado

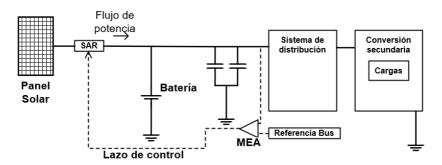

La Fig.1.2 muestra el esquema de bus de potencia no regulado, también conocido como bus de batería o bus regulado en iluminación solar. Las fuentes de energía serían el panel solar y la batería. De esta forma, sería la propia batería la que se encarga de alimentar las cargas, cuando el panel solar no sea capaz de proporcionar la suficiente potencia. A su vez, existe una conversión secundaria, por parte de las cargas, en la que se adapta el nivel de tensión proporcionado por la batería, a las necesidades de cada una de estas.

Desde el punto de vista del panel solar, cuando este sea capaz de proporcionar la potencia suficiente, será el llamado regulador de panel solar (*Solar Array Regulator* – SAR), el que se encargue de extraer la potencia de dicho panel, con el objetivo de alimentar las cargas, y de cargar la batería.

De este proceso de regulación se encarga el amplificador de error principal (*Mean Error Amplifier* – MEA). Esto proceso se basa en medir la tensión de la batería con el objetivo de saber cuánta potencia ha de inyectar el SAR, con el objetivo de mantener la batería cargada. En este caso, los valores típicos de tensión en las baterías estarán entre 24 V y 32 V.

Fig.1.2. Esquema básico del bus de potencia no regulado de un satélite

#### 1.2.3.2.- Subsistema de potencia regulado

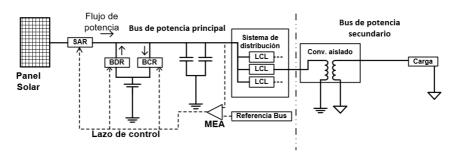

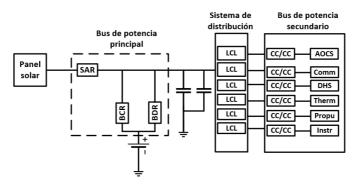

En la actualidad, el subsistema de potencia regulado, típico en los satélites, como el representado en la Fig.1.3, está formado por tres bloques: el SAR, el regulador de carga de batería (*Battery Charge Regulator* - BCR) y el regulador de descarga de batería (*Battery Discharge Regulator* - BDR) [1.1]. El SAR, se mantiene como el bloque encargado de extraer la energía del panel solar, mientras que el BCR y el BDR se encargan de inyectar o extraer energía de las baterías en función del balance neto de potencias entre el panel solar y las cargas. Estos bloques (SAR, BCR y BDR) están basados en convertidores continua-continua con diferentes especificaciones de potencia y tensiones de entrada y salida, no solo entre sí, sino también cambiantes entre distintas misiones (i.e. satélites). Debido a esto, la solución actual se centra en tener tres topologías distintas, tanto en especificaciones como en topologías. En el caso de los bloques SAR y

BCR, típicamente se emplean topologías reductoras (*Buck* o *Superbuck*) [1.7], [1.8], mientas que el bloque BDR está basado en topologías elevadoras (*Superboost* o *Weinberg*) [1.9], [1.10].

A modo de resumen general del esquema representado en la Fig.1.3, el panel solar está conectado al bus principal, a través del bloque SAR. Este bloque extrae la energía del panel solar, alimentando al bus de potencia principal. Seguidamente, la batería almacena la energía cuando la potencia demandada por las cargas de pago es menor que la potencia proporcionada por el SAR. Para este propósito, se tienen dos módulos conectados en paralelo, uno de ellos es el BCR, que almacena energía en la batería, y el otro es el BDR, que se encarga de extraer la energía de la batería, proporcionándola al bus de potencia principal. Con el objetivo de mantener la tensión del bus constante, existe un lazo de control (MEA), que es quien dicta cuánta potencia ha de ser procesada por cada uno de estos módulos, en función de la situación de trabajo en la que se encuentren.

En este tipo de arquitecturas de bus reguladas, el nivel de tensión del bus dependerá de los distintos requisitos de potencia establecidos en [1.1]. Para niveles de potencia menores de 1,5 kW, el bus se diseña para operar a 28 V. Para rangos de potencia comprendidos entre 1,5 kW y 8 kW, el nivel de tensión de bus será de 50 V. Finalmente, para potencias por encima de 8 kW, los niveles de tensión de bus están comprendidos entre 100 V y 120 V.

A su vez, el bus de potencia secundario es el encargado de adaptar los niveles de tensión del bus (28 V, 50 V ó 100 V) a los niveles de tensión requeridos por los distintos subsistemas que forman el satélite. En este sentido conviene destacar que las baterías presentan niveles de tensión inferiores, y cercanos a los niveles de tensión de bus. La estructura de cada una de estas fuentes suele estar basada en un convertidor sencillo, que por normativa suele ser aislado (Flyback o Fordward), seguido de un regulador lineal para la adaptación al nivel de tensión requerida por el subsistema al que se conecta.

Finalmente, entre el bus de potencia principal y el bus de potencia secundario, se encuentra el sistema de distribución, formado por los limitadores de corriente de enclavamiento (*Latching Current Limiters*, LCLs) [1.11], [1.12]. Estos circuitos se encargan de proporcionar protección al bus de potencia frente a sobrecargas, así como también de la distribución de potencia eléctrica de forma segura en los satélites. El Capítulo 4, de este documento de tesis, se centra en el análisis y diseño de este tipo de protecciones.

Por razones de fiabilidad, se emplea redundancia (típicamente 2+1), con lo que cada uno de los bloques SAR, BCR y BDR se componen de tres módulos en paralelo dimensionados para procesar la mitad de la potencia nominal. De esta forma, si se produjese un fallo en alguno de ellos, todavía se dispondría de dos módulos capaces de proporcionar toda la potencia necesaria. Con el objetivo de que esta redundancia sea efectiva, cada convertidor tiene que poder evitar que un fallo interno se propague fuera, afectando con ello al correcto funcionamiento de los otros módulos. Esto implica incluir interruptores adicionales en la entrada y/o salida del convertidor para permitir su desconexión del sistema en caso de fallo. Esta inclusión de interruptores extra afectará de manera negativa a aspectos tales como el coste, el tamaño y el rendimiento de cada convertidor.

Fig.1.3. Esquema básico de un sistema de potencia regulado en un satélite

#### 1.2.4.- Subsistema de control térmico

Este subsistema se encarga de mantener la temperatura del satélite dentro de los límites establecidos, durante las misiones. Proporciona refrigeración de manera activa o pasiva, según sea necesario. Este subsistema está formado por disipadores, calentadores, sensores de temperatura (termistores), así como también instrumentación electrónica [1.13],[1.14]. Estos equipos están diseñados teniendo en cuenta la potencia media de disipación, el calor externo procedente del sol, la luz solar reflejada por la Tierra (albedo), y el calor derivado de la radiación infrarroja de la Tierra.

En el espacio se hace complicado el poder llegar a corregir los problemas derivados de la disipación de calor. De esta manera, se hace necesario que el subsistema de control térmico esté correctamente diseñado y verificado, y que presenta un alto rendimiento y fiabilidad. Este subsistema es el encargado de mantener la temperatura estable de componentes electrónicos sensible, y de componentes ópticos.

El control térmico, en el ámbito de las aplicaciones espaciales cubre un amplio rango de temperaturas, desde el nivel criogénico (menos de -270 °C), hasta la protección térmica a altas temperaturas (por encima de 2000 °C). En este sentido, el subsistema de control térmico es absolutamente esencial desde el punto de vista de la integridad física del satélite y de la operación óptima de los componentes y equipos electrónicos del mismo. En el caso de las cargas de pago, son las que dictan su rango de operación. Por ejemplo, infrarrojos algunos instrumentos con detectores requieren extremadamente bajas. Existen otros muchos temperaturas componentes cuya vida útil se puede ver reducida, debido a altas temperaturas.

El nivel de temperatura de una nave espacial está determinado por el balance entre la radiación solar externa, el albedo y los propios flujos de calor, producidos internamente por los equipos electrónicos, y considerando también el calor lanzado al exterior. De esta forma, el subsistema térmico siempre busca el mantener la temperatura global del satélite en un valor aceptable, y al mismo tiempo obtener la distribución más adecuada de la temperatura dentro del propio satélite.

# 1.2.5.- Subsistema de propulsión

Este subsistema proporciona a los satélites la fuerza para ajustar su órbita alrededor de la Tierra y, para mantenerse por debajo de un nivel máximo, durante la duración de la misión espacial. Por lo general, esto se consigue a través de una mezcla de gases de alta presión como el helio o el nitrógeno [1.15].

A día de hoy se continúan desarrollando nuevas tecnologías para permitir lanzamientos más fiables, a menor coste, y que presenten menores niveles de contaminación. En el caso de los cohetes, por ejemplo, típicamente se emplea "propulsión química", fundamentalmente de dos tipos: líquida y sólida. Mientras que la propulsión líquida es más eficiente, la sólida es más sencilla, segura y barata.

La <u>propulsión líquida</u> combina combustible con oxígeno en una cámara de combustión. La explosión de dicha mezcla genera gases de combustión. Estos gases se propulsan desde el motor, permitiendo el lanzamiento del cohete. En este caso, el nivel de combustible se puede controlar, así como también se puede regular el empuje producido por la propia propulsión.

La <u>propulsión sólida</u> funciona empleando el mismo principio que en el caso de los fuegos artificiales. En esta ocasión, se emplea una mezcla de combustible y oxidante, que a través de su combustión permite el despegue del cohete.

Una alternativa a la llamada propulsión química sería <u>la propulsión</u> <u>eléctric</u>a. Se trata de un método más eficiente que emplea la electricidad para expulsar gases a alta velocidad. Hoy en día, la

propulsión eléctrica se está convirtiendo en una tecnología muy madura, cuyo uso se está incrementado [1.16], [1.17]. En este sentido, los motores electroestáticos son particularmente preciados por su habilidad para proporcionar un empuje continuado durante períodos de tiempo prolongados, limitando el nivel de combustible.

# 1.3.- Evolución en el uso de los satélites

El *Sputnik I* fue el primer satélite artificial de la historia, puesto en órbita por parte de la Unión Soviética el 4 de octubre de 1957 [1.18]. Desde el punto de vista de la alimentación, integraba una única batería de plata-zinc la cual proporcionaba una potencia de 1 W para alimentar a dos transmisores. Dicha batería (no recargable) definía el límite de vida útil de la nave espacial. Este primer satélite fue seguido pronto por el modelo *Vanguard I* (1958), siendo este el primer satélite en incorporar celdas solares acopladas al sistema de baterías secundario (baterías recargables). Las baterías fueron incluidas con el objetivo de proporcionar alimentación durante los períodos de eclipse.

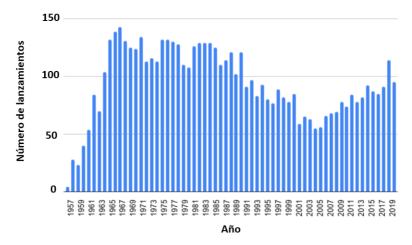

Desde entonces, el nivel de sofisticación a la hora de diseñar e implementar satélites artificiales, y de atender a las demandas energéticas que requieren para hacerlos funcionales, se ha visto incrementado en varios órdenes de magnitud. Lo que en su momento supuso una curiosidad científica se ha convertido en una herramienta indispensable hoy en día, desde el punto de vista de las comunicaciones, la meteorología, la observación, la navegación, la geodesia, la defensa nacional, el entretenimiento y el propio descubrimiento científico. De esta forma, desde aquellos primeros días y modelos de satélites, la frecuencia con la que se han llevado a cabo lanzamientos de satélites ha hecho del evento algo común. La Fig.1.4 muestra la evolución en el número de satélites lanzados en todo el mundo, desde 1957 hasta 2019 [1.19]. Si bien no ha sido una pauta

exclusivamente creciente, se debe tener en cuenta también el tamaño y las dimensiones de los satélites lanzados a lo largo del tiempo. Mientras que el primer *Sputnik* tenía un peso de unos pocos kilogramos, los lanzadores empleados en la actualidad presentan capacidades de carga de hasta mil kilogramos [1.18]. Aunque con los sistemas modernos se pueden poner en órbita cargas que sobrepasan los mil kilogramos con relativa facilidad, el coste del lanzamiento se mantiene muy alto (típicamente varios cientos de dólares por kilogramo, dentro de la órbita terrestre).

Fig.1.4. Número de satélites lanzados entre 1957 y 2019 [1.19]

## 1.3.1.- Paradigma "new space"

Uno de los cambios actuales en la forma de construir y plantear los sistemas de satélites ha venido de la mano del paradigma "new space" [1.20]. Este concepto hace referencia a una nueva manera de proceder dentro de la industria aeroespacial. De esta forma, la idea se basa en desarrollar una industria privada encargada del diseño, fabricación y puesta en marcha de satélites, y de aeronaves, con un claro objetivo comercial, trabajando de manera independiente a los gobiernos. Para ello se plantean desarrollos rápidos, modulares y más económicos, de

tecnologías espaciales, pensadas para uso comercial. Actualmente, existen tres grandes empresas operando bajo esta nueva filosofía: *SpaceX, Blue Origin y Virgin Galactic*.

Dentro de esa nueva filosofía existen varias metas a conseguir [1.21]. Por un lado, una innovación en los procesos industriales de desarrollo y manufacturación, basados en la reducción de tiempos de desarrollo. En este sentido, se plantea el poder adaptar algunas de las técnicas presentes en la producción en masa de la empresa del automóvil. Por otro lado, en todo aquello que tiene que con los tiempos de desarrollo de un producto hasta que se obtiene un producto final. La idea se basa en poder llegar a desarrollar entre 40 y 60 satélites por mes, (2 ó 3 satélites al día) [1.21], lo cual supone un ritmo de producción nunca visto en la industria espacial. De la misma manera, se persigue el comprimir costes en el desarrollo de las satélites fijando como objetivo un intervalo entre los 400.000 y los 500.000 dólares [1.21]. Desde el punto de vista de nuevos lanzamientos, se piensa en poder llegar a poner en órbita nuevos satélites cada 21 días [1.21].

Como ejemplo de esta nueva filosofía en el desarrollo de satélites, de encuentran las llamadas mega-constelaciones [1.22]. Una mega-constelación puede verse como un sistema que utiliza desde decenas hasta cientos de miles de satélites trabajando en la llamada órbita terrestre baja (*Low Earth Orbit* – LEO), con el objetivo de proporcionar servicios de datos de banda ancha y baja latencia, en cualquier parte del planeta. Los satélites que forman parte de este tipo de sistemas ocupan órbitas entre 400 km y 1220 km.

En este caso, el cambio de paradigma en su construcción se basa en que, para ser económicamente viables, este tipo de satélites se construyen en serie, intentando ser lo más pequeños y económicos posible, sin dejar de ser capaces de prestar los servicios requeridos.

Las áreas de aplicación de este tipo de sistemas van desde los servicios bancarios de baja latencia, hasta la capacidad de

proporcionar conexión a internet en áreas remotas, así como servicios de comunicación para aeronaves, barcos y potenciales usuarios militares.

El hecho de que los satélites que forman parte de estas megaconstelaciones se tengan que fabricar de manera asequible, conduce a la producción en masa. De esta manera, el tener que incorporar la automatización hace que la industria satelital acabe pareciéndose cada vez más a la industria de la automoción. Esta producción en serie supone un cambio muy significativo en la forman en la que se construyen los satélites, y abre la necesidad de plantearse cómo se pueden conseguir mejores tiempos de desarrollo, buena calidad y bajo coste, con el objetivo de conseguir equipos baratos, rápidos y mejores.

A modo de ejemplo de mega-constelaciones, se mencionan los casos:

<u>Starlink:</u> Empresa dentro del proyecto *SpaceX* pensada para el despliegue de una constelación de satélites con el objetivo de proporcionar servicio de internet de banda ancha, baja latencia y cobertura mundial, de bajo coste. En este sentido se trata de una megaconstelación formada por 12000 satélites (dato 2020) [1.23].

<u>OneWeb:</u> Se trata de una empresa de comunicaciones que ha comenzado con el lanzamiento de su propia constelación de satélites formada por 650 equipos en órbita LEO. El objetivo se basa en proporcionar acceso a internet en lugares rurales y remotos [1.24]. En este caso los satélites están construidos de manera conjunta entre *Airbus* y la propia *OneWeb*.

<u>Kuiper:</u> En este caso se trata de una mega-constelación de satélites que planea desplegar Amazon. Dicha constelación estaría formada por 3236 (dato 2020) satélites en órbita LEO, con el objetivo de competir con la desarrollada por *Starlink*. Al igual que en los casos anteriores, la idea se basa en proporcionar servicios de banda ancha, rápida y asequible en lugares remotos [1.25].

# 1.4.- La creciente demanda de potencia en las naves espaciales

El incremento en el nivel de sofisticación de los satélites, así como también en sus dimensiones, ha ido acompañado de un incremento constante en sus requisitos de potencia. La Fig.1.5 muestra el crecimiento de la potencia necesaria por las naves espaciales desde los años 60 a los 2000. En cierto sentido, las demandas energéticas en los satélites de comunicaciones pueden tomar dos caminos distintos, dependiente de las órbitas. Por un lado, los satélites geosíncronos de comunicaciones suelen requerir entre 10 y 20 kW de potencia [1.18], frente a los satélites más pequeños, de órbitas más bajas, cuyos requisitos de potencia suelen variar entre las decenas y las centenas de watios [1.18]. Para el resto de las aplicaciones, como puede ser la distribución de televisión privada en el hogar o los satélites de difusión directa, la tendencia ha ido hacia el incremento en el nivel de potencia requerido por las naves espaciales.

Fig.1.5 Crecimiento en los requisitos de potencia de las navas espaciales entre la década de los 60 y los 2000 [1.18]

## 1.4.1.- Problemática y motivación

A pesar del uso masivo de los satélites, existen una serie de problemáticas asociadas con el subsistema de potencia, en las que se centra el trabajo desarrollado en este documento de tesis. Como se ha comentado, la función del subsistema de potencia en los satélites es la de generar, distribuir y almacenar la potencia eléctrica necesaria en los demás subsistemas que forman el satélite. Dicha energía será obtenida a través de los paneles solares. Sin embargo, mientras que los rangos de tensiones en el bus de potencia están estandarizados a determinados valores, la tensión en los paneles solares carece de este nivel de estandarización.

Esto hace que los distintos bloques que forman el subsistema de potencia tengan que ser rediseñados, prácticamente desde cero, para cada nueva misión con el correspondiente incremento en costes y tiempos de desarrollo. En este sentido, este rediseño afecta a los bloques SAR, BCR y BDR que forman el subsistema de potencia del satélite. Como se ha comentado, la solución actual pasa por implementar distintas topologías para cada módulo. En este caso, se trataría de topologías reductoras [1.7], [1.8] para los bloques SAR y BCR, y de topologías elevadoras para el bloque BDR [1.9], [1.10].

Otro aspecto relevante dentro del diseño aeroespacial es que no existe normalización en el diseño del panel solar, o en la potencia nominal del satélite. Como consecuencia, las características de tensión y corriente del panel solar son distintas para cada satélite, ya que dependen enormemente de la geometría [1.26] disponible para el almacenamiento y despliegue del mismo, la potencia a montar, y otra serie de aspectos constructivos y mecánicos. De esta forma, el diseño del SAR debe replantearse prácticamente desde cero para cada nueva misión espacial. Los cambios de potencia nominal entre satélites hacen que el BCR y el BDR también deban ser rediseñados para cada

nueva misión, pues los niveles de tensión de bus cambian, tal y como se explicó en anteriormente.

Teniendo en cuenta la proliferación y el uso masivo de satélites [1.27], tanto desde el punto de vista gubernamental, como a través de la reciente irrupción del sector privado, se hace necesario encontrar soluciones y planteamientos que permitan acortar los tiempos de desarrollo de un satélite, así como también estandarizar su fabricación y sus componentes. De esta forma, también se hace interesante el poder encontrar una topología óptima (desde el punto de vista del rendimiento) que pueda ser empleada en los tres bloques del subsistema de potencia. Dicha topología debe de ser capaz de elevar o reducir tensión en función del bloque en el que se coloque (SAR, BCR o BDR), debiendo estar protegida frente a la propagación de fallos.

Es precisamente en este sentido, y en esta falta de estandarización, donde se encuentra focalizado este trabajo de tesis, y donde la ESA plantea sus necesidades y demandas. Como se detalla en el siguiente apartado de Objetivos y Contribuciones, este trabajo pretende aportar una solución intermedia entre el panel solar y el SAR, con el objetivo de reaprovechar el bloque SAR entre misiones espaciales distintas, de la misma manera que abre la posibilidad a reaprovechar paneles solares entre satélites.

Es aspecto contribuye a conseguir una mayor estandarización en el diseño de los satélites, al mismo tiempo que persigue una reducción en los tiempos de desarrollo de estos. La idea fundamental de este trabajo se basa en ir introduciendo los factores de estandarización y reusabilidad, como aspectos clave, en el diseño y la construcción de los satélites.

# 1.5.- Objetivos y contribuciones originales de este trabajo

El objetivo de este trabajo pasa por el desarrollo de topologías y circuitos electrónicos para la mejora del bus de potencia y del subsistema de distribución en satélites.

Desde el punto de vista del subsistema de potencia, se plantea la posibilidad de un diseño modular a nivel de convertidor. De esta forma, se tendrá un diseño fijo de los bloques SAR, BCR y BDR, independientes de panel solar empleado en las distintas misiones espaciales. Esto a su vez, permite una reducción en los costes y tiempos de desarrollo en el subsistema de potencia del satélite.

Por su parte, el subsistema de distribución del satélite es en el que se implementan los sistemas de protección del bus principal frente a sobrecargas. En este sentido, los dispositivos limitadores de corriente de enclavamiento (LCLs) hacen las veces de fusibles de protección, rearmables. En este trabajo se plantea una nueva topología de LCL basada en transistores N-MOS de carburo de silicio (SiC), frente a los transistores P-MOS de silicio, tradicionalmente utilizados. De esta forma, se podría llegar a reducir las pérdidas presentes en este tipo de circuitos, mejorando su eficacia.

Las contribuciones originales de este trabajo son las siguientes:

Arquitecturas. Se realiza un análisis de las arquitecturas posibles, con el objetivo de simplificar el bus de potencia de los satélites, que cumplan con los requisitos propuestos en un determinado caso de estudio. Se elige como solución aquella basada en el uso de transformadores de CC (DCX) similares a los planteados en [1.28]-[1.47], con el objetivo de llevar a cabo una solución que permita adaptar los niveles de tensiones y potencias de forma modular. De esta

forma, se consigue independizar el bloque SAR del panel solar empleado.

Diseño del convertidor modular DCX. Se lleva a cabo el diseño e implementación de la topología propuesta, en función de los requisitos establecidos. Esta topología se analiza desde el punto de vista de adaptación de los distintos de niveles de tensiones y potencias, al emplear varios módulos conectados entre sí. Se analiza también buscando un alto rendimiento y desde el punto de vista de su fiabilidad respecto a fallos.

<u>Diseño de la topología LCL basada en N-MOS de SiC.</u> Se propone una arquitectura de LCL basada en transistores N-MOS de SiC, en contrapartida a las topologías tradicionales basadas en transistores P-MOS [1.48]-[1.54]. El hecho de cambiar el transistor, que funciona como limitador de corriente, implica un rediseño completo en la etapa de control tradicional en este tipo de circuitos.

<u>Verificación del funcionamiento del LCL</u>. Una vez diseñada e implementada la topología, se evalúa su funcionamiento en función de las distintas clases de LCLs mostradas en [1.55]. De la misma manera, se plantean diferentes puntos de operación, dentro de una determinada clase, con el objetivo de analizar su fiabilidad.

De todos los estudios y resultados experimentales obtenidos, se extraen conclusiones sobre posibles mejoras de los sistemas planteados, y su correcta adecuación a las especificaciones de diseño.

# 1.6.- Bibliografía

[1.1] M. Patel, "Spacecraft Power Systems", Boca Raton (FL) 2005.

[1.2]Telemetry and Telecomand. [En línea]. Disponible en: https://www.esa.int/Enabling\_Support/Space\_Engineering\_Technology/Onbo ard\_Computers\_and\_Data\_Handling/Telemetry\_Telecommand (Última visita: 12 de Abril 2022)

- [1.3] Artur Scholz, "Command and data handling system design for the COMPASS-1 picosatellite", University of Applied Sciences Aachen, Germany, May 2005

- [1.4] Control Systems [En línea]. Disponible en: https://www.esa.int/Enabling\_Support/Space\_Engineering\_Technology/Cont rol\_Systems (Última visita: 12 de Abril 2022)

- [1.5] Attitude Control System [En línea]. Disponible en: https://www.ohb-system.de/position-control.html (Última visita: 12 de Abril 2022)

- [1.6]Power Systems [En línea]. Disponible en: https://www.esa.int/Enabling\_Support/Space\_Engineering\_Technology/Power\_Systems (Última visita: 12 de Abril 2022)

- [1.7] G. Xu, Z. Li, S. Wang and L. Jiang, "Study on high efficiency power supply with wide input voltage for stratospheric airships," 2014 IEEE Aerospace Conference, Big Sky, MT, 2014, pp. 1-7, doi: 10.1109/AERO.2014.6836517.

- [1.8] J. Leppäaho and T. Suntio, "Solar-generator-interfacing with a current-fed superbuck converter implemented by duality-transformation methods," The 2010 International Power Electronics Conference ECCE ASIA -, Sapporo, 2010, pp. 680-687, doi: 10.1109/IPEC.2010.5543658.

- [1.9] E. Maset, A. Ferreres, J. B. Ejea, E. Sanchis-Kilders, J. Jordan and V. Esteve, "5kW Weinberg Converter for Battery Discharging in High-Power Communication Satellites," 2005 IEEE 36th Power Electronics Specialists Conference, Recife, 2005, pp. 69-75, doi: 10.1109/PESC.2005.1581604.

- [1.10] J. M. Blanes et al., "Two-Stage MPPT Power Regulator for Satellite Electrical Propulsion System," in IEEE Transactions on Aerospace and Electronic Systems, vol. 47, no. 3, pp. 1617-1630, July 2011, doi: 10.1109/TAES.2011.5937254.

- [1.11] D. Marroqui, A. Garrigos, J. Blanes, R. Gutierrez and E. Maset, "SiC Based Latching Current Limiter for High Voltage Space Power Distribution Systems," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, 2018, pp. 3669-3673, doi: 10.1109/ECCE.2018.8557760.

- [1.12] D. Marroqui, A. Garrigos, J. M. Blanes, R. Gutiérrez and E. Maset, "Circuit proposals for high-voltage latching current limiters," 2019 European Space Power Conference (ESPC), Juan-les-Pins, France, 2019, pp. 1-8, doi: 10.1109/ESPC.2019.8931995.

- [1.13]Thermal Control [En línea]. Disponible en: https://www.esa.int/Enabling\_Support/Space\_Engineering\_Technology/Thermal\_Control (Última visita: 12 de Abril 2022)

- [1.14]Thermal Control [En línea]. Disponible en: https://www.nasa.gov/smallsat-institute/sst-soa/thermal-control (Última visita: 12 de Abril 2022)

- [1.15] Propulsion: lift-off, orbit adjustments and travelling through Space [En línea].https://www.esa.int/Enabling\_Support/Preparing\_for\_the\_Future/Discovery and Preparation/ (Última visita: 12 de Abril 2022)

- [1.16] A. Barzkar and M. Ghassemi, "Electric Power Systems in More and All Electric Aircraft: A Review," in IEEE Access, vol. 8, pp. 169314-169332, 2020, doi: 10.1109/ACCESS.2020.3024168.

- [1.17] Alan H. Epstein and Steven M. O'Flarity, "Considerations for reducing aviation's CO2 with aircraft electric propulsion" in Aerospace Research Central (ARC), Feb 2019, doi: 10.2514/1.B37015

- [1.18] Anthony K. Hyder, Ronald L. Wiley, G. Halpert, Donna Jones Flood, S. Sabripour, "Spacecraft power technologies", Imperial College Pres. 2000.

- [1.19] Increasing Access to space [En línea] Disponible en: https://www.clusterinc.com/articles/newsletter-vol-11-increasing-access-to-space, (Última visita: 21/01/2022)

- [1.20] The new space paradigm [En línea] Disponible en: http://trinitamonti.org/2020/07/15/the-newspace-paradigm-spacex-is-just-the-beginning/, (Última visita: 25/07/2022)

- [1.21] Space industry: On-going structural changes and paradigm shifts [En línea] Disponible en: https://www.emerton.co/space-industry-going-structural-changes-paradigm-shifts/ (Última visita: 25/07/2022)

- [1.22] Mega-constellations in Space: revolutionising the satellite industry [En línea] Disponible en: https://securecommunications.airbus.com/en/meet-the-experts/mega-constellations-in-space-revolutionising-satellite-industry, (Última visita: 20/04/2022)

- [1.23] El Sistema de internet de banda ancha más avanzado del mundo [En línea] Disponible en: https://www.starlink.com/satellites, (Última visita: 20/04/2022)

- [1.24]OneWeb Satellites [En línea] Disponible en: https://airbusonewebsatellites.com/, (Última visita: 20/04/2022)

- [1.25] Kuiper, la constelación de satélites de Amazon, [En línea], Disponible en: https://www.astrobitacora.com/kuiper-la-constelacion-de-satelites-de-amazon/, (Última visita: 20/04/2022)

- [1.26] Henry Louie and Peter Dauenhauer "Effects of Load Estimation Error on Small-Scale Off-Grid Photovoltaic System Design, Cost and Reliability", 2016 in Energy for suitable development, DOI: 10.1016/j.esd.2016.08.002.

- [1.27] Visualizing Earth satellite [En línea]. Disponible en: https://www.weforum.org/agenda/2020/10/visualizing-easrth-satellites-sapce-spacex. (Última visita: 14/06/2021).

- [1.28] Q. Zhu, L. Wang, L. Zhang and A. Q. Huang, "A 10 kV DC transformer (DCX) based on current fed SRC and 15 kV SiC MOSFETs," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), 2018, pp. 149-155, doi: 10.1109/APEC.2018.8341001.

- [1.29] Shiguo Luo, Zhihong Ye, Ray-Lee Lin and F. C. Lee, "A classification and evaluation of paralleling methods for power supply modules," 30th Annual IEEE Power Electronics Specialists Conference. Record. (Cat. No.99CH36321), 1999, pp. 901-908 vol.2, doi: 10.1109/PESC.1999.785618.

- [1.30] Wei Qin, Guixing Lan and Xinke Wu, "A family of ZVSZCS resonant DCX with DC resonant capacitor," 2015 IEEE 2nd International Future Energy Electronics Conference (IFEEC), 2015, pp. 1-6, doi: 10.1109/IFEEC.2015.7361431.

- [1.31] W. Qin, B. Zhu, X. Zhang and X. Wu, "A novel current-feed soft-switching two-switch forward resonant DC-DC Transformer (DCX)," 2014 International Power Electronics and Application Conference and Exposition, 2014, pp. 126-130, doi: 10.1109/PEAC.2014.7037841.

- [1.32] Xianjin Zhang and Caihong Fan, "Research on a novel DC-DC transformer," 2011 International Conference on Electric Information and Control Engineering, 2011, pp. 1619-1622, doi: 10.1109/ICEICE.2011.5778002.

- [1.33] Jung Won Kim, Hang Seok Choi and B. H. Cho, "A novel droop method for the converter parallel operation," APEC 2001. Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No.01CH37181), 2001, pp. 959-964 vol.2, doi: 10.1109/APEC.2001.912483.

- [1.34] G. Ivensky, A. Abramovitz, M. Gulko and S. Ben-Yaakov, "A resonant DC-DC transformer," [Proceedings] APEC '92 Seventh Annual Applied Power Electronics Conference and Exposition, 1992, pp. 731-737, doi: 10.1109/APEC.1992.228340.

- [1.35] Y. Panov, J. Rajagopalan and F. C. Lee, "Analysis and design of N paralleled DC-DC converters with master-slave current-sharing control," Proceedings of APEC 97 Applied Power Electronics Conference, 1997, pp. 436-442 vol.1, doi: 10.1109/APEC.1997.581489.

- [1.36] P. Czyz, T. Guillod, F. Krismer, J. Huber and J. W. Kolar, "Design and Experimental Analysis of 166 kW Medium-Voltage Medium-Frequency Air-Core Transformer for 1:1-DCX Applications," in IEEE Journal of Emerging and Selected Topics in Power Electronics, doi: 10.1109/JESTPE.2021.3060506.

- [1.37] L. Wang, Q. Zhu, W. Yu and A. Q. Huang, "A Medium-Voltage Medium-Frequency Isolated DC–DC Converter Based on 15-kV SiC MOSFETs," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 1, pp. 100-109, March 2017, doi: 10.1109/JESTPE.2016.2639381.

- [1.38] H. Fan and H. Li, "High-Frequency Transformer Isolated Bidirectional DC–DC Converter Modules With High Efficiency Over Wide Load Range for 20 kVA Solid-State Transformer," in IEEE Transactions on Power Electronics, vol. 26, no. 12, pp. 3599-3608, Dec. 2011, doi: 10.1109/TPEL.2011.2160652.

- [1.39] M. H. Ahmed, F. C. Lee and Q. Li, "Two-Stage 48-V VRM With Intermediate Bus Voltage Optimization for Data Centers," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 9, no. 1, pp. 702-715, Feb. 2021, doi: 10.1109/JESTPE.2020.2976107.

- [1.40] H. Shi, X. Wu and M. Xia, "Analysis of MHz 380V-12V DCX with Low FoM Device," 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 ECCE Asia), 2019, pp. 1821-1829, doi: 10.23919/ICPE2019-ECCEAsia42246.2019.8797111.

- [1.41] Ö. Ş. Alemdar and O. Keysan, "Design and implementation of an unregulated DC-DC transformer (DCX) module using LLC resonant converter," 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), 2016, pp. 1-6, doi: 10.1049/cp.2016.0156.

- [1.42] M. Fu, C. Fei, Y. Yang, Q. Li and F. C. Lee, "A GaN-Based DC–DC Module for Railway Applications: Design Consideration and High-Frequency Digital Control," in IEEE Transactions on Industrial Electronics, vol. 67, no. 2, pp. 1638-1647, Feb. 2020, doi: 10.1109/TIE.2019.2896279.

- [1.43] G. Deng et al., "ZVS Analysis of Half Bridge LLC-DCX Converter Considering the Influence of Resonant Parameters and Loads," 2020 IEEE

- Energy Conversion Congress and Exposition (ECCE), 2020, pp. 1186-1190, doi: 10.1109/ECCE44975.2020.9235371.

- [1.44] H. Zhou et al., "Input-Series Output-Equivalent-Parallel Multi-Inverter System for High-Voltage and High-Power Wireless Power Transfer," in IEEE Transactions on Power Electronics, vol. 36, no. 1, pp. 228-238, Jan. 2021, doi: 10.1109/TPEL.2020.3000244.

- [1.45] R. Ramachandran and M. Nymand, "Experimental Demonstration of a 98.8% Efficient Isolated DC–DC GaN Converter," in IEEE Transactions on Industrial Electronics, vol. 64, no. 11, pp. 9104-9113, Nov. 2017, doi: 10.1109/TIE.2016.2613930.

- [1.46] H. Chen and X. Wu, "LLC resonant DC transformer (DCX) with parallel PWM output tight regulation," 2014 IEEE Energy Conversion Congress and Exposition (ECCE), 2014, pp. 4742-4747, doi: 10.1109/ECCE.2014.6954050.

- [1.47] X. Chen et al., "A Natural Bidirectional Input-Series—Output-Parallel LLC-DCX Converter With Automatic Power Sharing and Power Limitation Capability for Li-Ion Battery Formation and Grading System," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 4, pp. 3618-3632, Dec. 2020, doi: 10.1109/JESTPE.2019.2941583.

- [1.48] A. Soto, L. Jimenez, E. Lapeña, C. Delepaut, "Stability analysis for the LCL of GEO-PCDU product," 10th ESPC, 13 –17 April 2014 Noordwijkerhout, The Netherlands.

- [1.49] C. Delepaut, T. Kuremyr, M. Martin, F. Tonicello, "LCL current control loop stability design," 10th ESPC, 13 –17 April 2014 Noordwijkerhout, The Netherlands.

- [1.50] S. Pappalardo, C. Ribellino, I. Mirabella et al. "Integrated Current Limiter: Applications tests," 10th ESPC, 13 –17 April 2014 Noordwijkerhout, The Netherlands.

- [1.51] A. V. Dias, J. A. Pomilio and S. Finco, "A current limiting switch for applications in space power systems," 2017 IEEE Southern Power Electronics Conference (SPEC), 2017, pp. 1-6, doi: 10.1109/SPEC.2017.8333594.

- [1.52] F. Tonicello, O. El Korashy, A. Pesce, "Perfomance and simplicity in power conversion functions made possible by new European components," 9th ESPC, 6 10 June 2011, Saint Raphäel, France.

- [1.53] H. Shi, C. Zhao, Y. Jin and Y. Liu, "Current limiting protection in spacecraft power system," 2015 3rd International Conference on Electric

Power Equipment – Switching Technology (ICEPE-ST), 2015, pp. 561-565, doi: 10.1109/ICEPE-ST.2015.7368377.

- [1.54] M. Komatsu, N. Ide and S. Yanabu, "A Solid-State Current Limiting Switch for Application of Large-scale Space Power Systems," 2007 IEEE Power Electronics Specialists Conference, 2007, pp. 1471-1476, doi: 10.1109/PESC.2007.4342211.

- [1.55] "Space engineering Electrical design and interface requirements for power supply, ECSS-E-ST-20-20C". ECSS Secretariat ESA-ESTEC Requirements & Standards Division Noordwijk, The Netherlands, 15 April 2016.

# Capítulo 2: Estandarización del bus de potencia en satélites

Como se ha comentado en el Capítulo 1, la energía empleada por el subsistema de potencia de los satélites se obtiene a partir de paneles solares. Además, existen un conjunto de convertidores y baterías encargados de procesar y almacenar dicha energía cuando el consumo del satélite es menor que la potencia que entregan los paneles, y la ceden cuando dicha situación se invierte.

Como se verá en este capítulo, uno de los principales problemas a los que se enfrenta el diseño de satélites, es la falta de estandarización. Este aspecto, al que ya se hacía referencia en el Capítulo 1, junto con la mayor irrupción de la empresa privada en el ámbito espacial, hace necesario replantear el diseño y los costes derivados del mismo en la fabricación de los satélites. En este capítulo se aborda la posibilidad de replantear el subsistema de potencia a nivel convertidor, con el objetivo de desarrollar una única topología válida. De esta forma, el rediseño necesario para cada misión se vería drásticamente minimizado o, incluso, eliminado. En primer lugar, se presenta un análisis de una serie de topologías aisladas que podrían ser las más idóneas para la estandarización del subsistema de potencia regulado, con la condición de maximizar el rendimiento. Finalmente, se presenta el uso de un transformador electrónico como posible solución alternativa de cara a independizar el subsistema de potencia del diseño variable del panel solar.

### 2.1.- Motivación

El objetivo de este capítulo se basa en presentar una serie de criterios que permitan comparar entre distintas topologías, con las que implementar los bloques SAR, BCR y BDR, y pensadas para simplificar y estandarizar el subsistema de potencia en satélites. De la misma manera, se plantea el mecanismo de selección de los componentes (semiconductores, y componentes magnéticos) empleados en las distintas topologías seleccionadas.

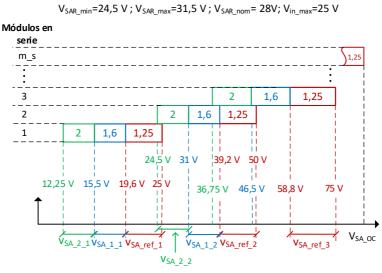

En el caso de todas estas topologías (módulos), denotadas como básicas en este capítulo, la adaptabilidad a distintos diseños (i.e. satélites), estaría basada en el rediseño de los componentes magnéticos que las forman, así como también en las distintas conexiones serie/paralelo entre entradas y paralelo entre salidas de estas, con el objetivo de escalar y adaptar los distintos niveles de tensión y potencia, a los necesarios, en función del punto de trabajo.

# 2.2.- Requisitos empleados en la selección y comparativa de topologías modulares

La selección de la topología óptima para la estandarización de los convertidores empleados en el subsistema de potencia regulado (Fig.2. 1) debe atenerse a las reglas que rigen el diseño de convertidores para aplicaciones aeroespaciales y a las circunstancias propias del entorno en las que va a operar el convertidor (i.e. el espacio). El hecho de que el convertidor debe elevar o reducir la tensión en función del bloque en el que se vaya a implementar hace de las topologías aisladas buenas candidatas para su posible implementación. Por un lado, está el hecho de que algunas topologías aisladas, basadas en estructuras en medio

puente y puente completo, están inherentemente protegidas frente a fallo, como se verá a continuación, y por otro lado, está el hecho de que el cambio entre elevador y reducir tensión, puede lograrse mediante un número reducido de elementos en el diseño del convertidor.

Fundamentalmente, los cambios se basarían en el rediseño del transformador magnético, y en la etapa de rectificación, debido a cambios en el nivel de tensión del bus. En cualquier caso, con un número reducido de transformadores y etapas de rectificación, podría conseguirse que un mismo convertidor (módulo) pueda funcionar en modo reductor o elevador en los distintos bloques que forman el bus de potencia.

Fig.2. 1. Esquema del bus de potencia regulado de un satélite

#### 2.2.1.- Análisis de la fiabilidad

En este apartado se analizará la fiabilidad de los componentes electrónicos y de las topologías propuestas para la estandarización del subsistema de potencia. Para llevar a cabo esta tarea, se emplea el documento "Failure modes, effects and criticality analysis" (FMECA) con referencia ECCS-Q-ST-30-02C [2.1]. En este documento, se establecen los principios y requisitos que se deben cumplir en relación con los posibles modos de fallo de los componentes, y en cómo estos

puedan influir en el resto de los módulos conectados al bus de potencia del satélite.

En relación con el FMECA, los componentes de interés, desde el punto de vista de la fiabilidad y de sus posibles modos de fallo, serían:

- 1. Diodos, analizando fallo por cortocircuito (FCC) y por circuito abierto (FCA).

- 2. Transistores, analizando posible FCC o FCA.

- 3. Transformadores, considerando FCC entre espiras, FCC entre terminales, FCC entre devanados, FCC entre devanados y núcleo y FCA entre terminales.

- 4. Bobinas, considerando FCC entre terminales, FCC entre espiras, FCC entre devanado y núcleo y FCA entre terminales.

Para este análisis sólo se considerarán los dos primeros casos (fallos en diodos y transistores), ya que son aquellos componentes cuyos fallos potenciales pueden tener las peores consecuencias, desde el punto de vista de producir pérdida de funcionalidad en los bloques SAR, BCR y BDR.

En este caso, de acuerdo con lo indicado en la sección 4.13 del documento ECCS-Q-ST-30-02C [2.1], se trata de un análisis de fallo único, es decir, sólo se considera un único fallo por módulo/convertidor. De esta forma, los fallos en los componentes magnéticos pueden afectar al correcto funcionamiento de la topología que se esté analizando, pero en el caso de considerar redundancia, simplemente desconectado dicho módulo del bus de potencia, el fallo no debería propagarse ni afectar a la misión.

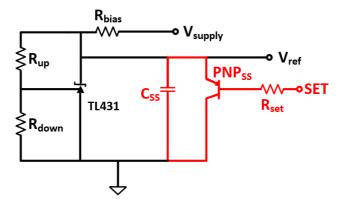

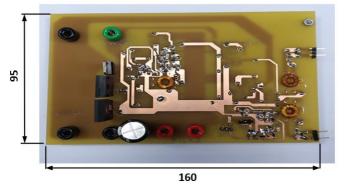

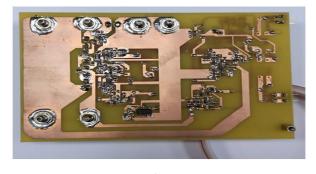

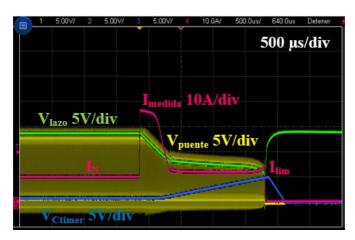

En el caso de los condensadores, su análisis no resulta muy relevante ya que se plantea el uso de condensadores autorreparables (*self-healing*), lo cual implica la no posibilidad de que se produzca un FCC en los mismos.