Universidad de Oviedo

Tesis Doctoral Programa de Doctorado en Energía y Control de Procesos

Análisis dinámico y desarrollo de sistemas de control distribuidos en celdas de potencia y convertidores multipuerto para integración en red de recursos distribuidos

Geber Villa Fernández

#### UNIVERSITY OF OVIEDO Department of Electrical, Electronics, Communications and Systems Engineering

#### Ph.D. THESIS DISSERTATION

#### Dynamic analysis and development of distributed control systems in power cells and multiport converters for grid integration of distributed resources

Dissertation submitted in fulfilment of the requirements for the degree of Doctor of Philosophy in the Energy and Process Control PhD program of the University of Oviedo with International Mention

### Geber Villa Fernández

Supervisor: Pablo García Fernández. Department of Electrical, Electronics, Communications and Systems Engineering

Gijón, February 2022

#### UNIVERSIDAD DE OVIEDO Departamento de Ingeniería Eléctrica, Electrónica, de Comunicaciones y de Sistemas

## TESIS DOCTORAL

#### Análisis dinámico y desarrollo de sistemas de control distribuidos en celdas de potencia y convertidores multipuerto para integración en red de recursos distribuidos

Tesis presentada en cumplimiento de los requisitos para la obtención del título de Doctor en el programa de doctorado de Energía y Control de Procesos de la Universidad de Oviedo con Mención Internacional

#### Geber Villa Fernández

Director: Pablo García Fernández. Departamento de Ingeniería Eléctrica, Electrónica, de Comunicaciones y de Sistemas

Gijón, Febrero 2022

A mis padres, hermanos, familia y amigos...

## Agradecimientos

Dedicado a mi director de tesis, mis compañeros de universidad, mi familia y mis amigos.

#### **RESUMEN DEL CONTENIDO DE TESIS DOCTORAL**

| 1 Título de la Tesis                       |                                          |

|--------------------------------------------|------------------------------------------|

| Español: Análisis dinámico y desarrollo de | Inglés: Dynamic analysis and development |

| sistemas de control distribuidos en celdas | of distributed control systems in power  |

| de potencia y convertidores multipuerto    | cells and multiport converters for grid  |

| para integración en red de recursos        | integration of distributed resources     |

| distribuidos                               |                                          |

| 2 Autor                                               |     |  |  |  |  |  |  |

|-------------------------------------------------------|-----|--|--|--|--|--|--|

| Nombre: Geber Villa Fernández                         | DNI |  |  |  |  |  |  |

|                                                       |     |  |  |  |  |  |  |

| Programa de Doctorado: Energía y Control de Procesos  |     |  |  |  |  |  |  |

| Órgano responsable: Centro Internacional de Postgrado |     |  |  |  |  |  |  |

#### **RESUMEN (en español)**

El objetivo de esta tesis es el desarrollo de sistemas de control adaptados a convertidores de potencia multipuerto para integración en red de recursos distribuidos. El estudio pretende dar respuesta a un cambio en el paradigma en el diseño de sistemas de control para convertidores de potencia, desde unidades de potencia con un diseño rígido y específico para cada aplicación de generación centralizada hacia implementaciones alternativas con un diseño adaptativo y genérico que pueda ser integrado en múltiples aplicaciones de generación distribuida.

El trabajo desarrollado se centra en la explotación de un convertidor de potencia modular formado a partir de celdas básicas de potencia, a fin de proponer una configuración multipuerto que permita la interconexión de unidades de potencia de diversa naturaleza, la integración con la red eléctrica y el apoyo de sistemas de almacenamiento de energía.

Por tanto, inicialmente, se realiza una revisión de los diferentes diseños de celdas de potencia para determinar la opción más adecuada para la implementación del convertidor.

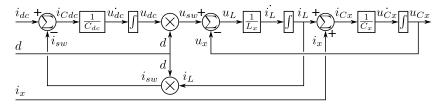

Una vez seleccionada la configuración del convertidor, se lleva a cabo el modelado matemático del mismo en espacio de estados a partir del modelo promediado de gran señal. El modelo es adecuado para realizar el análisis dinámico del sistema a fin de comprender su comportamiento y posteriormente ser utilizado en el diseño del sistema de control.

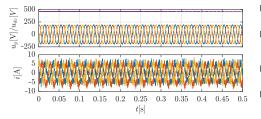

Este modelo matemático es validado mediante la comparación con el modelo conmutado del convertidor, obteniéndose unos resultados equivalentes con la ausencia del rizado de alta frecuencia derivado de la conmutación de los interruptores de potencia.

Utilizando la información adquirida a partir del modelo matemático, se establecen los requerimientos para determinar el sistema de control distribuido más adecuado para la explotación del convertidor de potencia modular multipuerto.

Llegados a este punto, se propone una arquitectura de control distribuido para el convertidor multipuerto.

Esta arquitectura se desarrolla para tener en cuenta la configuración modular del convertidor, por lo que sigue una estructura jerárquica formada por diversos controladores distribuidos, los cuales gestionan las tareas de control a nivel de celda de potencia, supeditados a un controlador central, el cual gestiona las tareas de control a nivel de sistema y aplicación. Los controladores distribuidos a cargo de las celdas de potencia son diseñados para seguir una estructura común y adaptable, con el fin de habilitar la integración de diferentes unidades de potencia en el convertidor sin grandes modificaciones en la arquitectura de control.

Posteriormente, se integra el controlador central en un sistema embebido basado en un microprocesador de propósito general, proporcionando versatilidad, escalabilidad y capacidad computacional al mismo tiempo.

#### Universidad de Oviedo

El microprocesador se maneja mediante un sistema operativo Linux para aprovechar su gran soporte y facilitar la ejecución de tareas auxiliares no críticas, junto con una extensión en tiempo real que habilita la ejecución de tareas de control críticas y con restricciones firmes de tiempo real.

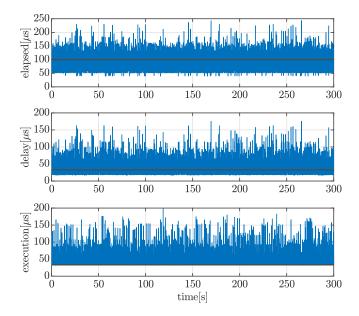

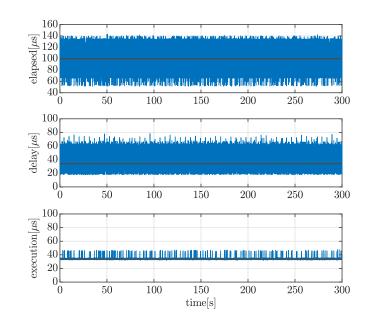

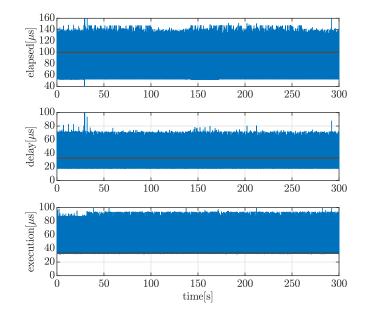

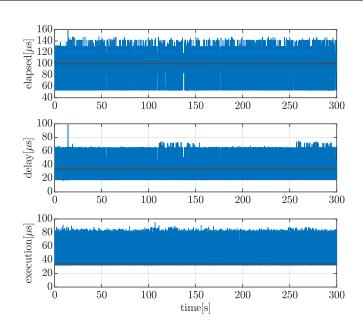

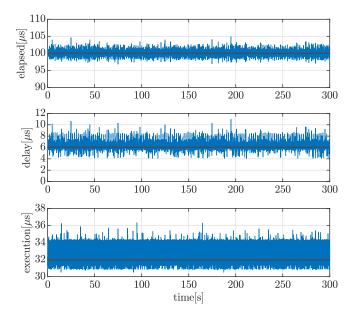

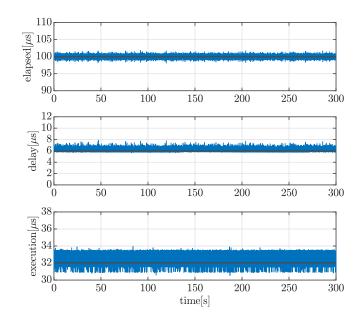

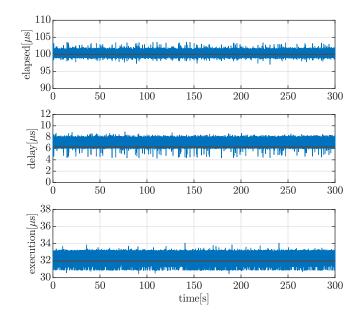

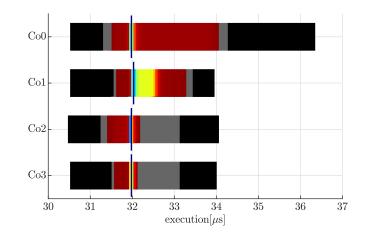

La validación del sistema embebido para su integración en el sistema de control se determina analizando la correcta ejecución de tareas en tiempo real, demostrando una operación determinista con un número despreciable de incumplimientos de plazos.

Finalmente, se desarrolla e implementa una aplicación basada en el uso de un convertidor multipuerto controlado mediante el sistema de control distribuido propuesto.

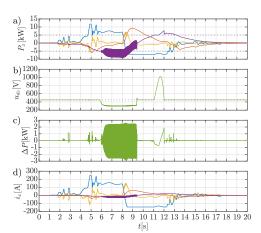

Dicha aplicación permite la operación de una unidad de potencia bidireccional siguiendo un determinado perfil de potencia, bajo restricciones de potencia máxima de red, y con el apoyo de un sistema de almacenamiento de energía híbrido.

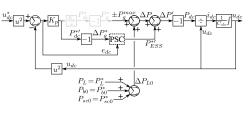

Para este propósito, se implementa un algoritmo de reparto de potencia para la integración del sistema de almacenamiento de energía híbrido con el fin de suavizar el perfil de potencia de la red, considerando eventos de saturación y condiciones de aislamiento de red.

#### **RESUMEN** (en inglés)

The objective of this thesis is the development of control systems adapted to multiport power converters for grid integration of distributed resources, in order to consider a paradigm shift in the design of control systems for power converters, from power units with a rigid and specific design for each centralized generation application to alternative implementations with an adaptive and generic design that can be integrated in multiple distributed generation applications.

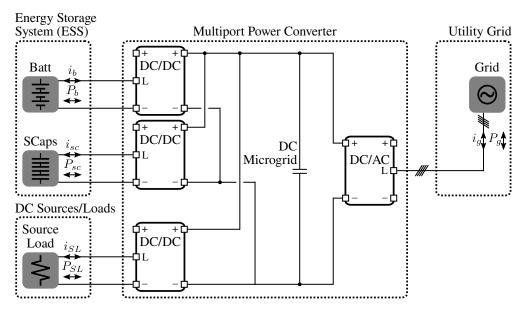

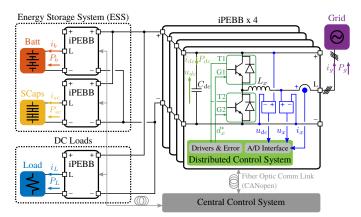

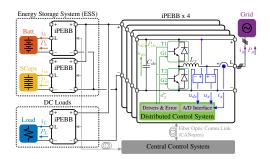

The work developed focuses on the exploitation of a modular power converter formed from basic power cells, in order to propose a multiport configuration that allows the interconnection of power units of different nature, the integration with the electrical grid and the support of energy storage systems.

Therefore, initially, a review of the different power cell designs is performed to determine the most suitable option for the implementation of the converter.

Once the converter configuration has been selected, mathematical modeling in state space is carried out from the large-signal average model. The model is suitable for conducting dynamic analysis to understand its behavior and later to be used in the control system design. This mathematical model is validated by comparison with the converter switching model, obtaining equivalent results with the absence of the high-frequency ripple resulting from the switching.

Using the information acquired from the mathematical model, the requirements to determine the most suitable distributed control system for the operation of the multiport modular power converter are established.

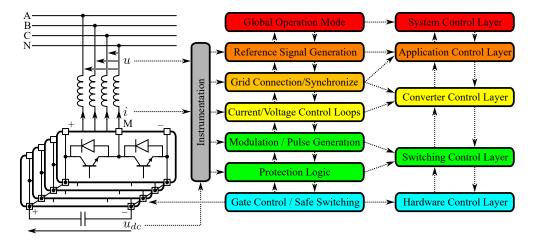

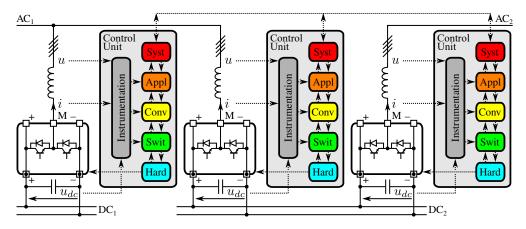

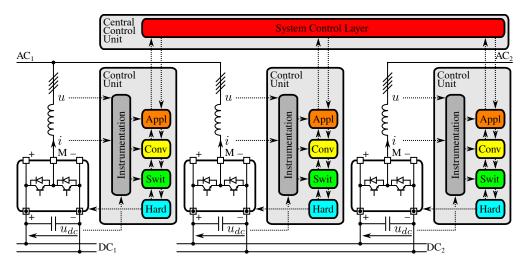

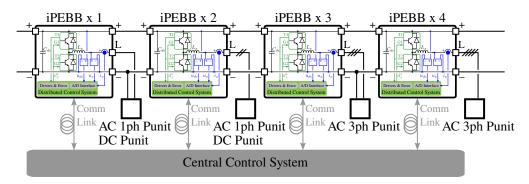

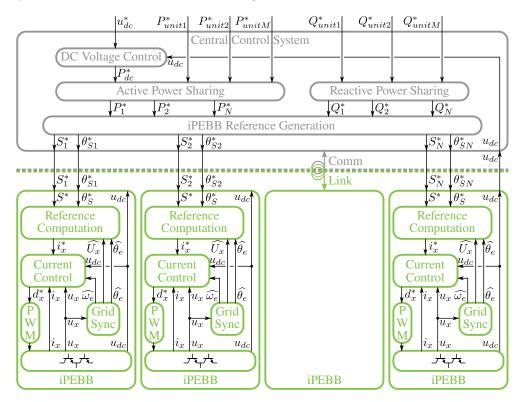

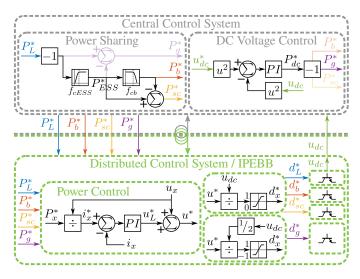

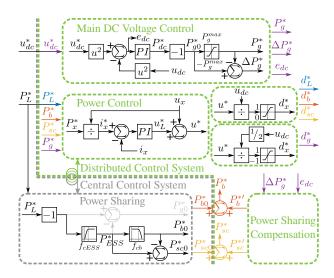

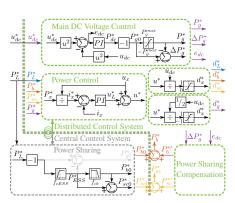

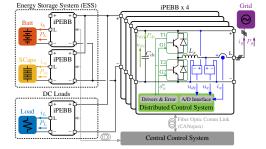

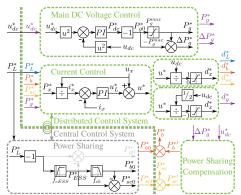

At this point, a distributed control architecture for the multiport converter is proposed. This architecture is developed to take into account the modular configuration of the converter, so it follows a hierarchical structure formed by several distributed controllers, which manage the control tasks at power cell level, subordinated to a central controller, which manages the control tasks at system and application level.

The distributed controllers in charge of the power cells are designed to follow a common and adaptable structure, in order to enable the integration of different power units in the converter without major modifications in the control architecture.

Afterwards, the central controller is integrated into an embedded system based on a generalpurpose microprocessor, providing versatility, scalability and computational capacity at the same time.

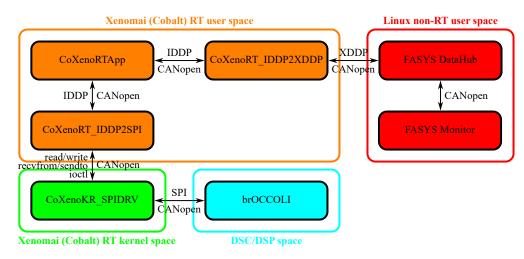

The microprocessor is handled by a Linux operating system to take advantage of its wide support and facilitate the execution of non-critical auxiliary tasks, together with a real-time extension that enables the execution of critical and firm real-time control tasks.

The validation of the embedded system for its integration into the control system is determined by analyzing the correct execution of tasks in real time, demonstrating a deterministic operation

#### Universidad de Oviedo

with a negligible number of missed deadlines.

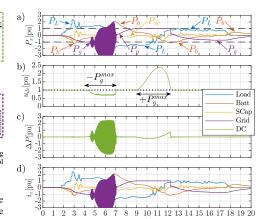

Finally, an application based on the use of a multiport converter controlled by the proposed distributed control system is developed and implemented.

This application allows the operation of a bidirectional power unit following a given power profile, under maximum grid power constraints, and with the support of a hybrid energy storage system.

For this purpose, a power sharing algorithm is implemented for the integration of the hybrid energy storage system in order to smooth the grid power profile, considering saturation events and islanding conditions.

SR. PRESIDENTE DE LA COMISIÓN ACADÉMICA DEL PROGRAMA DE DOCTORADO EN ENERGÍA Y CONTROL DE PROCESOS

### Resumen

El objetivo de esta tesis es el desarrollo de sistemas de control adaptados a convertidores de potencia multipuerto para integración en red de recursos distribuidos. El estudio pretende dar respuesta a un cambio en el paradigma en el diseño de sistemas de control para convertidores de potencia, desde unidades de potencia con un diseño rígido y específico para cada aplicación de generación centralizada hacia implementaciones alternativas con un diseño adaptativo y genérico que pueda ser integrado en múltiples aplicaciones de generación distribuida.

El trabajo desarrollado se centra en la explotación de un convertidor de potencia modular formado a partir de celdas básicas de potencia, a fin de proponer una configuración multipuerto que permita la interconexión de unidades de potencia de diversa naturaleza, la integración con la red eléctrica y el apoyo de sistemas de almacenamiento de energía. Por tanto, inicialmente, se realiza una revisión de los diferentes diseños de celdas de potencia para determinar la opción más adecuada para la implementación del convertidor.

Una vez seleccionada la configuración del convertidor, se lleva a cabo el modelado matemático del mismo en espacio de estados a partir del modelo promediado de gran señal. El modelo es adecuado para realizar el análisis dinámico del sistema a fin de comprender su comportamiento y posteriormente ser utilizado en el diseño del sistema de control. Este modelo matemático es validado mediante la comparación con el modelo conmutado del convertidor, obteniéndose unos resultados equivalentes con la ausencia del rizado de alta frecuencia derivado de la conmutación de los interruptores de potencia. Utilizando la información adquirida a partir del modelo matemático, se establecen los requerimientos para determinar el sistema de control distribuido más adecuado para la explotación del convertidor de potencia modular multipuerto.

Llegados a este punto, se propone una arquitectura de control distribuido para el convertidor multipuerto. Esta arquitectura se desarrolla para tener en cuenta la configuración modular del convertidor, por lo que sigue una estructura jerárquica formada por diversos controladores distribuidos, los cuales gestionan las tareas de control a nivel de celda de potencia, supeditados a un controlador central, el cual gestiona las tareas de control a nivel de sistema y aplicación. Los controladores distribuidos a cargo de las celdas de potencia son diseñados para seguir una estructura común y adaptable, con el fin de habilitar la integración de diferentes unidades de potencia en el convertidor sin grandes modificaciones en la arquitectura de control.

Posteriormente, se integra el controlador central en un sistema embebido basado en un microprocesador de propósito general, proporcionando versatilidad, escalabilidad y capacidad computacional al mismo tiempo. El microprocesador se maneja mediante un sistema operativo Linux para aprovechar su gran soporte y facilitar la ejecución de tareas auxiliares no críticas, junto con una extensión en tiempo real que habilita la ejecución de tareas de control críticas y con restricciones firmes de tiempo real. La validación del sistema embebido para su integración en el sistema de control se determina analizando la correcta ejecución de tareas en tiempo real, demostrando una operación determinista con un número despreciable de incumplimientos de plazos.

Finalmente, se desarrolla e implementa una aplicación basada en el uso de un convertidor multipuerto controlado mediante el sistema de control distribuido propuesto. Dicha aplicación permite la operación de una unidad de potencia bidireccional siguiendo un determinado perfil de potencia, bajo restricciones de potencia máxima de red, y con el apoyo de un sistema de almacenamiento de energía híbrido. Para este propósito, se implementa un algoritmo de reparto de potencia para la integración del sistema de almacenamiento de energía híbrido con el fin de suavizar el perfil de potencia de la red, considerando eventos de saturación y condiciones de aislamiento de red.

### Abstract

The objective of this thesis is the development of control systems adapted to multiport power converters for grid integration of distributed resources, in order to consider a paradigm shift in the design of control systems for power converters, from power units with a rigid and specific design for each centralized generation application to alternative implementations with an adaptive and generic design that can be integrated in multiple distributed generation applications.

The work developed focuses on the exploitation of a modular power converter formed from basic power cells, in order to propose a multiport configuration that allows the interconnection of power units of different nature, the integration with the electrical grid and the support of energy storage systems. Therefore, initially, a review of the different power cell designs is performed to determine the most suitable option for the implementation of the converter.

Once the converter configuration has been selected, mathematical modeling in state space is carried out from the large-signal average model. The model is suitable for conducting dynamic analysis to understand its behavior and later to be used in the control system design. This mathematical model is validated by comparison with the converter switching model, obtaining equivalent results with the absence of the high-frequency ripple resulting from the switching. Using the information acquired from the mathematical model, the requirements to determine the most suitable distributed control system for the operation of the multiport modular power converter are established.

At this point, a distributed control architecture for the multiport converter is proposed. This architecture is developed to take into account the modular configuration of the converter, so it follows a hierarchical structure formed by several distributed controllers, which manage the control tasks at power cell level, subordinated to a central controller, which manages the control tasks at system and application level. The distributed controllers in charge of the power cells are designed to follow a common and adaptable structure, in order to enable the integration of different power units in the converter without major modifications in the control architecture.

Afterwards, the central controller is integrated into an embedded system based on a general-purpose microprocessor, providing versatility, scalability and computational capacity at the same time. The microprocessor is handled by a Linux operating system to take advantage of its wide support and facilitate the execution of non-critical auxiliary tasks, together with a real-time extension that enables the execution of critical and firm real-time control tasks. The validation of the embedded system for its integration into the control system is determined by analyzing the correct execution of tasks in real time, demonstrating a deterministic operation with a negligible number of missed deadlines.

Finally, an application based on the use of a multiport converter controlled by the proposed distributed control system is developed and implemented. This application allows the operation of a bidirectional power unit following a given power profile, under maximum grid power constraints, and with the support of a hybrid energy storage system. For this purpose, a power sharing algorithm is implemented for the integration of the hybrid energy storage system in order to smooth the grid power profile, considering saturation events and islanding conditions.

Х

# Abbreviations and acronyms

| $1 \mathrm{ph}$        | Single-Phase                      |

|------------------------|-----------------------------------|

| 3L                     | Three-Level                       |

| $3\mathrm{ph}$         | Three-Phase                       |

| 5L                     | Five-Level                        |

| $\mathbf{AC}$          | Alternating Current               |

| ACK                    | Acknowledge                       |

| A/D                    | Analog-To-Digital                 |

| ANN                    | Artificial Neural Network         |

| ANPC                   | Active NPC                        |

| API                    | Application Programming Interface |

| $C^{3}S$               | Common Cross-Connected Stage      |

| CAES                   | Compressed Air Energy Storage     |

| CAN                    | Controller Area Network           |

| CAN FD                 | CAN Flexible Data-Rate            |

| $\mathbf{C}\mathbf{M}$ | Compute Module                    |

| CNT                    | Controllable Network Transformer  |

| CRC                    | Cyclic Redundancy Check           |

| CPU                    | Central Processing Unit           |

| DC                     | Direct Current                    |

| DPS                    | Distribution Power System         |

| DRC                    | Direct RC                         |

| DSP                    | Digital Signal Processor          |

| DVC                    | Direct Voltage Control            |

| ESS                    | Energy-Storage System             |

|                        |                                   |

#### XII

| EtherCAT       | Ethernet for Control Automation Technology |

|----------------|--------------------------------------------|

| FACTS          | Flexible AC Transmission System            |

| $\mathbf{FC}$  | Fuel Cell                                  |

| FESS           | Flywheel ESS                               |

| FFT            | Fast Fourier Transform                     |

| FLC            | Fuzzy Logic Control                        |

| $\mathbf{FLL}$ | Frequency Locked Loop                      |

| GPU            | Graphics Processing Unit                   |

| GUI            | Graphical User Interface                   |

| HAL            | Hardware Abstraction Layer                 |

| HDMI           | High-Definition Multimedia Interface       |

| HES            | High-Energy Storage                        |

| HESS           | Hybrid ESS                                 |

| HMI            | Human-Machine Interface                    |

| HPF            | High-Pass Filter                           |

| HPS            | High-Power Storage                         |

| HV             | High Voltage                               |

| $I^2C$         | Inter-Integrated Circuit                   |

| IC             | Integrated Circuit                         |

| IDE            | Integrated Development Environment         |

| IMU            | Impedance Measurement Unit                 |

| IoT            | Internet of Things                         |

| IP             | Internet Protocol                          |

| IPC            | Inter-Process Communication                |

| iPEBB          | Intelligent PEBB                           |

| IRQ            | Interrupt Request                          |

| $\mathbf{LC}$  | Inductor-Capacitor                         |

| LPF            | Low-Pass Filter                            |

| LV             | Low Voltage                                |

| $\mathbf{MF}$  | Multi-Fed                                  |

| MMC            | Modular Multilevel Converter               |

| MNPC           | Mixed-Voltage NPC                          |

| MPC            | Model Predictive Control                   |

|                |                                            |

| $\mathbf{MV}$  | Medium Voltage                          |

|----------------|-----------------------------------------|

| NMT            | Network Management                      |

| NPC            | Neutral-Point Clamped                   |

| OS             | Operating System                        |

| OSI            | Open Systems Interconnection            |

| PCB            | Printed Circuit Board                   |

| PCC            | Point of Common Coupling                |

| PDO            | Process Data Object                     |

| PEBB           | Power Electronics Building Block        |

| PET            | Power Electronic Transformer            |

| PFC            | Power Factor Correction                 |

| PI             | Proportional-Integral                   |

| PLL            | Phase-Locked Loop                       |

| POSIX          | Portable Operating System Interface     |

| $\mathbf{PR}$  | Proportional-Resonant                   |

| PSH            | Pumped Storage Hydropower               |

| PSO            | Particle Swarm Optimization             |

| PWM            | Pulse-Width Modulation                  |

| $\mathbf{QSG}$ | Quadrature Signal Generator             |

| QVC            | Quadratic Voltage Control               |

| RAM            | Random Access Memory                    |

| RBC            | Rule-Based Control                      |

| RC             | Repetitive Controller                   |

| RPi            | Raspberry Pi                            |

| $\mathbf{RT}$  | Real-Time                               |

| RTR            | Remote Transmission Request             |

| SDO            | Service Data Object                     |

| SFLA           | Shuffled Frog-Leaping Algorithm         |

| SOGI           | Second-Order Generalized Integrator     |

| SMC            | Sliding Mode Control                    |

| SMES           | Superconducting Magnetic Energy Storage |

| SOC            | State Of Charge                         |

| SPI            | Serial Peripheral Interface             |

#### XIV

| STATCOM        | Static Synchronous Compensator                  |

|----------------|-------------------------------------------------|

| $\mathbf{SVR}$ | Second Voltage Regulation                       |

| SYNC           | Synchronization                                 |

| TCP            | Transmission Control Protocol                   |

| TEES           | Thermo-Electric Energy Storage                  |

| THD            | Total Harmonic Distorsion                       |

| UART           | Universal Asynchronous Receiver-Transmitter     |

| UI             | User Interface                                  |

| USB            | Universal Serial Bus                            |

| VCD            | Virtual Capacitance Droop                       |

| VRD            | Virtual Resistance Droop                        |

| VSC            | Voltage Source Converter                        |

| WCA            | Water Cycle Algorithm                           |

| WiMAX          | Worldwide Interoperability for Microwave Access |

| ZCT            | Zero-Current Transition                         |

| ZPS            | Zero-Phase-Shift                                |

| $\mu P$        | Micro-Processor                                 |

## Contents

|   | Agra | adecimi                 | entos        |           |                    |        |        |      |      |    | • • | • |     |    |  |  | V  |

|---|------|-------------------------|--------------|-----------|--------------------|--------|--------|------|------|----|-----|---|-----|----|--|--|----|

|   | Resi | sumen                   |              |           |                    |        |        |      |      |    |     |   | VII |    |  |  |    |

|   | Abst | $\operatorname{stract}$ |              |           |                    |        |        |      |      |    |     |   |     | IX |  |  |    |

|   | Abb  | reviatio                | ns and acro  | onyms     |                    |        |        |      |      | •  |     |   |     |    |  |  | XI |

| 1 | Intr | oducti                  | on           |           |                    |        |        |      |      |    |     |   |     |    |  |  | 1  |

|   | 1.1  | Backg                   | round and i  | motivat   | tion .             |        |        |      |      |    |     |   |     |    |  |  | 1  |

|   | 1.2  | Thesis                  | objectives   |           |                    |        |        |      |      |    |     |   |     |    |  |  | 4  |

|   | 1.3  | Thesis                  | contributio  | ons       |                    |        |        |      |      |    |     |   |     |    |  |  | 5  |

|   | 1.4  | Thesis                  | publication  | ns        |                    |        |        |      |      |    |     |   |     |    |  |  | 6  |

|   |      | 1.4.1                   | Peer-revie   | wed joı   | ırnal p            | paper  | з.     |      |      |    |     |   |     |    |  |  | 6  |

|   |      | 1.4.2                   | Peer-revie   | wed co    | nferen             | .ce pa | pers   |      |      |    |     |   |     |    |  |  | 6  |

|   | 1.5  | Thesis                  | software w   | vith inte | ellectu            | ual pr | opert  | y ri | ghts |    |     |   |     |    |  |  | 8  |

|   | 1.6  | Thesis                  | outline      |           |                    |        | • •    |      |      | •  |     | • |     |    |  |  | 9  |

| 2 | Lite | erature                 | review a     | nd sta    | te of <sup>,</sup> | the a  | art    |      |      |    |     |   |     |    |  |  | 11 |

|   | 2.1  | Introd                  | uction       |           |                    |        |        |      |      |    |     |   |     |    |  |  | 11 |

|   | 2.2  | Modul                   | ar power co  | onverte   | rs                 |        |        |      |      |    |     |   |     |    |  |  | 12 |

|   |      | 2.2.1                   | Power Ele    | ctronic   | s Buile            | ding   | Blocl  | к (Р | EBI  | 3) |     |   |     |    |  |  | 12 |

|   |      | 2.2.2                   | Converter    | configu   | uratior            | ns     |        |      |      |    |     |   |     |    |  |  | 17 |

|   |      | 2.2.3                   | Proposed     | applica   | tions              |        |        |      |      |    |     |   |     |    |  |  | 21 |

|   | 2.3  | Distrik                 | outed contro | ol in po  | ower c             | onver  | rters  |      |      |    |     |   |     |    |  |  | 23 |

|   |      | 2.3.1                   | Distribute   | d contr   | ol stru            | uctur  | е.     |      |      |    |     |   |     |    |  |  | 23 |

|   |      | 2.3.2                   | Distribute   | d contr   | ol imp             | pleme  | entati | ions |      |    |     |   |     |    |  |  | 24 |

|   |      |                         | 2.3.2.1 N    | Multi-a   | gent c             | ontro  | ol.    |      |      |    |     |   |     |    |  |  | 25 |

|   |      |                | 2.3.2.2 Hierarchical control                           | 26       |

|---|------|----------------|--------------------------------------------------------|----------|

|   |      | 2.3.3          | Communications protocols                               | 27       |

|   |      | 2.3.4          | Control reconfiguration                                | 30       |

|   | 2.4  | Real-7         | Гіте OSes                                              | 30       |

|   |      | 2.4.1          | Native RTOSes                                          | 32       |

|   |      | 2.4.2          | Real-time extensions for standard OSes                 | 32       |

|   |      | 2.4.3          | System performance and control applications            | 33       |

|   | 2.5  | Power          | sharing in multiport power converters                  | 33       |

|   |      | 2.5.1          | Hybrid Energy-Storage Systems (HESSs)                  | 34       |

|   |      | 2.5.2          | Power sharing techniques                               | 38       |

|   | 2.6  | Summ           | hary and research opportunities                        | 39       |

|   | Refe | erences        |                                                        | 41       |

| 9 | D    | •              | and deliver and desire for the Intelligent DEDD (DEDD) | • 1      |

| 3 |      |                |                                                        | 51       |

|   | 3.1  |                |                                                        | 51<br>52 |

|   | 3.2  | 3.2.1          | 6                                                      | 52<br>52 |

|   |      | 3.2.1<br>3.2.2 |                                                        | 52<br>54 |

|   |      | 3.2.2          | · ·                                                    | 54<br>56 |

|   |      |                |                                                        | 57       |

|   |      |                |                                                        | 60       |

|   |      |                |                                                        | 65       |

|   |      |                |                                                        | 68       |

|   |      | 3.2.3          |                                                        | 71       |

|   |      | 3.2.3          |                                                        | 71<br>71 |

|   |      | 3.2.4          |                                                        | 73       |

|   | 3.3  |                | -                                                      | 73       |

|   | 5.5  | 3.3.1          |                                                        | 73<br>74 |

|   |      | 3.3.2          |                                                        | 76       |

|   |      | 0.0.2          | -                                                      | 76       |

|   |      |                | -                                                      | 77       |

|   |      |                | -                                                      | 78       |

|   |      | 3.3.3          |                                                        | 79       |

|   |      | 5.5.0          |                                                        |          |

|   |      | 3.3.4   | Reference computation                                                        | 80  |

|---|------|---------|------------------------------------------------------------------------------|-----|

|   | 3.4  | Power   | converter implementation                                                     | 81  |

|   |      | 3.4.1   | AC/DC power converter                                                        | 81  |

|   |      | 3.4.2   | DC/DC power converter                                                        | 82  |

|   | 3.5  | Distril | buted control structure                                                      | 82  |

|   | 3.6  | Conclu  | usions                                                                       | 84  |

|   | Refe | rences  |                                                                              | 84  |

|   |      | 1.      |                                                                              |     |

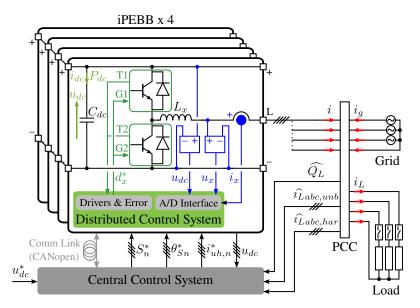

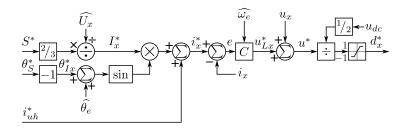

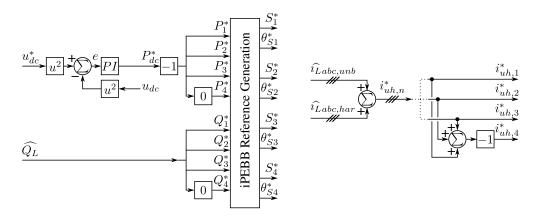

| 4 |      | •       | and development of a modular distributed digital control<br>atform           | 87  |

|   | 4.1  | -       | uction                                                                       | 87  |

|   | 4.2  |         | l structure                                                                  | 89  |

|   | 4.3  | Develo  | oppment of the central control in a general-purpose $\mu P$ with RT          |     |

|   |      | capabi  |                                                                              | 91  |

|   |      | 4.3.1   | Analysis of the DC voltage control loop $\hfill \ldots \ldots \ldots \ldots$ | 91  |

|   |      | 4.3.2   | Active and reactive power sharing                                            | 92  |

|   |      | 4.3.3   | iPEBB reference generation                                                   | 93  |

|   | 4.4  | •       | sis of the communication bus between central and distributed con-            |     |

|   |      |         | s                                                                            | 94  |

|   |      | 4.4.1   | Development of the higher-layer protocol                                     | 94  |

|   |      | 4.4.2   | Selection of the physical and data link layers                               | 96  |

|   | 4.5  |         | ol issues                                                                    | 97  |

|   |      | 4.5.1   | Communication channel                                                        | 97  |

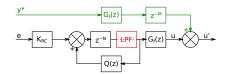

|   |      | 4.5.2   | Reference reconstruction                                                     | 98  |

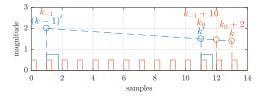

|   |      | 4.5.3   | Reference differentiability correction                                       | 99  |

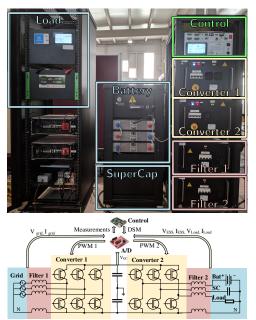

|   | 4.6  |         | g setup                                                                      |     |

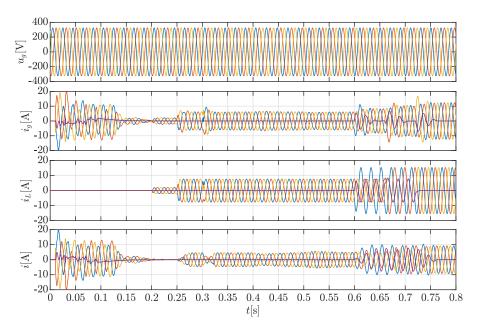

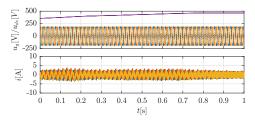

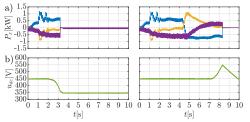

|   | 4.7  | Simula  | ation results                                                                |     |

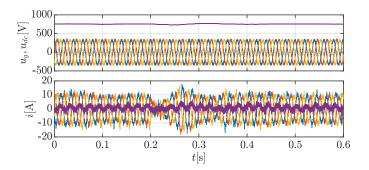

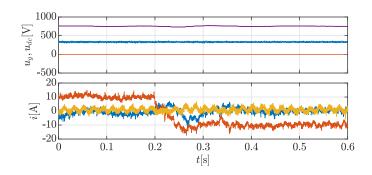

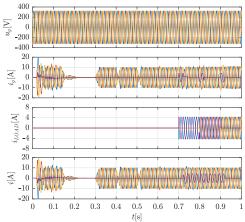

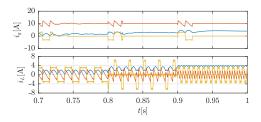

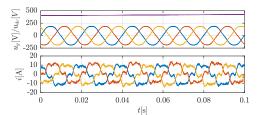

|   |      | 4.7.1   | Reactive power management and frequency shifts                               |     |

|   |      | 4.7.2   | Connection of local linear loads                                             |     |

|   |      | 4.7.3   | Connection of local non-linear loads                                         | 105 |

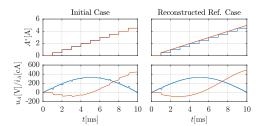

|   |      | 4.7.4   | Effect of reference reconstruction and differentiability correction          | 106 |

|   |      | 4.7.5   | Error from communication delays                                              | 107 |

|   | 4.8  | -       | imental results                                                              |     |

|   | 4.9  | Conclu  | usions                                                                       | 113 |

|   | Refe | rences  |                                                                              | 113 |

| 5 | Distributed control deployment in a digital platform based on a $\mu P$ under RTOS 115 |          |                                                                                                                                         |  |  |  |  |  |  |  |

|---|----------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|   | 5.1                                                                                    | Introd   | uction                                                                                                                                  |  |  |  |  |  |  |  |

|   | 5.2                                                                                    | Select   | ion of the hardware and low-level software                                                                                              |  |  |  |  |  |  |  |

|   |                                                                                        | 5.2.1    | Hardware equipment                                                                                                                      |  |  |  |  |  |  |  |

|   |                                                                                        | 5.2.2    | Operating System                                                                                                                        |  |  |  |  |  |  |  |

|   |                                                                                        | 5.2.3    | Real-Time extension                                                                                                                     |  |  |  |  |  |  |  |

|   |                                                                                        | 5.2.4    | Final implementation and software configuration                                                                                         |  |  |  |  |  |  |  |

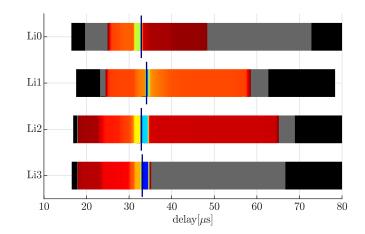

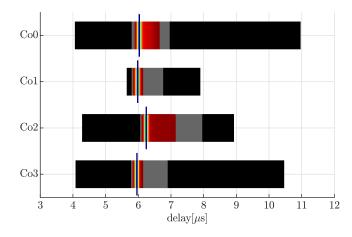

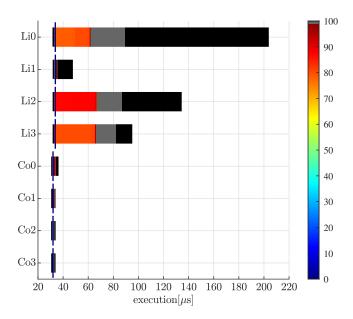

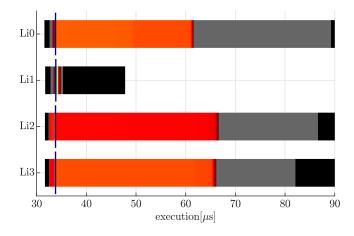

|   | 5.3                                                                                    | Valida   | tion of the RT operation $\ldots \ldots 122$ |  |  |  |  |  |  |  |

|   | 5.4                                                                                    | Archit   | becture of the developed software $\ldots \ldots 133$                    |  |  |  |  |  |  |  |

|   | 5.5                                                                                    | Concl    | usions                                                                                                                                  |  |  |  |  |  |  |  |

|   | Refe                                                                                   | erences  |                                                                                                                                         |  |  |  |  |  |  |  |

| 6 | Ana                                                                                    | alvsis c | of power sharing in multiport DC/DC/AC converters based                                                                                 |  |  |  |  |  |  |  |

| 0 |                                                                                        | PEBB     |                                                                                                                                         |  |  |  |  |  |  |  |

|   | 6.1                                                                                    | Introd   | uction                                                                                                                                  |  |  |  |  |  |  |  |

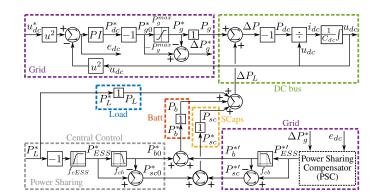

|   | 6.2                                                                                    | Power    | sharing issues                                                                                                                          |  |  |  |  |  |  |  |

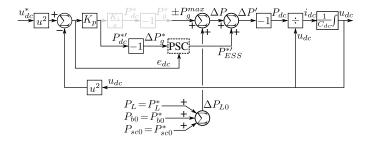

|   | 6.3                                                                                    | Comp     | ensation techniques                                                                                                                     |  |  |  |  |  |  |  |

|   |                                                                                        | 6.3.1    | Direct power reference compensation                                                                                                     |  |  |  |  |  |  |  |

|   |                                                                                        | 6.3.2    | Auxiliary DC voltage control                                                                                                            |  |  |  |  |  |  |  |

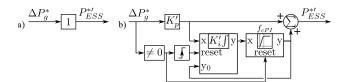

|   |                                                                                        | 6.3.3    | Enhanced power reference compensation                                                                                                   |  |  |  |  |  |  |  |

|   |                                                                                        | 6.3.4    | Operation in islanding mode                                                                                                             |  |  |  |  |  |  |  |

|   |                                                                                        | 6.3.5    | Summary                                                                                                                                 |  |  |  |  |  |  |  |

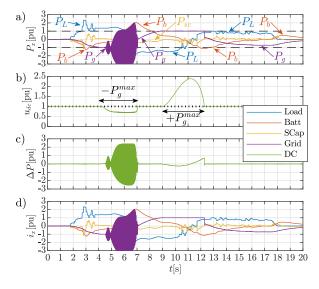

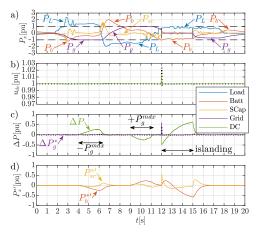

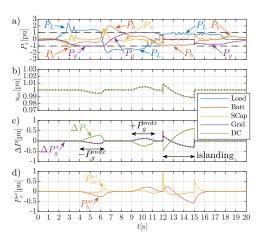

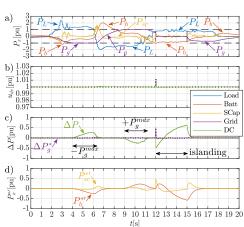

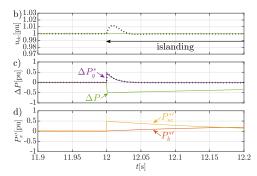

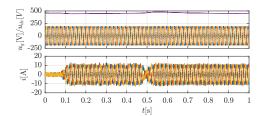

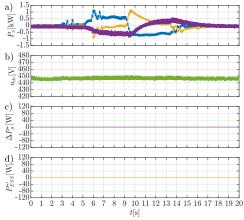

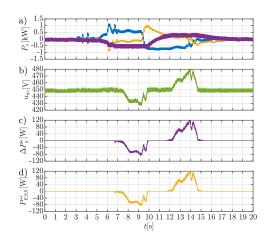

|   | 6.4                                                                                    | Simula   | ation results $\ldots \ldots 154$     |  |  |  |  |  |  |  |

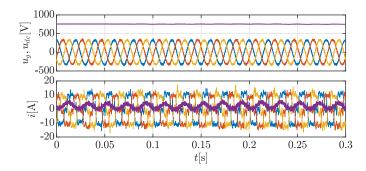

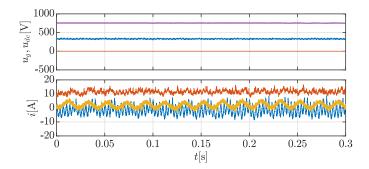

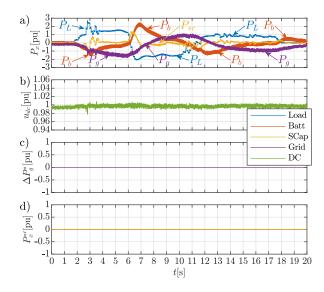

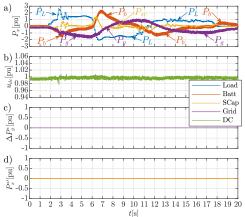

|   |                                                                                        | 6.4.1    | Ideal case                                                                                                                              |  |  |  |  |  |  |  |

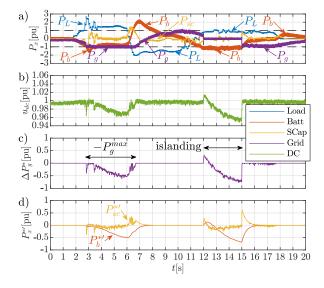

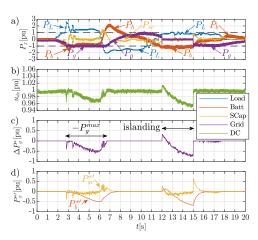

|   |                                                                                        | 6.4.2    | Direct power reference compensation                                                                                                     |  |  |  |  |  |  |  |

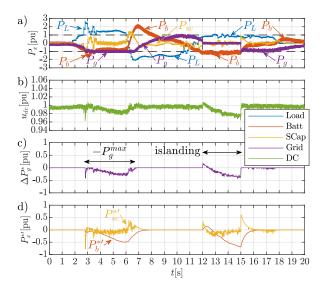

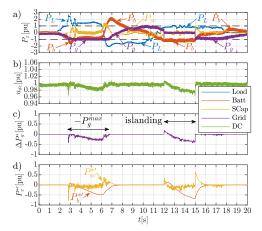

|   |                                                                                        | 6.4.3    | Auxiliary DC voltage control                                                                                                            |  |  |  |  |  |  |  |

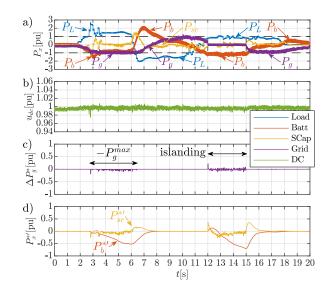

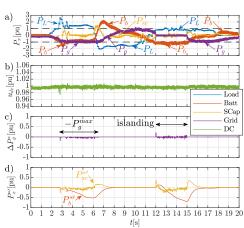

|   |                                                                                        | 6.4.4    | Enhanced power reference compensation                                                                                                   |  |  |  |  |  |  |  |

|   |                                                                                        | 6.4.5    | Summary                                                                                                                                 |  |  |  |  |  |  |  |

|   |                                                                                        | 6.4.6    | Effect of power measurement errors and communication delays . 161                                                                       |  |  |  |  |  |  |  |

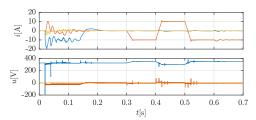

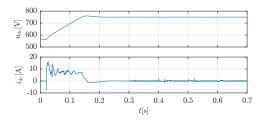

|   | 6.5                                                                                    | Exper    | imental results                                                                                                                         |  |  |  |  |  |  |  |

|   | 6.6                                                                                    | Concl    | usions                                                                                                                                  |  |  |  |  |  |  |  |

|   | References                                                                             |          |                                                                                                                                         |  |  |  |  |  |  |  |

| 7            | Cor | clusions and future work                                                     | 175  |

|--------------|-----|------------------------------------------------------------------------------|------|

|              | 7.1 | Conclusiones                                                                 | 175  |

|              | 7.2 | Conclusions                                                                  | 176  |

|              | 7.3 | Future work                                                                  | 178  |

| $\mathbf{A}$ | Jou | rnal publications                                                            | 179  |

|              | A.1 | Compensation Alternatives for Power Sharing in Multi-Port Converters         | 180  |

| в            | Cor | ference publications                                                         | 197  |

|              | B.1 | Distributed Control Alternatives of Modular Converters for Hybrid Microgrids | 198  |

|              | ЪЭ  | Componention Alternatives for Down Shaving in Converters for Microsofie      | -207 |

B.2 Compensation Alternatives for Power Sharing in Converters for Microgrids207

#### XIX

### Chapter 1

## Introduction

#### 1.1 Background and motivation

Traditionally, the generation of electrical energy was carried out in large plants in a centralized manner, in order to take advantage of the characteristics of fossil and nuclear fuels. This is due to the fact that the thermal processes produced with this type of technology obtain better performance in conjunction with a larger plant size. In addition, the extraction of the raw material to carry out the combustion/fission process is located in those areas where there is availability, which further encourages centralization.

Nevertheless, with the course of the last years, there has been an increasing development of renewable energies, which are based on energy sources with different characteristics from the traditional ones. These renewable energy sources (sun, wind) are considered virtually inexhaustible and are available in all places to a greater or lesser extent. Due to the integration of this type of sources in the energy mix, there is an evolution from a centralized model to an increasingly distributed model. In this model, the aim is to generate electricity close to where it will be consumed, in order to make it more accessible, favour self-consumption, reduce distribution costs and allow operation in the event of disconnections from the electrical grid.

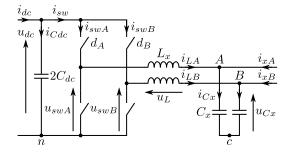

All this entails a modification of the power converter topologies in order to adapt to distributed generation and take advantage of all its benefits. Traditional power converters are specifically designed to fulfill a particular purpose in the most efficient way and, therefore, they are not very customizable. In a centralized and rigid model of electricity generation, whose requirements are well known and little modifiable, this type of converter allows cost savings. However, taking into account that their adaptation capacity is reduced, it makes them less suitable for a distributed generation model, where generation requirements are more changeable. This is where modular power converters come into play. A modular power converter consists of a series of power cells that joined together and configured in a certain way carry out a certain purpose. Thus, depending on the arrangement of the cells and the programming implemented in each of them, the converter can vary its behavior and adapt to the needs of each moment. Therefore, this type of converter provides the advantage of having great flexibility, since a repositioning and reprogramming of these cells would allow you to vary its purpose without further cost. This feature is appealing to carry out the development of distributed generation, due to the continuous evolution it is undergoing.

In addition to flexibility, the use of power cells to form the modular converter provides other advantages. On the one hand, it facilitates the scalability of the system as it allows to increase the voltage and current rating of the converter by adding more cells in series or parallel. On the other hand, the reliability of the converter can be improved by adding redundant cells to the existing ones, which could hot-swap one of the main cells in case there is a failure in them.

Renewable energy sources are considered to be inexhaustible but some of them cannot guarantee uninterrupted power generation due to their dependence on resources with variable availability. This is the case for any generator based on solar or wind energy, as the sun and wind are influenced by weather, seasonal and climatic conditions. Therefore, the controllability of the power generated from these types of sources is limited and subject to environmental conditions. This phenomenon is even more aggravated when power consumption profiles are taken into account, since consumption peaks do not always coincide with the most favorable sun and wind conditions.

To mitigate the problem, the development and introduction of energy storage devices in power systems is being encouraged, with a wide range of possibilities available: electrochemical (batteries), electrical (supercapacitors), kinetic (flywheels), gravitational (pumping). This way, surplus power generation can be stored in periods of higher supply or lower demand (off-peak hours) for use in periods of lower supply or higher demand (peak hours). Therefore, the integration of all the power devices belonging to a distributed generation system entails the need for power converters with multiple connection points to manage all the sources and loads, as well as auxiliary energy storage elements to improve system performance.

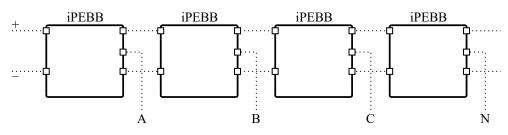

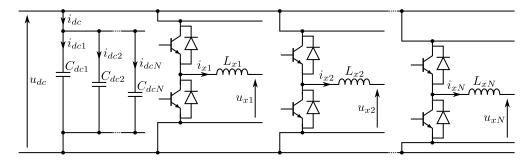

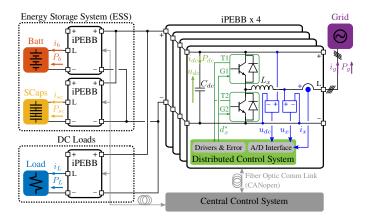

At this point, the concept of the multiport power converter arises, a device that provides multiple connection ports to interconnect various power units and integrate them into the electrical grid. Following a modular development, a multiport power converter can be formed by connecting a specific number of power cells depending on the number of distributed resources to be integrated into the grid. Therefore, unlike more conventional converter topologies, the control system of a multiport converter requires a high number of inputs/outputs to be able to interact with all the power cells that make up the converter and, in addition, a large computational capacity necessary to ensure the correct execution of the control algorithms within specified time ranges.

To address this issue, a single high-performance digital controller can be used to provide a sufficient number of hardware resources to handle the number of inputs and outputs required by the application. In this way, the entire control algorithm would be implemented in this device, taking care of the complete management of the multiport power converter. However, this solution conflicts with the modularity concept put forward for the integration of distributed resources, since the integration of the control system in a single device hinders scalability, especially in terms of having enough resources available to handle all the required inputs and outputs. While it is true that the digital controller could be oversized to meet future needs and facilitate the scalability of the converter, this would imply a non-optimal design with limitations on the maximum number of inputs and outputs.

Following a modular design, it is possible to distribute part of the control system within each of the power cells that form the modular multiport converter, by integrating cost-effective digital controllers within each of the cells for the implementation of specific control algorithms for autonomous management. This means that the highperformance digital controller of the control system is freed from having a large number of inputs and outputs, which are now distributed within the local cell controllers, taking care of coordinating the operation of the cells with a global approach at the converter level. Thus, greater scalability is achieved for the multiport converter, making it easier to upgrade the converter for the integration of new power units.

The motivation for this work arises from the lack of distributed control systems for the management of modular power converters based on power cells. For this purpose, the proposal in this thesis is to transform the power cell into an intelligent one by introducing a local control system, allowing self-management for the internal control variables. Improving the performance of the power cell in this respect facilitates the development of multiport converters capable of handling multiple power units of different nature without requiring bespoke hardware designs for the central control system. This could potentially bring an improved integration of distributed generation systems with hybrid energy storage systems.

However, the implementation of a multiport converter based on intelligent power cells with a distributed control system involves a number of challenges that must be considered. First, it is desirable to have a single power cell implementation that is capable of configuring all power conversions required by the multiport converter through cell replication. Moreover, the development of a distributed control system requires the integration of a digital controller for each cell, which must be conveniently programmed to perform the local autonomous control. Local control must be designed to be versatile enough to enable the use of the cell for different power topologies.

In addition, the introduction of multiple connection ports to handle as many power units as necessary places increasing requirements on the number of inputs and outputs managed by the control system of the converter. Since these inputs/outputs are distributed among the local controllers of the power cells, the control system becomes more complex to optimally operate the resources available in the cells. Thus, although the power cells have their own controller for self-management, a higher control layer is necessary to synchronize all of them for establishing the global operation of the converter. This results in ever-increasing computational requirements and the need for high performance communication channels, issues addressed during the development of the thesis.

#### 1.2 Thesis objectives

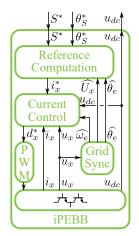

The main objective of this work is the development of a distributed control system architecture for the operation of modular power converters formed from the combination of multiple power cells, with the final purpose of controlling multiport converters capable of integrating distributed resources. For this purpose, the distributed control system is designed to manage power converter topologies based on the interconnection of several units of an unique power cell which consists of a specific set of active and passive elements necessary for the utilization of the cell in different power conversion scenarios. In addition, to meet the requirements of different applications, a programmable control system will be integrated into the cell itself, providing it with greater intelligence and adaptability. In order to achieve all above, the following objectives are defined:

- I. A state-of-the-art review related to the thesis motivation and the corresponding objectives, covering the following topics:

- Review of modular power converters based on the development of a power cell, considering different converter configurations and applications where this concept is applied.

- Review of the distributed control approach in power converters, focusing on the structure in layers of this type of control, the different implementations available in literature and the communication protocols used to interconnect the control agents.

- Review of different implementations of Real-Time Operating Systems, which can be used for the development of a digital controller in a Micro-Processor to provide enhanced support and connectivity.

- Review of power sharing in multiport converters for the integration of multiple power units to take advantage of their specific characteristics. The study focuses on the exploitation of hybrid energy storage systems.

- II. Dynamic modeling of a power cell with the necessary power and control devices for building different configurations of modular power converters by making diverse power cell arrangements, depending on the requirements of the application.

- III. Development of a distributed digital control system platform capable of handling modular power converters. It is based on a versatile control structure that allows its adequate operation for different operating cases.

- IV. Analysis of the latency in a controller based on a open-source Real-Time Operating System to validate the implementation of a digital controller in a generalpurpose Micro-Processor.

- V. Implementation of a multiport power converter operated by a distributed control system for an application based on multiple energy-storage devices and power loads/sources to counteract power limitation in the main electric grid.

- VI. Simulation and experimental validation. To check the feasibility of the proposed solutions, several simulations are performed using MATLAB/Simulink. In addition, to further enhance validation, some experimental tests are carried out in a controlled environment within the laboratory of the LEMUR researching group of the University of Oviedo, Spain.

#### **1.3** Thesis contributions

The contributions of the work carried out during the course of this thesis are presented below:

#### Distributed Control System for Modular Power Converters [CP2]

First contribution is found in the development of a control system distributed into various devices following a hierarchical structure, making it suitable for its integration in modular power converters.

For this purpose, several distributed controllers are located in each of the power cells of the converter to perform the local control, with a central controller in charge of operating all of them to achieve the requirements established at an application level.

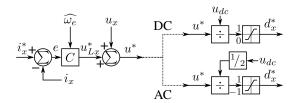

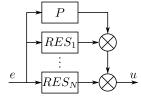

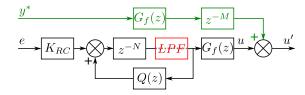

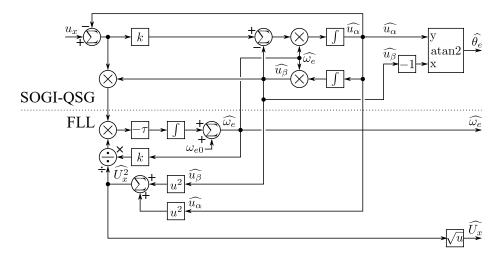

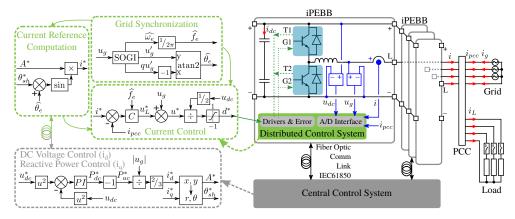

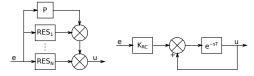

The analysis focuses on the implementation of versatile digital controller in the distributed devices based on resonant approaches to guarantee a proper operation for both AC and DC power units. This enables the possibility of building a multiport power converter controlling an arbitrary number of power units.

#### Power Sharing Solutions for a Multiport Converter [JP1, CP1]

Second contribution is found in the proposal of compensation alternatives for power sharing mismatches occurring during the operation of multiport converters based on distributed control systems.

The connection of several power loads and sources together with different energystorage units requires a specific distribution of the power flow among the different devices to maintain a stable operation of the whole system. Therefore, a power sharing algorithm is integrated in the distributed control system to address this issue. Nevertheless, either errors in the measurements, power limitations in the units or islanding operation can provoke mismatches in the power sharing. Thus, several compensation alternatives are proposed to counteract this problem.

## Distributed Control Deployment in a Digital Platform based on a $\mu$ P under RTOS [IPR1, SLA1]

Final contribution is related to the implementation of the central controller of a distributed control system in a general-purpose Micro-Processor. This is done by integrating a Real-Time extension in a conventional open-source Operating System. This way, firm real-time operation is guaranteed to execute high-priority tasks regarding control operation, while keeping low-priority services typically available in an OS.

#### 1.4 Thesis publications

The work developed for the thesis has resulted in the writing of several conference and journal papers, as shown below. In some of them [JP1, CP1, CP2], the author contribution is strictly the result of the research contributions in this thesis; in the others, the author of this thesis has contributed either by providing the control platform for the experimental validation or in the writing and reviewing process.

#### **1.4.1** Peer-reviewed journal papers

- JP1 G. Villa, S. Saeed, P. García, C. Gómez-Aleixandre and R. Georgious, "Compensation Alternatives for Power Sharing Mismatch in Multiport DC–DC–AC Converters," in *IEEE Transactions on Industry Applications*, vol. 57, no. 6, pp. 6221-6236, Nov.-Dec. 2021, doi: 10.1109/TIA.2021.3115721.

- JP2 I. Peláez, P. García, G. Villa and S. Saeed, "Real-Time Measurement of Li-Ion Battery Cells Using Power Converter Pulse-Signal Injection and Fusion Methods," in *IEEE Transactions on Industry Applications*, vol. 57, no. 6, pp. 6350-6361, Nov.-Dec. 2021, doi: 10.1109/TIA.2021.3101777.

- JP3 A. Suárez-González, P. García, A. Navarro-Rodríguez, G. Villa and J. M. Cano, "Sensorless Unbalance Modeling and Estimation as an Ancillary Service for LV Four-Wire/Three-Phase Power Converters," in *IEEE Transactions on Industry Applications*, vol. 55, no. 5, pp. 4876-4885, Sept.-Oct. 2019, doi: 10.1109/TIA.2019.2918046.

#### 1.4.2 Peer-reviewed conference papers

CP1 G. Villa, S. Saeed, P. García, C. Gómez-Aleixandre and R. Georgious, "Compensation Alternatives for Power Sharing Errors in Multi-Port Converters for Hybrid DC/AC Microgrids," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 6929-6939, doi: 10.1109/ECCE.2019.8912879.

- CP2 G. Villa, C. Gómez-Aleixandre, P. García and J. García, "Distributed Control Alternatives of Modular Power Converters for Hybrid DC/AC Microgrids," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018, pp. 6379-6386, doi: 10.1109/ECCE.2018.8557556.

- CP3 J. M. Piedra, P. García, R. Georgious, G. Villa and M. B. Gebremariam, "Transformer-less Alternative Topologies of a Unified Power Quality Conditioner with Embedded Hybrid Energy Storage," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 3176-3181, doi: 10.1109/ECCE47101.2021.9595585.

- CP4 C. Gómez-Aleixandre, A. Navarro-Rodríguez, G. Villa, C. Blanco and P. García, "Sharing Control Strategies for a Hybrid 48V/375V/400Vac AC/DC Microgrid," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 3900-3907, doi: 10.1109/ECCE44975.2020.9235472.

- CP5 M. Crespo, R. Georgious, P. García and G. Villa, "Active equalization of series/parallel Li-ion battery modules including no-load conditions," 2020 IEEE Energy Conversion Congress and Exposition (ECCE), 2020, pp. 4431-4437, doi: 10.1109/ECCE44975.2020.9236250.

- CP6 C. Gómez-Aleixandre, G. Villa, P. García, A. Suárez-González and Á. Navarro-Rodríguez, "Homopolar harmonic injection and grid synchronization in distributed control systems for grid-tied intelligent power electronic blocks in 4-wire 3-phase converters," *IECON 2019 45th Annual Conference of the IEEE Industrial Electronics Society*, 2019, pp. 3906-3911, doi: 10.1109/IECON.2019.8927413.

- CP7 C. Gómez-Aleixandre, P. García, Á. Navarro-Rodríguez and G. Villa, "Design and Control of a Hybrid 48v/375v/400Vac AC/DC Microgrid," *IECON 2019 -*45th Annual Conference of the IEEE Industrial Electronics Society, 2019, pp. 3977-3982, doi: 10.1109/IECON.2019.8926709.

- CP8 I. Peláez, P. García, G. Villa and S. Saheed, "Li-ion Batteries Parameter Estimation Using Converter Excitation and Fusion Methods," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 2491-2498, doi: 10.1109/ECCE.2019.8912968.

- CP9 M. Crespo, P. García, R. Georgious, G. Villa and J. García, "Design and Control of a Modular 48/400V Power Converter for the Grid Integration of Energy Storage Systems," 2019 IEEE Energy Conversion Congress and Exposition (ECCE), 2019, pp. 1421-1428, doi: 10.1109/ECCE.2019.8912775.

- CP10 I. Peláez, S. Saheed, G. Villa and P. García, "Optimization Method for the Integration of Hybrid Energy Storage Systems in Industrial Applications," 2018 IEEE Energy Conversion Congress and Exposition (ECCE), 2018, pp. 6646-6653, doi: 10.1109/ECCE.2018.8557882.

- CP11 A. Suárez-González, P. García, Á. Navarro-Rodríguez, G. Villa and J. M. Cano, "Sensorless unbalance correction as an ancillary service for LV 4-wire/3-phase power converters," 2017 IEEE Energy Conversion Congress and Exposition (ECCE), 2017, pp. 4799-4805, doi: 10.1109/ECCE.2017.8096816.

#### 1.5 Thesis software with intellectual property rights

The work developed for the thesis has also resulted in the development of a software with intellectual property rights [IPR1], in order to enable the exploitation of part of the knowledge acquired during the course of the thesis at a business level.

IPR1 Software name: DECiSivE - Development of Energy Control SystEms. Holder: University of Oviedo. Authors: Pablo García, Marcos Cuadrado and Geber Villa. Registration authority: General Registry of Intellectual Property, Ministry of Culture and Sport, Spain. Request number: O-308-2020. Request date: 29 September 2020. Registration number: 05/2020/432. Registration date: 30 November 2020.

The explotation of the software is currently active, since a 5-year software license agreement [SLA1] has been signed with the company Enfasys Ingeniería S.L. for the development of part of its products using the software with intellectual property rights derived from the thesis work.

SLA1 Software name: DECiSivE - Development of Energy Control SystEms. Vendor company: University of Oviedo Foundation on behalf of University of Oviedo. User company: Enfasys Ingeniería S.L. Authors: Pablo García (10% share in user company), Marcos Cuadrado (30% share in user company) and Geber Villa (10% share in user company). Reference number: PAT-20-003. Start date: 10 November 2020. End date: 10 November 2025.

#### 1.6 Thesis outline

The thesis document is organized in seven chapters and an appendix according to the following structure:

- Chapter 1 introduces the background and motivation behind the realization of this thesis. From that, the fundamental objectives of this work are determined and the contributions which support the thesis are presented. In addition, an enumeration of the different journal and conference publications derived from the thesis work is shown. Finally, the structure of the document is described to facilitate its understanding.

- Chapter 2 shows a literature review and a state-of-the-art analysis related to the use of distributed control systems in modular power converters. The concept of power cell is initially presented, giving some examples of converter configurations and applications where modular converters based on this concept are used. After that, a generic structure for the distributed control is described, from which different implementations are found in literature. Moreover, a review of different approaches and developments of Real-Time Operating Systems valid for digital controller implementations is carried out. Finally, power sharing in multiport power converters is analyzed, focusing on the exploitation of hybrid energy storage systems.

- Chapter 3 presents the dynamic modeling of the power of the modular converter approach with the added instrumentation and control devices required to operate it conveniently for a distributed control scheme.

- Chapter 4 addresses the analysis and development of the distributed digital control system needed for a versatile operation of the modular power converter, so that it can operate multiple power units with different electrical characteristics (DC, single-phase AC or three-phase AC).

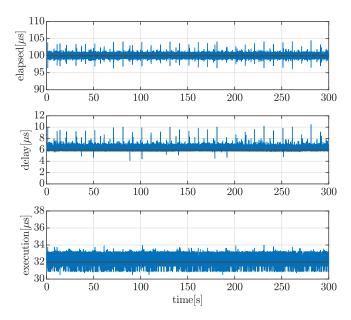

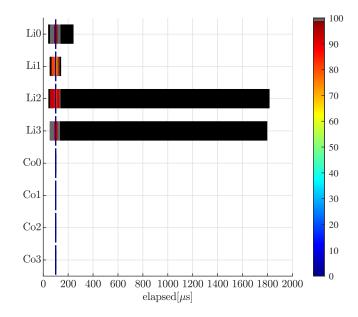

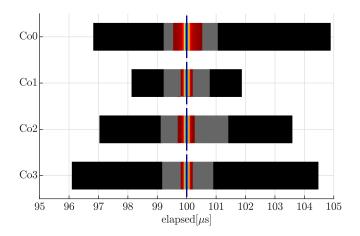

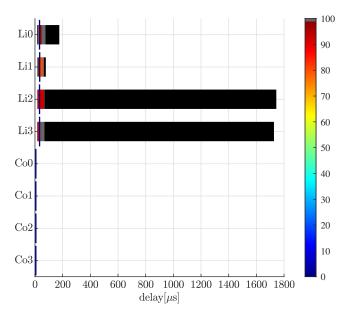

- Chapter 5 shows an analysis of latency in the Real-Time Operating System used for the implementation of the central controller in the distributed control system. The analysis is performed to validate firm real-time operation, which is necessary for the correct performance of the central controller.

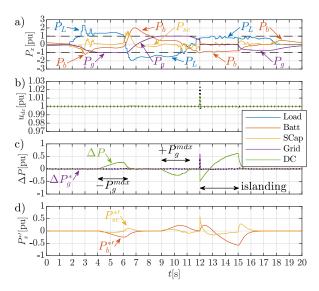

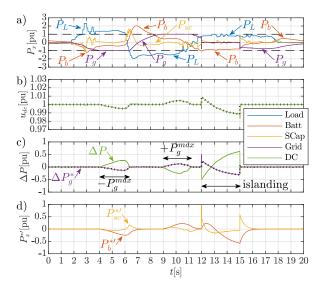

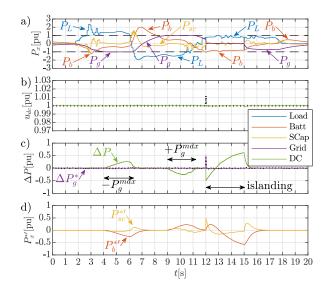

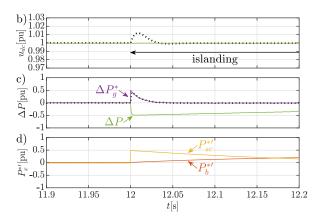

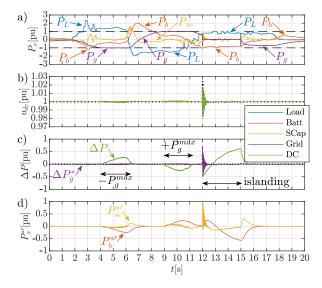

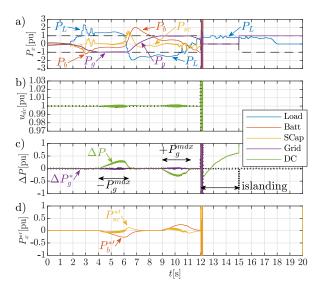

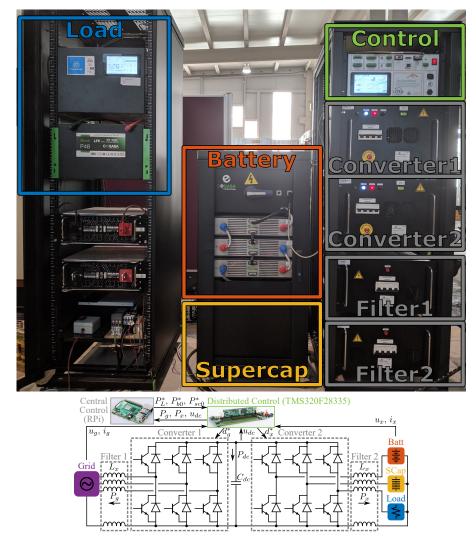

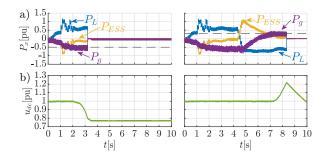

- Chapter 6 presents the implementation of a multiport power converter based on the results achieved in previous chapters, operating a system with several power units, such as load, source and energy-storage devices. The power sharing algorithm used to properly distribute the power flow among the different units is discussed, including compensation techniques to counteract power mismatches due to measurement errors, power limitation and islanding operation.

- Chapter 7 describes the conclusions derived from all the work carried out during the thesis, as well as the future work that can be developed starting with the results obtained.

# Chapter 2

# Literature review and state of the art

# 2.1 Introduction

In this chapter, a review of the literature related to the different topics covered in the development of the thesis is carried out to support the contributions presented in future chapters.

The main objective of this work is the development of a distributed control system suitable for the implementation of a modular power converter with a multiport structure based on the use of basic power blocks.

Therefore, an initial review of different configurations of modular converters based on basic power blocks is performed. In this way, it is possible to determine the most suitable modular converter structure to meet the objectives set. For this purpose, information is sought about the concept of the basic power block, the characteristics it provides and why it is suitable for the construction of modular power converters. After that, different configurations of power converters based on a basic power block and proposed applications using these converters are reviewed in the literature.

Once the state of the art on modular power converters based on basic power blocks has been analyzed, the literature is reviewed for distributed control systems that allow the proper management of these converters. Initially, information about the structuring of distributed control systems is sought, and then different implementations that can be made in this type of control are discussed. All this in order to understand how to make the most appropriate configuration to meet the objective of implementing a distributed control system suitable for a multiport converter.

An essential requirement for the realization of a distributed control system is to have a communications system that interconnects the different control units with each other. Therefore, the organization of communications in different layers is analyzed to then review various existing protocols with different characteristics depending on the needs of each specific application.

In addition, the implementation of a distributed control system for multiport converters imposes a high computational burden to manage and synchronize the operation of all distributed control units, as well as interactivity to facilitate local or remote monitoring. Therefore, a review of the different implementations of Real-Time Operating Systems is made in order to integrate the central controller in a high-performance microprocessor. In this way, it is possible to execute high-priority tasks with firm realtime constraints related to critical control tasks, at the same time as low-priority tasks related to auxiliary control or monitoring tasks.

# 2.2 Modular power converters

Modular power converters are based on the development of a basic power block that can be replicated several times in order to build the power conversion stage required for the relevant application. In this way, a flexible converter is formed, which is adaptable to changing requirements for use in a variety of applications, all without the need for a complete redesign of the converter.

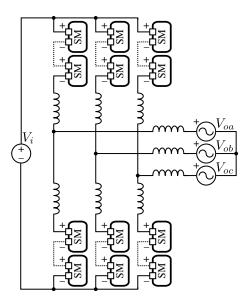

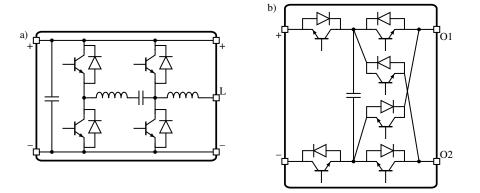

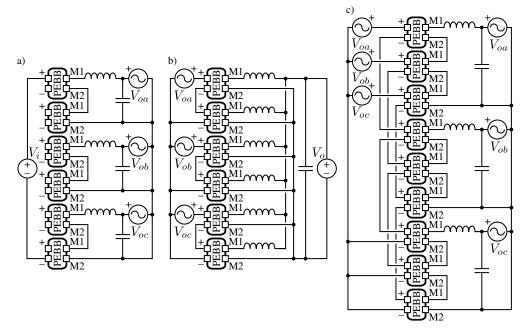

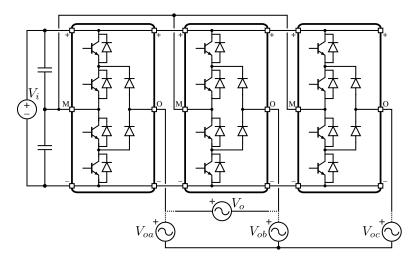

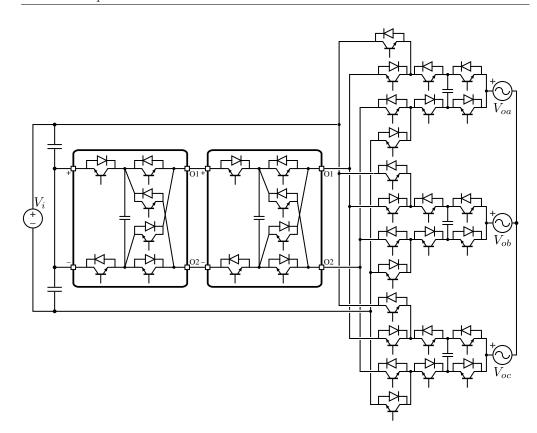

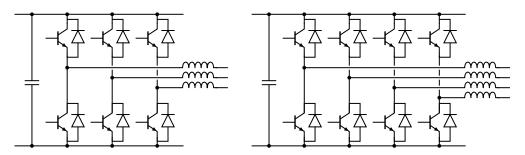

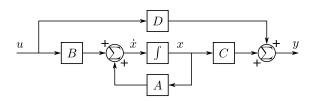

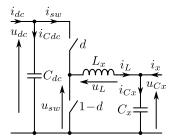

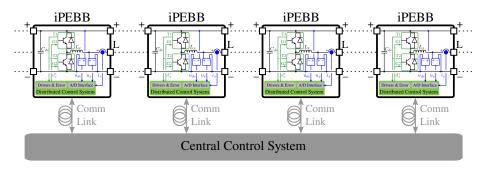

The modular power converter concept is exploited in the development of Modular Multilevel Converters (MMCs) [2.1], which are based on the series connection of several identical submodules in each branch in order to increase the voltage level that the converter can withstand, thus enabling its integration in HVDC applications. By designing a submodule with a fixed power stage that can be replicated several times to meet the specific requirements of each application, it is possible to provide the converter with a modular structure, which gives it flexibility in its sizing and therefore great scalability. Fig. 2.1 shows the implementation of the MMC based on submodules (SM) with a fixed power stage.

Following the MMC approach, a modular approach can be applied to other types of converters to take advantage of enhanced functionality, improving performance in a variety of applications.

Considering all the above, different implementations of basic power blocks capable of building modular power converters are reviewed in this section. After that, different converter configurations based on these building blocks and, in turn, different applications where they can be employed are discussed.

#### 2.2.1 Power Electronics Building Block (PEBB)

The idea of using a basic power block for the construction of power converters is reflected in the definition of the Power Electronics Building Block (PEBB) concept

Figure 2.1: MMC based on submodules (SM) with a fixed power stage.

[2.2, 2.3]. The main objective associated with this concept is to standardize a power block with a certain structure that can be reused in multiple applications.

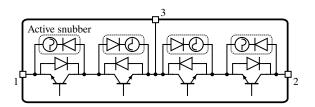

From a conventional point of view, the construction of a specific power converter for a given application involves a design and validation process with a considerable cost. At the same time, the implementation of this converter is associated with installation and maintenance costs that are not negligible. The design of reusable PEBBs can reduce these costs. The objective is to focus the engineering effort on the design of the PEBB, with all the costs that this entails, in order to reduce them in the medium and long term by integrating the PEBB into various converters that can be used in multiple applications. Providing a PEBB enables an open plug-and-play converter design methodology, in which the design of a converter focuses on knowing the characteristics of the PEBB to interconnect them in a certain way to develop the desired application.

The design of the PEBB is critical to comply with a user-friendly methodology based on the interconnection of functional blocks. Therefore, the building block must contain all those elements necessary to fulfill its purpose. First, those components that make up the power stage must be available, whether they are active (power switches) or passive energy-storage elements (inductors and capacitors). Next, switching control logic such as gate drivers, modulators and comparators must be integrated. Finally, cooling systems to dissipate heat, sensors to know the current state of the PEBB and protections to act in case of malfunction must be introduced.

Similar approaches to the PEBB concept have been explored, such as Power Block Geometry (PBG) [2.4]. In this case, the authors propose the creation of several basic power units that can be put together like a puzzle, depending on the power conversion

step to be performed. This confirms the growing interest and development of modular topologies based on basic power blocks, resulting in different implementations of PEBBs proposed over time.

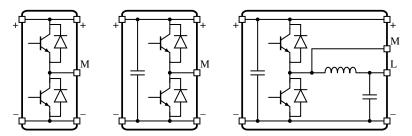

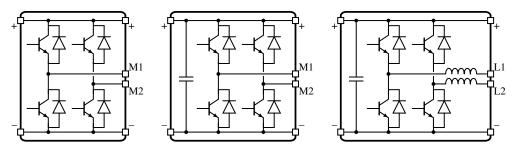

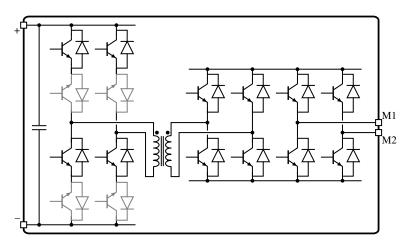

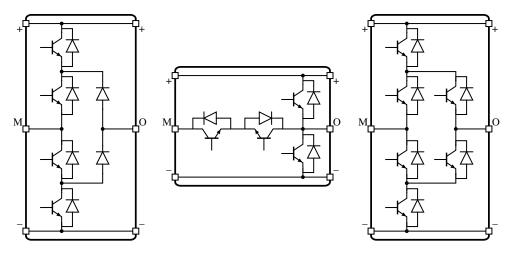

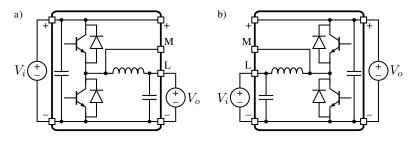

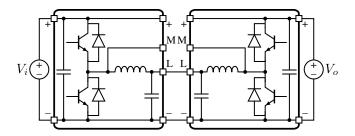

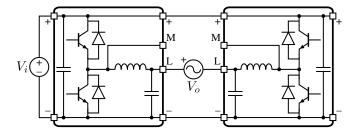

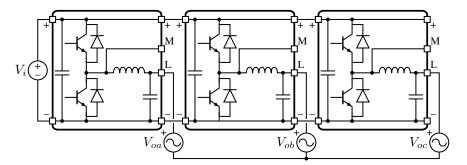

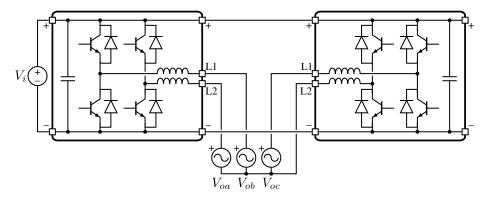

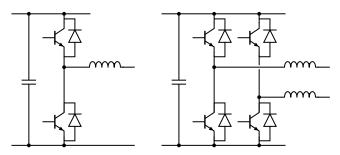

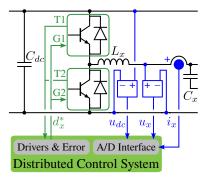

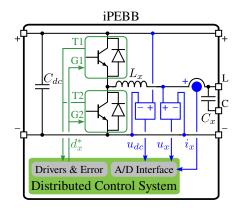

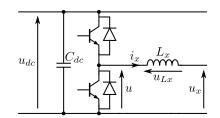

Starting with the simplest implementations, PEBB based on the half-bridge topology can be found in the literature. The starting point is to integrate in a single functional block two power switches connected in series and the drivers and control electronics to operate them properly. This allows to obtain a basic PEBB with halfbridge topology that can be used in different power converters [2.5]. To improve the performance of the PEBB and reduce its dependence on external elements, additional passive elements can be added to this topology, such as a DC capacitor [2.6] or a midpoint LC filter [2.7], generating new PEBBs more suitable for various applications. Considering all the above, Fig. 2.2 shows several options for PEBBs based on the half-bridge topology.

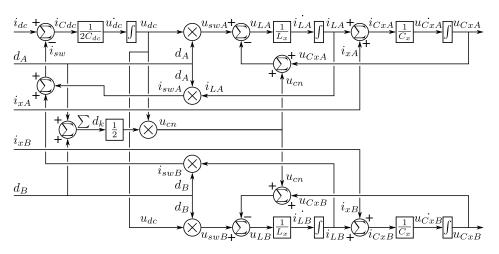

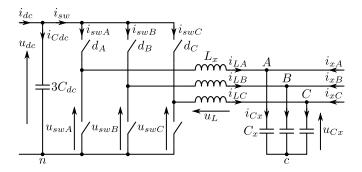

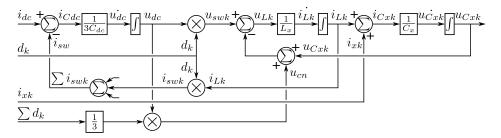

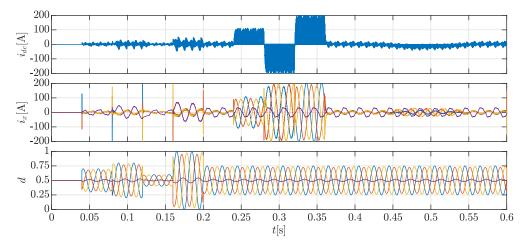

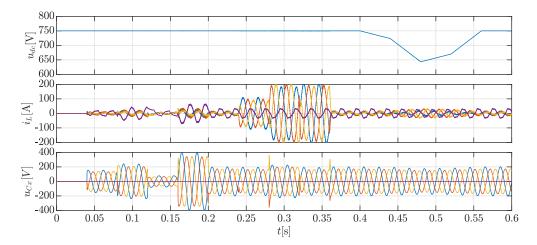

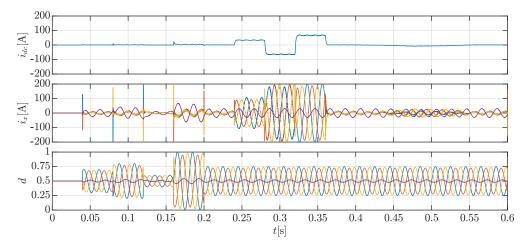

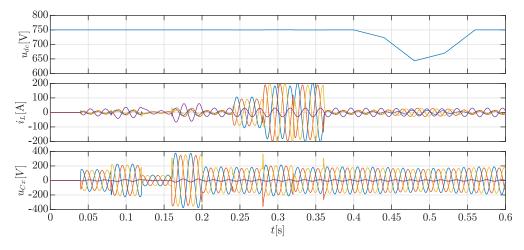

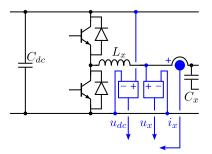

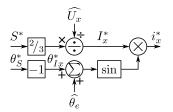

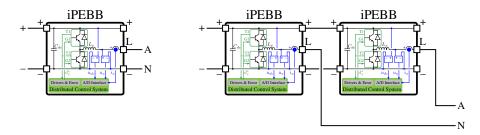

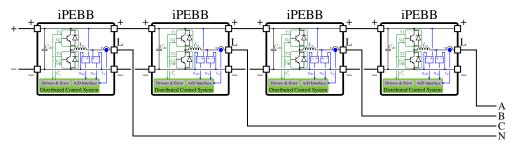

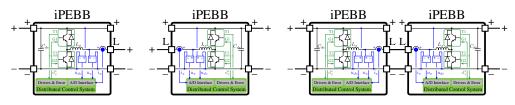

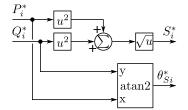

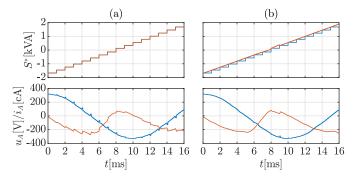

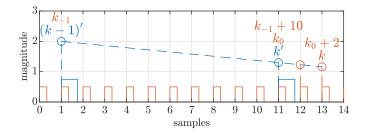

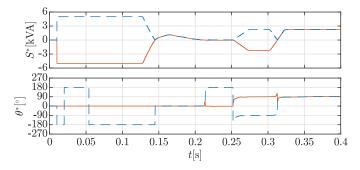

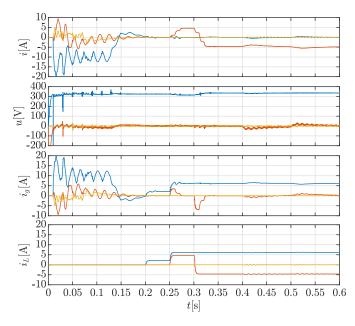

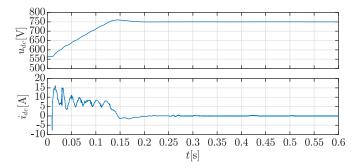

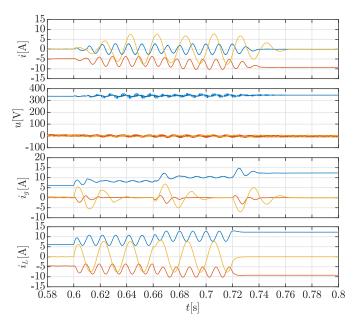

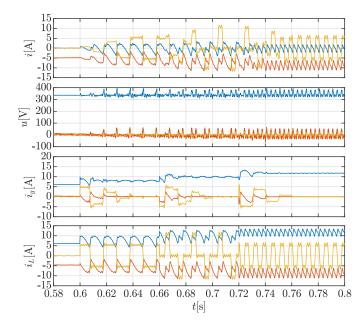

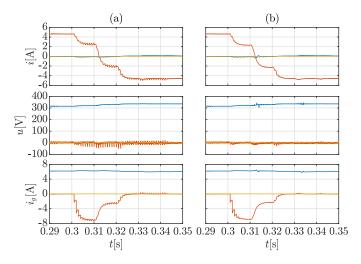

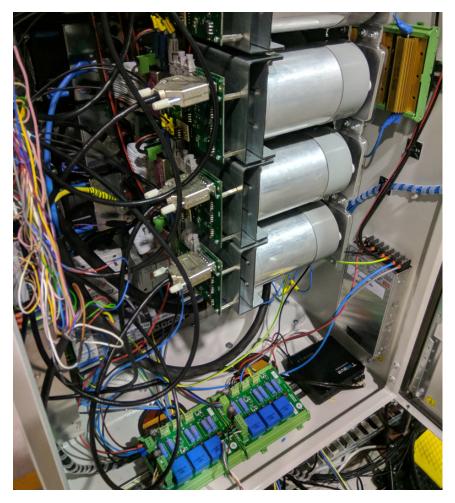

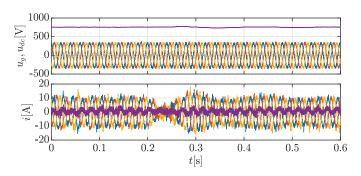

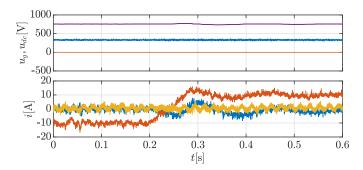

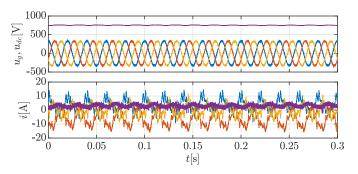

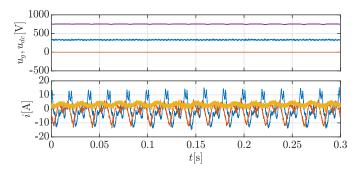

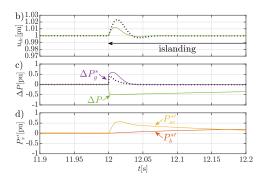

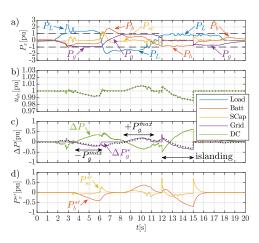

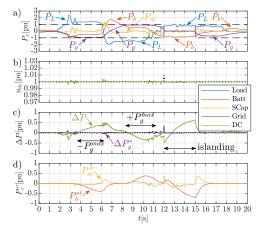

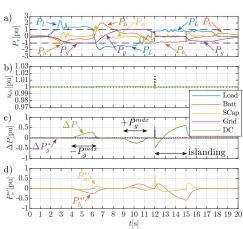

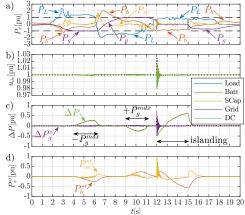

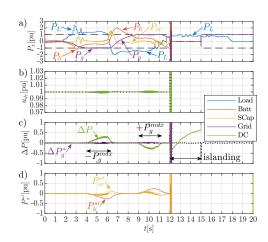

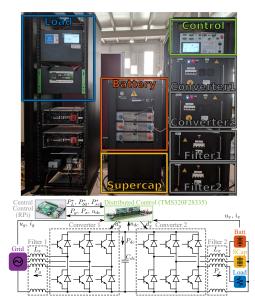

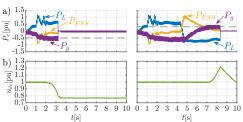

Figure 2.2: PEBB implementations based on the half-bridge topology.