## Wide-bandgap semiconductor based multilevel converters for HVDC connection between Sardinia and Italy

by

Carlos Gómez-Aleixandre Tiemblo

Submitted to the Department of Electrical Engineering, Electronics,

Computers and Systems

in partial fulfillment of the requirements for the degree of

Erasmus Mundus Master Course in Sustainable Transportation and

Electrical Power Systems

at the

#### UNIVERSIDAD DE OVIEDO

August 2017

© Universidad de Oviedo 2017. All rights reserved.

| Author       |                                                                    |

|--------------|--------------------------------------------------------------------|

|              |                                                                    |

| Certified by |                                                                    |

| Certified by | Fabio Giulii Capponi Professor at University of Rome "La Sapienza" |

## Wide-bandgap semiconductor based multilevel converters for HVDC connection between Sardinia and Italy

by

#### Carlos Gómez-Aleixandre Tiemblo

Submitted to the Department of Electrical Engineering, Electronics, Computers and Systems

on August 31, 2017, in partial fulfillment of the requirements for the degree of Erasmus Mundus Master Course in Sustainable Transportation and Electrical Power Systems

#### Abstract

In this thesis, the possibility to apply wide-bandgap semiconductor based multilevel converters to the refurbishment of the existing HVDC connection between Sardinia, Corsica and the Italian mainland, named SACOI (300 MW, 200kV), is studied.

For that purpose, the work starts with the model of the current system, with 12 pulse thyristor based converters, using mainly Simulink.

After that, the new power conversion system is designed and modelled, considering different possible configuration for multilevel converters (finally focusing on modular multilevel converters) and their advantages and drawbacks.

Once the simulation models with their control strategies are obtained, the performance of both systems (with 12 pulse thyristor based converters and with modular multilevel converters) are analysed and compared, focusing on some important aspects like: harmonic distortion (both in the DC and the AC sides), active and reactive power exchange control capability, etc.

Finally, the results are analyzed and show the importan advantages of MMC agains the current system (reactive power management and less harmonic distortion).

Thesis Supervisor: Fabio Giulii Capponi

Title: Professor at University of Rome "La Sapienza"

### Acknowledgments

First of all, I would like to thank my supervisor, the Professor Fabio Giulii Capponi, for considering that I was a good candidate for this project and also for all his help during the duration of the project.

I would also like to express my gratitude to all the other profesors I have had during these 2 years of Erasmus Mundus Master Course in Sustainable Transportation and Electrical Power Systems, who have provided me the knowledge required to develop this Master Thesis and for my future career.

I want to thank to all my classmates during this Master Course and all the other friends I have met in these two years. It was an awesome experience to have this mixture of different cultures and I am glad that we ended up being a group of very good friends. It was really nice to have all of you living in Gijón, my city, and I am sure you enjoyed it as I did. I know we will all meet again and I wish you the best for the future after this Master.

# Contents

| 1 | Intr | roduction                                        | 13   |  |  |  |  |  |

|---|------|--------------------------------------------------|------|--|--|--|--|--|

|   | 1.1  | Historical background                            |      |  |  |  |  |  |

|   | 1.2  | Refurbishment of the existing connection         | . 14 |  |  |  |  |  |

|   | 1.3  | Objectives                                       | . 17 |  |  |  |  |  |

|   | 1.4  | Structure                                        | . 19 |  |  |  |  |  |

| 2 | Sta  | ate of the art                                   | 21   |  |  |  |  |  |

|   | 2.1  | HVDC systems                                     | . 21 |  |  |  |  |  |

|   | 2.2  | LCC based HVDC connections                       | . 23 |  |  |  |  |  |

|   |      | 2.2.0.1 6-pulse thyristor bridge                 | . 24 |  |  |  |  |  |

|   |      | 2.2.0.2 12-pulse thyristor bridge                | . 25 |  |  |  |  |  |

|   |      | 2.2.0.3 Current system configuration and control | . 27 |  |  |  |  |  |

|   | 2.3  | VSC based HVDC connections                       | . 28 |  |  |  |  |  |

|   |      | 2.3.0.1 Neutral Point Clamped (NPC)              | . 29 |  |  |  |  |  |

|   |      | 2.3.0.2 Flying capacitor                         | . 32 |  |  |  |  |  |

|   |      | 2.3.0.3 Modular Multilevel Converters (MMC)      | . 34 |  |  |  |  |  |

| 3 | MN   | MC systems                                       | 39   |  |  |  |  |  |

|   | 3.1  | Modelling of the system                          | . 39 |  |  |  |  |  |

|   |      | 3.1.1 abc to dq transformation                   | . 42 |  |  |  |  |  |

|   | 3.2  | Modulation technique                             | . 43 |  |  |  |  |  |

|   | 3.3  | Control strategy                                 | . 45 |  |  |  |  |  |

|   |      | 3.3.1 Current control                            | . 45 |  |  |  |  |  |

|   |     | 3.3.3   | Active and reactive power control         | 48         |

|---|-----|---------|-------------------------------------------|------------|

|   |     | 3.3.4   | Coordinated control of the converters     | 49         |

| 4 | Sim | ulatio  | n                                         | 51         |

|   | 4.1 | System  | n data                                    | 51         |

|   | 4.2 | Resul   | ts                                        | 53         |

| 5 | Cor | nclusio | ns                                        | <b>5</b> 9 |

|   | 5.1 | MMC     | vs. Thyristor based                       | 59         |

|   | 5.2 | Degre   | e of fulfilment of the initial objectives | 60         |

| 6 | Fut | ure de  | velopment                                 | 61         |

|   |     |         |                                           |            |

# List of Figures

| 1-1  | Single phase leg of a two-level converter and the AC output waveform [3] | 15 |

|------|--------------------------------------------------------------------------|----|

| 1-2  | Single phase leg of a two-level converter and the AC output waveform [3] | 18 |

| 2-1  | Comparison of the costs for AC and DC transmission [5]                   | 22 |

| 2-2  | LCC-HVDC scheme [7]                                                      | 23 |

| 2-3  | Circuit configuration of the 6-pulse thyristor bridge with highly induc- |    |

|      | tive load (constant current) [8]                                         | 24 |

| 2-4  | Load voltage waveforms for the 6-pulse thyristor bridge for different    |    |

|      | firing angles $\alpha$ [8]                                               | 25 |

| 2-5  | Current waveforms for the 6-pulse thyristor bridge [8]                   | 25 |

| 2-6  | Circuit configuration of the 12-pulse thyristor bridge with highly in-   |    |

|      | ductive load (constant current) [8]                                      | 26 |

| 2-7  | Voltage and current waveforms for the 12-pulse thyristor bridge $[8]$    | 27 |

| 2-8  | LCC-HVDC scheme [7]                                                      | 27 |

| 2-9  | VSC-HVDC scheme [7]                                                      | 29 |

| 2-10 | Three-phase three-level scheme of a NPC [10]                             | 30 |

| 2-11 | Three-phase five-level scheme of a NPC [10]                              | 31 |

| 2-12 | Line voltage waveform of a five-level NPC [10]                           | 31 |

| 2-13 | Three-phase three-level scheme of a flying capacitor [10]                | 32 |

| 2-14 | Three-phase five-level scheme of a flying capacitor [10]                 | 33 |

| 2-15 | General scheme of a MMC using full-bridge [10]                           | 34 |

| 2-16 | Output phase voltage waveform of an 11-level cascade inverter with 5     |    |

|      | separate DC sources [10]                                                 | 35 |

| 2-17 | Schematic block diagram of MINIC based HVDC system, (a) Single line       |    |

|------|---------------------------------------------------------------------------|----|

|      | diagram, (b) Internal circuit diagram of MMC converter station $[11]$ .   | 36 |

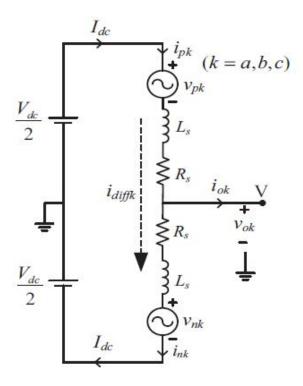

| 3-1  | Single phase equivalent circuit of MMC [11]                               | 40 |

| 3-2  | Modulating and carrier signals for a five-level MMC                       | 44 |

| 3-3  | Refere and resulting voltage                                              | 44 |

| 3-4  | Diagram of the control scheme (the image is a modification of the         |    |

|      | original in [11])                                                         | 45 |

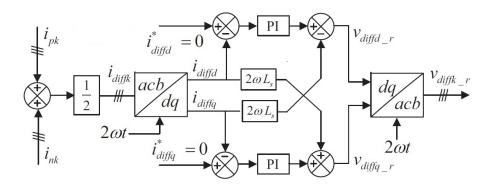

| 3-5  | Control of the circulating current (the image is a modification of the    |    |

|      | original in [11])                                                         | 47 |

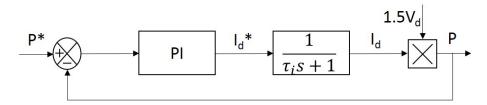

| 3-6  | Diagram of the active power control loop                                  | 48 |

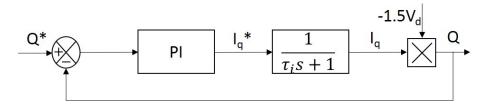

| 3-7  | Diagram of the reactive power control loop                                | 48 |

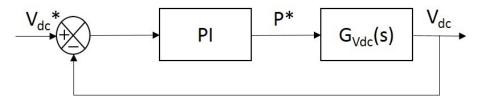

| 3-8  | Diagram of the DC link voltage control loop                               | 49 |

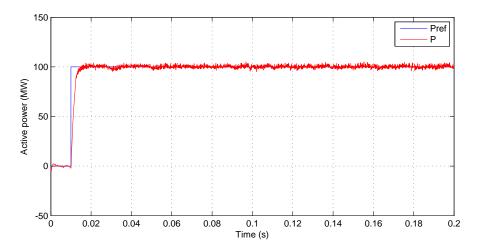

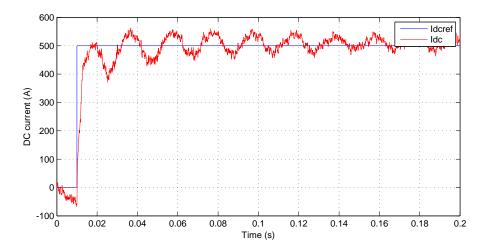

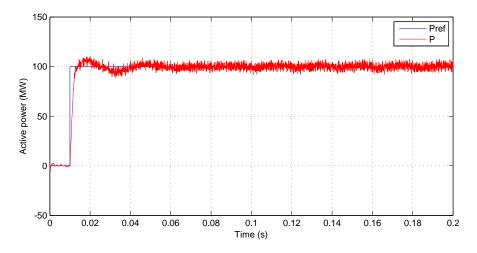

| 4-1  | Active power received by Sardinia AC grid                                 | 53 |

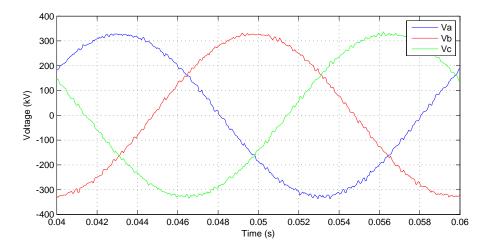

| 4-2  | Voltage at the connection to the grid                                     | 54 |

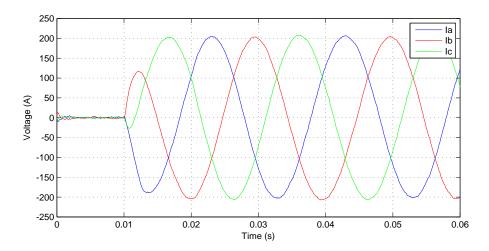

| 4-3  | Current at the connection to the grid                                     | 54 |

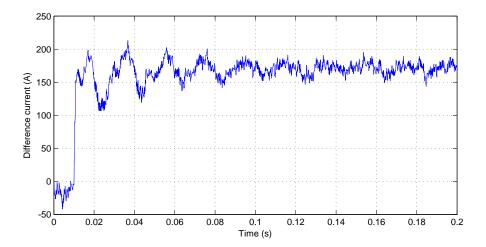

| 4-4  | Phase $a$ difference current in Sardinia converter $\ldots \ldots \ldots$ | 55 |

| 4-5  | DC link current at Sardinia terminal and desired value                    | 55 |

| 4-6  | Capacitor voltage in one of the branches                                  | 56 |

| 4-7  | Active power received by Sardinia AC grid                                 | 56 |

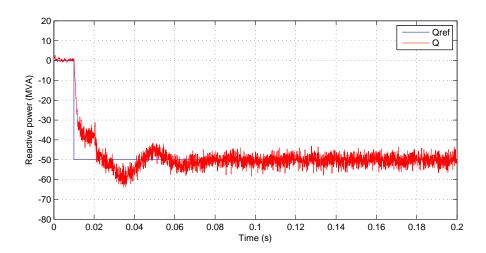

| 4-8  | Reactive power received by Sardinia AC grid                               | 57 |

| 4-9  | Rective power received by Italy AC grid                                   | 57 |

# List of Tables

| 2.1 | Switching scheme for three-level NPC [10]              | 30 |

|-----|--------------------------------------------------------|----|

| 2.2 | Switching scheme for five-level NPC [10]               | 30 |

| 2.3 | Switching scheme for three-level flying capacitor [10] | 32 |

| 2.4 | Switching scheme for five-level flying capacitor [10]  | 33 |

## Chapter 1

## Introduction

## 1.1 Historical background

The first practical applications of electricity started during the second half of the 19th century with direct current (DC) technologies.

After having patented the light bulb, Thomas Edison patented a electrical power distribution system using DC current and, in 1882, he opened his first power plant.

In 1882, the first High Voltage Direct Current (HVDC) transmission line was built, design by Oskar von Miller and Marcel Deprez, for connecting Miesbach and Munich (57 km distance) [1] for transmitting 1.5 kW at 2kV (less than 1 A) [2].

After that, even if some other HVDC transmission lines were built [1], with significantly higher power, voltage and current rating than the first one [1], there was a trend to move towards alternating current (AC) applications, mainly due to the appearance of induction machines and transformers.

The first one provided a efficient and robust way for electro-mechanical transformation, being more reliable than the other rotating machines. But the second one was even more important, providing the possibility of eadily changing the voltage (and, thus, the current) level in order to allow long distance transmission with lower cost.

This impossibility of changing the voltage and current levels in an easy way was the reason why AC current became the chosen option for a huge majority of the applications, including transmission, using DC current only for particular (and normally low power) applications.

But the development of the power electronic converters, with the invention of the mercury-arc valves in the 1930s, reopened the possibility of using DC current for some high power applications where the use of DC current could mean important advantages (being HVDC transmission the most important use).

Some important HVDC connections using mercury-arc valves were built during the following years, like the line connecting Sardinia and mainland Italy, which is going to be studied in this thesis, which was first built in 1968 using mercury-arc rectifiers for each side converter, rated at 200 kV and 200 MW.

The invention of thyristors in the 1950s led to an improvement in the efficiency and controllability of the rectifiers, in addition to the possibility of obtaining higher voltage and current ratings (by combining many thyristors in series or parallel). Because of this, the HVDC transmission became a more feasible solution for a wider range of cases, compared to the previous mercury-arc systems.

That was the case of the new terminal of the line analyzed in this thesis, which, apart from the previous terminals in Sardinia and Italy, got a new terminal in Corsica, built with thyristor valves in 1988, becoming a particular case of HVDC transmission due to this 3rd terminal and getting its current name, SACOI (Sardinia-Corsica-Italy).

Four years after, the old mercury-arc rectifiers on the two extremes of the SACOI line, were replaced by thyristor rectifiers and the power rating was increased up to 300 MW, reaching the current state of the system.

## 1.2 Refurbishment of the existing connection

Further improvements in the semiconductors, with the development of fully controllable switches (like IGBTs) allowed the appearance of voltage-sourced converters (VSC), instead of the previous current-sourced (CSC) or line-commutated converters (LCC) built with thyristors, allowing a much better controllability of the converters.

Initially, these IGBTs did not have enough current and voltage rating for being

used in applications with very high power ratings (like HVDC). Thus, thyristor rectifiers were still in use due to their higher voltage, current and power rating, despite their much worse controllability. However, the development of wide-bandgap (WBG) semiconductors, with high power ratings, introduced the possibility of using VSC for HVDC transmission.

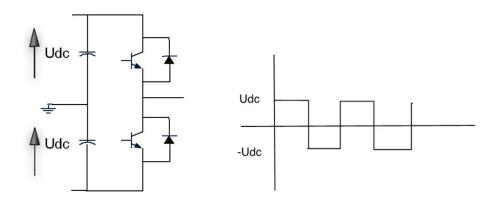

But, even with these WBG semiconductors, the voltage rating (around 6 kV for our case) is not enough for using it in HVDC transmission (DC link voltage of 200 kV for the SACOI connection) for standard (two-level) inverters (as the one shown in figure 1-2).

Figure 1-1: Single phase leg of a two-level converter and the AC output waveform [3]

This is one of the reasons why, instead of two-level converters, multilevel converters topologies, which will be explained in next chapter, are used for this application.

Some other important advantages of the use of multilevel converters are enumerated below [4].

- Quasi-sinusoidal AC voltage waveform: due to the high amount of levels, even if pulse-width modulation (PWM) were not used, the multilevel staircase waveform will have a quasi-sinusoidal form because of the high number of levels used.

- Low harmonic impact: due to the high number of levels, the waveform will be really close to a sinusoidal one, thus having low harmonic content compared to a two-level converter.

- Reduced costs for the filtering elements: because of this low harmonic content, the filtering elements required will be much less, even dispensable if the number of levels is really high.

- Possible direct connection to the MV grid: because of the non-requirement of filtering and the high controllability of the system (capability of controlling active and reactive power), the connection to the grid can be done directly, without filters or reactive power compensation equipment.

- Reduction of semiconductor losses due to a very low switching frequency per device: in two-level converters, to compensate the absence of a high number of steps for the staircase waveform, high frequency PWM techniques have to be used. However, the more levels you have, the lower frequency for the PWM you require (for similar harmonic distortion requirements). In the case of HVDC, the number of levels will easily be higher than 100, leading to carrier frequencies for the PWM of around 200 Hz, really low compared to the level case, in the order of kHz or tenths of kHz. This much lower frequency leads to an important reduction in the switching losses, meaning also less cooling required.

All of these advantages (except the last one referref to switching losses) are also important advantages of the multilevel converters compared to the thyristor converters currently used in SACOI connection, together with the much higher degree of controllability of the converters (in the thyristor converter, you can only control active power, meanwhile in the VSC you can control reactive power too).

Taking all the aforementioned advantages into account, the refurbishment of the SACOI connection was considered as a real possibility after the appearance of WBG semiconductors and multilevel converter topologies.

### 1.3 Objectives

The objectives of the present work are the design of a new system for the possible refurbishment of the line and the comparison between that system and the actual one.

For that purpose, the initial objective should be the proper understanding of the converters operation from a theoretical point of view.

After that, a proper control system must be design for the new system in order to have a proper operation.

And the last objective is the testing of the system using simulation programs (Matlab/Simulink).

Further improvements in the semiconductors, with the development of fully controllable switches (like IGBTs) allowed the appearance of voltage-sourced converters (VSC), instead of the previous current-sourced (CSC) or line-commutated converters (LCC) built with thyristors, allowing a much better controllability of the converters.

Initially, these IGBTs did not have enough current and voltage rating for being used in applications with very high power ratings (like HVDC). Thus, thyristor rectifiers were still in use due to their higher voltage, current and power rating, despite their much worse controllability. However, the development of wide-bandgap (WBG) semiconductors, with high power ratings, introduced the possibility of using VSC for HVDC transmission.

But, even with these WBG semiconductors, the voltage rating (around 6 kV for our case) is not enough for using it in HVDC transmission (DC link voltage of 200 kV for the SACOI connection) for standard (two-level) inverters (as the one shown in figure 1-2).

This is one of the reasons why, instead of two-level converters, multilevel converters topologies, which will be explained in next chapter, are used for this application.

Some other important advantages of the use of multilevel converters are enumerated below [4].

• Quasi-sinusoidal AC voltage waveform: due to the high amount of levels,

Figure 1-2: Single phase leg of a two-level converter and the AC output waveform [3]

even if pulse-width modulation (PWM) were not used, the multilevel staircase waveform will have a quasi-sinusoidal form because of the high number of levels used.

- Low harmonic impact: due to the high number of levels, the waveform will be really close to a sinusoidal one, thus having low harmonic content compared to a two-level converter.

- Reduced costs for the filtering elements: because of this low harmonic content, the filtering elements required will be much less, even dispensable if the number of levels is really high.

- Possible direct connection to the MV grid: because of the non-requirement of filtering and the high controllability of the system (capability of controlling active and reactive power), the connection to the grid can be done directly, without filters or reactive power compensation equipment.

- Reduction of semiconductor losses due to a very low switching frequency per device: in two-level converters, to compensate the absence of a high number of steps for the staircase waveform, high frequency PWM techniques have to be used. However, the more levels you have, the lower frequency for the PWM you require (for similar harmonic distortion requirements). In the case of HVDC, the number of levels will easily be higher than 100, leading

to carrier frequencies for the PWM of around 200 Hz, really low compared to the level case, in the order of kHz or tenths of kHz. This much lower frequency leads to an important reduction in the switching losses, meaning also less cooling required.

All of these advantages (except the last one referref to switching losses) are also important advantages of the multilevel converters compared to the thyristor converters currently used in SACOI connection, together with the much higher degree of controllability of the converters (in the thyristor converter, you can only control active power, meanwhile in the VSC you can control reactive power too).

Taking all the aforementioned advantages into account, the refurbishment of the SACOI connection was considered as a real possibility after the appearance of WBG semiconductors and multilevel converter topologies.

#### 1.4 Structure

Chapter 2 will analyze the state of the art, starting from a general analysis of HVDC systems for later doing a theoretical analysis of line-conmutated converter (LCC) and voltage-sourced converter based HVDC in different topologies.

Chapter 3, after having decided the use of MMC, will be focused on its analysis, starting with the modelling of the system for later talking about the control issues (the modulation technique used and the control of the different variables of the system).

Chapter 4 will be devoted to present and analyze the simulation results, so that chapter 5 can present the conclusions.

Chapter 6 will be used for proposing future trends for ongoing work.

Finally, chapter 7 will be a quality report of all the work realized and the quality of the resources, management and methods used.

## Chapter 2

## State of the art

## 2.1 HVDC systems

As mentioned in the previous chapter, traditionally AC was used for the vast majority of the applications, meanwhile DC applications, especially if talking about high power, were exceptions, mainly due to the difficulty of convert the commonly used AC into DC (and vice versa).

However, the development of converters for AC/DC conversion opened the possibility of using DC for high power applications, where some of their advantages can be exploited.

Some of these advantages are:

- Lower environmental impact:: fewer overhead lines required for same power because they require fewer overhead lines to deliver the same amount of power. They also allow more efficient operation of the system, reducing the required power production [5].

- Possibility of using ground/sea return: as used in SACOI connection. However, this ground/sea return is less used nowadays, due to environmental impact [6].

- **High controllability:** active power (and also reactive power, in the case of VSC) transfer is easily controlled.

- Less effective resistance: because of skin effect, resistance is greater when the frequency increases, being minimum for DC.

- Reactive power: in AC, there is reactive power flowing in the line, increasing the current (for the same active power transfer) and, thus, the losses and the voltage drop. This is especially important for submarine cables, where the effect of the capacitance is significantly higher.

The last two aforementioned advantages, in the end, result in the DC conductors being cheaper than the AC ones for the same requirements, especially for submarine cables.

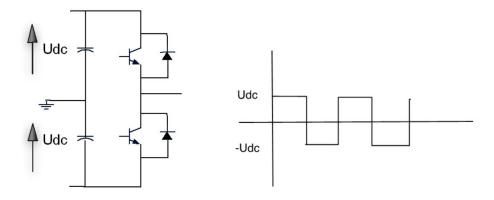

However, the DC terminal costs (cost of converter stations) are significantly higher than the AC ones, so DC transmission starts to be a more cost-effective solution when line length is higher than a critical or break-even point (around 600-800 km for overhead lines and 50 km for subsea cables [5]), as shown in figure 2-1.

Figure 2-1: Comparison of the costs for AC and DC transmission [5]

On the other hand, there are some drawbacks of using DC for transmission, like the difficulties for interrupting DC currents (in AC, the current naturally goes to zero twice per cycle, making the switching process easier; in DC, this does not happen and an electric arc would appear) and the precense of harmonics (in AC, with transformers for the terminal stations, the harmonic content is really small compared to the ones coming from AC/DC transformation).

Even with these drawbacks, HVDC is becoming more suitable for some applications where their advantages are crucial, like long-distance or submarine transmission or connection of asynchronous grids, which is only possible using DC connection.

#### 2.2 LCC based HVDC connections

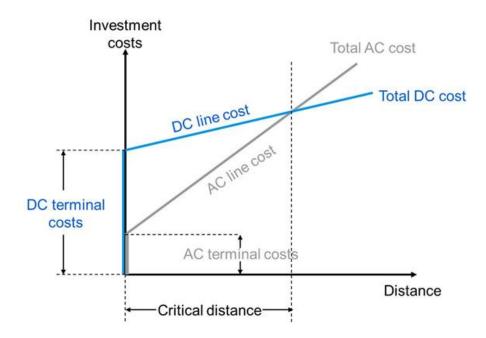

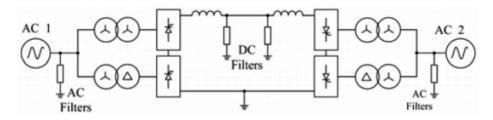

The first HVDC connections were done with this technology due to the presence of thyristors (and initially mercury-arc valves). The general scheme of the system is shown in figure 2-2.

Figure 2-2: LCC-HVDC scheme [7]

The first thing we can appreciate in the figure is the fact that the converters will always consume reactive power. Thus this system has no capability for reactive power control and some reactive power compensation will probably be required.

It can be seen that the connection between the two converters is done with an inductor (unlike the case of VSC, shown later in figure 2-9, which has a capacitor). This is due to the fact that this converter ideal operation is done with a constant current flowing in the link (that is the reason why they are also called current-sourced), so smoothing inductors are used to reduce the current ripple and operate close to constant current (in steady-state operation).

It can also be appreciated that the active power is supposed to be unidirectional, due to the fact that current can only flow in one direction (because of the thyristors unidirectionality). However, this is not totally true, because the voltage at the

terminal stations can be reversed, reversing also the power flow. In any case, unlike the case of VSC, for LCC connections we should think in the most likely direction of the power flow when doing the configuration to see which configuration is more convenient.

#### 2.2.0.1 6-pulse thyristor bridge

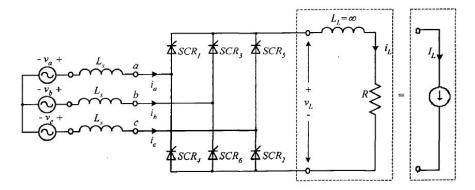

Figure 2-3 shows the scheme of a 6-pulse thyristor bridge for a highly inductive load, which means current can be assumed to be constant.

Figure 2-3: Circuit configuration of the 6-pulse thyristor bridge with highly inductive load (constant current) [8]

The output voltage waveforms are shown in figure 2-4 for different firing angles  $(\alpha)$ . The average output voltage can be obtained, as shown in [9]:

$$V_d = \frac{3\sqrt{2}}{\pi} V_{LL} cos\alpha = 1.35 V_{LL} cos\alpha \tag{2.1}$$

And taking into account that current is supposed to be constant, power transfer can be calculated as follows [9]:

$$P = V_d I_d = 1.35 V_{LL} I_d cos \alpha \tag{2.2}$$

Analyzing equation 2.2, it can be seen that for firing angles greater than 90°, the power flow is reversed and the converter works as an inverter.

Current waveforms are shown in figure 2-4, where we can see that the current in the input has a quasi-square waveform, which implies high harmonic content.

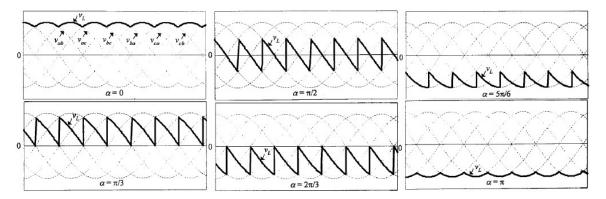

Figure 2-4: Load voltage waveforms for the 6-pulse thyristor bridge for different firing angles  $\alpha$  [8]

Figure 2-5: Current waveforms for the 6-pulse thyristor bridge [8]

#### 2.2.0.2 12-pulse thyristor bridge

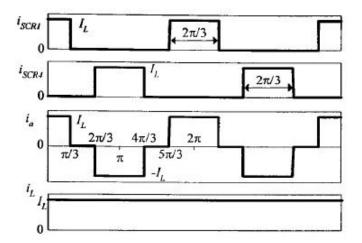

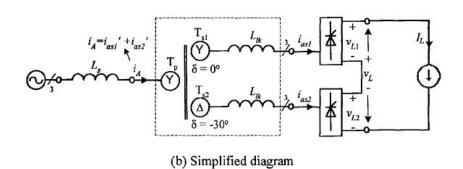

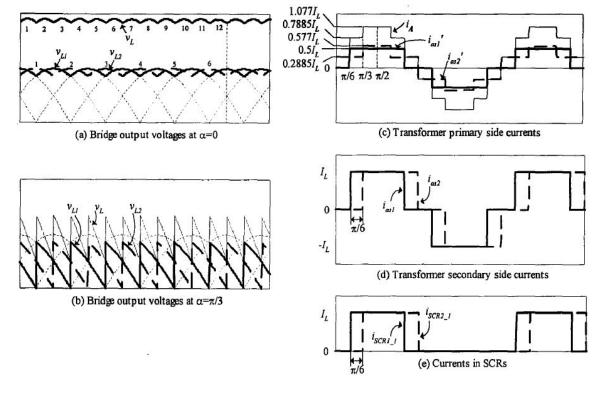

Figure 2-6 shows the scheme of a 12-pulse thyristor bridge for a highly inductive load. As we can see, the 12-pulse rectifier consist on two 6-pulse rectifiers series connected, with the input of each rectifier connected to the secondary side of a three-winding transformer, in which the inpute of the first converter is star connected (like the primary) and the input of the second one delta connected, being the ratio between the turn ratio between the two secondaries  $\frac{N_{s1}}{N_{s2}} = \frac{1}{\sqrt{3}}$ , resulting in the two inputs having the same magnitude for the line voltage, but with a phase shift of 30° [8].

By doing this, the output voltage generated, as shown in figure 2-7, is the sum of both outputs, which are the same obtained for the 6-pulse case in the previous case. With this, a higher output voltage is achieved (twice the previous one in average), but

(a) 12-pulse SCR rectifier with an inductive load

Figure 2-6: Circuit configuration of the 12-pulse thyristor bridge with highly inductive load (constant current) [8]

because of the phase-shift between the 2 outputs, the ripple is significantly reduced.

As mentioned before, the average output voltage of the 12-pulse rectifier is twice the one corresponding to the 6-pulse case for same firing angle and, for the same current, the power is doubled too as shown in the following equations [9]. Like before, for angles greater than 90°, the converter starts to work as an inverter.

$$V_d = \frac{6\sqrt{2}}{\pi} V_{LL} cos\alpha = 2.70 V_{LL} cos\alpha \tag{2.3}$$

$$P = V_d I_d = 2.70 V_{LL} I_d cos \alpha \tag{2.4}$$

Analyzing equation 2.2, it can be seen that for firing angles greater than 90°, the power flow is reversed and the converter works as an inverter.

Figure 2-7: Voltage and current waveforms for the 12-pulse thyristor bridge [8]

#### 2.2.0.3 Current system configuration and control

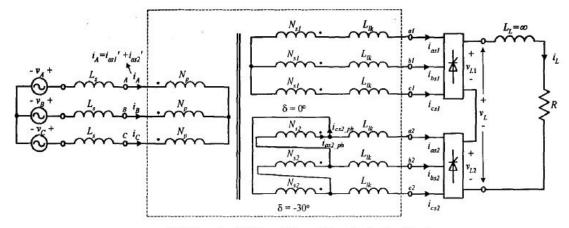

The current system used for SACOI connection uses the 12-pulse thyristor converters mentioned before. It has monopolar configuration, using the sea for current return. The scheme can be seen in figure 2-8.

Figure 2-8: LCC-HVDC scheme [7]

The control of this kind of systems, normally, is done by fixing the inverter extinction angle to its minimum value and controlling the angle in the rectifier to control the current flowing and, thus, the power (which depends on the net demand/production in Sardinia).

The SACOI connection, however, works in the opposite way. The rectifier, placed

in mainland, controls the voltage of the DC link, so will work with approximately constant firing angle regardless the power transfer required. The inverter, placed in Sardinia, changes its firing angle to increase or decrease its output voltage and, thus, change the current and power transfer.

When the direction of the power has to be reversed, the polarity of the DC link is changed (since the direction of the current cannot be reversed), and the converter in mainland works as inverter (still controlling the DC link voltage) and the one in Sardinia as rectifier (still controlling the current).

There is also one particularity of the SACOI connection: it has three terminals (the third one in Corsica). The converter in Corsica is the same as the other two, but for lower power rating. However, since the DC link polarity is determined by the power requirements in Sardinia, for changing the polarity of the DC link voltage as seen by the third terminal, there are for switches that allow to reverse the connection of the third terminal to the DC link (obtaining the required polarity regardless the situation).

The control in this third terminal is the same used for the Sardinia converter, in which the firing angle is changed in order to obtain the desired current and power.

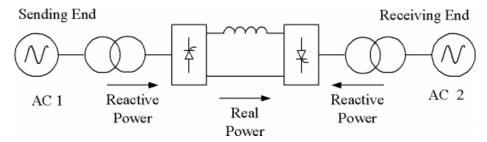

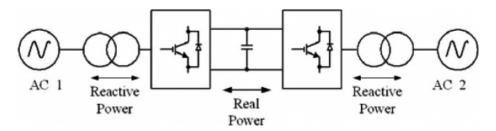

### 2.3 VSC based HVDC connections

As mentioned in the introduction, the development of IGBT and especially WBG semiconductors, it appeared the possibility of using VSC for the HVDC systems. This move towards VSC means an important increase in controllability and reduction of filtering equipment required for converters (especially in the case of multilevel converters). The general scheme of the system is shown in figure 2-9.

Compared to the LCC case analyzed before we can see three main differences:

- The converters can either produce or consume reactive power, increasing the controllability and avoiding the reactive power compensation equipment.

- The connection between the converters needs a capacitor in the DC link because

Figure 2-9: VSC-HVDC scheme [7]

this converter ideal operation requires constant DC link voltage (voltage-sourced converter).

• Active power can flow in either direction without changing the polarity of the DC link since the current can flow in both directions.

The last one is especially important. In the LCC case, if the power demanded in Sardinia changes its sign, the converter in Sardinia will need to wait until the converter in mainland changes its polarity to achieve this required power. Thus the operation of both converters are dependent and communication will be required, even in non-faulty situations. In the VSC case, if the power in Sardinia converter needs to be reversed, it can be done by itself by changing the direction of the current: the two converters are independent in normal conditions (the one in mainland will be in charge of keeping the voltage level in the desired level and the other will operate indepently and they will not require any communication).

Apart from that, for inverting the power flow in the third terminal, the switches are no required for the same reason.

Now, different multilevel topologies are going to be analyzed.

#### 2.3.0.1 Neutral Point Clamped (NPC)

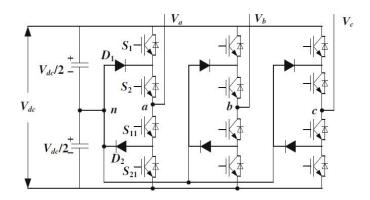

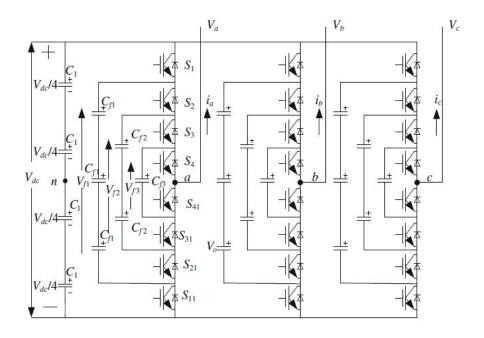

The first topology to be analyzed is the neutral point clamped (NPC). The scheme of a three-phase three-level NPC is shown in figure 2-10 and its switching scheme is shown in table 2.1.

The operation principle is easy: if point n is taken as the ground reference, the possible outputs will be  $+V_{dc}/2$  (upper switches connected, so the phase is connected

Figure 2-10: Three-phase three-level scheme of a NPC [10]

Table 2.1: Switching scheme for three-level NPC [10]

| $S_1$ | $S_2$ | $S_{11}$ | $S_{21}$ | $V_{an}$    |

|-------|-------|----------|----------|-------------|

| 1     | 1     | 0        | 0        | $+V_{dc}/2$ |

| 0     | 1     | 1        | 1        | 0           |

| 0     | 0     | 1        | 1        | $-V_{dc}/2$ |

to the positive terminal of the DC link), 0 (middle switches connected, so phase is connected to point n by the two diodes in antiparallel) or  $-V_{dc}/2$  (lower switches connected, so the phase is connected to the negative terminal of the DC link)

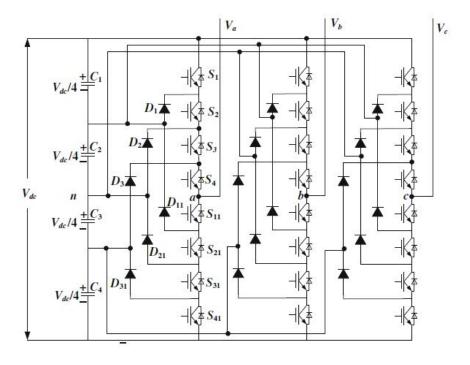

The same topology can be used for higher number of levels. In figure 2-11, the scheme of a three-phase five-level NPC is shown (switching scheme in table 2.2).

Table 2.2: Switching scheme for five-level NPC [10]

| $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_{11}$ | $S_{21}$ | $S_{31}$ | $S_{41}$ | $V_{an}$    |

|-------|-------|-------|-------|----------|----------|----------|----------|-------------|

| 1     | 1     | 1     | 1     | 0        | 0        | 0        | 0        | $+V_{dc}/2$ |

| 0     | 1     | 1     | 1     | 1        | 0        | 0        | 0        | $+V_{dc}/4$ |

| 0     | 0     | 1     | 1     | 1        | 1        | 0        | 0        | 0           |

| 0     | 0     | 0     | 1     | 1        | 1        | 1        | 0        | $-V_{dc}/4$ |

| 0     | 0     | 0     | 0     | 1        | 1        | 1        | 1        | $-V_{dc}/2$ |

The operation is similar, if the 4 upper (or lower) switches are connected, the phase is connected to the positive (or negative) terminal of the DC link. For the intermediate voltage levels, different switching states allow to reach the different intermediate points by two diodes connected in antiparallel. The circuit can be seen as a multiplexer which, depending on the state of the switches, connects the output to

Figure 2-11: Three-phase five-level scheme of a NPC [10]

the different voltage levels.

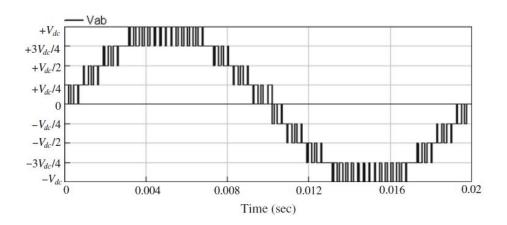

In figure 2-12, the line voltage waveform of this five-level converter is shown, which is a nine-level waveform. It can be noticed that the increase of the number of levels allows to get closer to a sinusoidal waveform.

Figure 2-12: Line voltage waveform of a five-level NPC [10]

#### 2.3.0.2 Flying capacitor

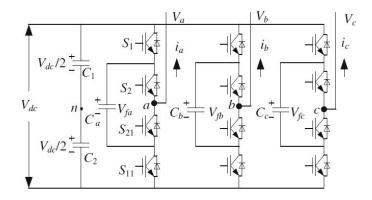

The second topology to be analyzed is the flying capacitor. The scheme of a three-phase three-level flying capacitor converter is shown in figure 2-13 and its switching scheme is shown in table 2.3.

Figure 2-13: Three-phase three-level scheme of a flying capacitor [10]

Table 2.3: Switching scheme for three-level flying capacitor [10]

| S | 1 | $S_2$ | $V_{an}$    | $C_a$           |

|---|---|-------|-------------|-----------------|

| 1 |   | 1     | $+V_{dc}/2$ | No charge (NC)  |

| 1 |   | 0     | 0           | Charging (+)    |

| 0 | ) | 1     | 0           | Discharging (-) |

| 0 | ) | 0     | $-V_{dc}/2$ | No charge (NC)  |

The operation principle, in this case, is the following: as in the previous case, connecting both upper switches connects to the positive terminal of the link, producing  $+V_{dc}/2$  at the output and the opposite for the lower switches (connects to the negative terminal and produces  $-V_{dc}/2$ ). However, in this case, there are different combinations to achieve the intermediate voltages (0, in this case). The voltage of the flying capacitor is  $V_{dc}/2$ , so we can either go from the positive terminal and pass through the capacitor (second combination in table 2.3) charging the flyting capacitor (taking into account the direction of the output current in figure 2-13) or go from the negative terminal (third combination in table 2.3) and discharge the capacitor.

This possibility to use different paths to charge/discharge the capacitors is really useful to give flexibility in the control of the flying capacitor voltages.

For higher number of levels the operation is similar (but with an important increase in the possible combination of switching states). In figure 2-14, the scheme of a three-phase five-level flying capacitor converter is shown (switching scheme in table 2.4).

Figure 2-14: Three-phase five-level scheme of a flying capacitor [10]

Table 2.4: Switching scheme for five-level flying capacitor [10]

| $S_1$ | $S_2$ | $S_3$ | $S_4$ | $C_{f1}$ | $C_{f2}$ | $C_{f3}$ | $V_{an}$         |

|-------|-------|-------|-------|----------|----------|----------|------------------|

| 1     | 1     | 1     | 1     | NC       | NC       | NC       | $+V_{dc}/2$      |

| 1     | 1     | 1     | 0     | NC       | NC       | +        |                  |

| 1     | 1     | 0     | 1     | NC       | +        | -        | $+V_{dc}/4$      |

| 1     | 0     | 1     | 1     | +        | -        | NC       | $  + v_{dc} / +$ |

| 1     | 1     | 1     | 0     | -        | NC       | NC       |                  |

| 0     | 0     | 1     | 1     | NC       | -        | NC       |                  |

| 0     | 1     | 0     | 1     | -        | +        | -        |                  |

| 0     | 1     | 1     | 0     | -        | NC       | +        | 0                |

| 1     | 0     | 0     | 1     | +        | NC       | -        |                  |

| 1     | 0     | 1     | 0     | +        | -        | +        |                  |

| 1     | 1     | 0     | 0     | NC       | +        | NC       |                  |

| 1     | 0     | 0     | 0     | +        | NC       | NC       |                  |

| 0     | 1     | 0     | 0     | -        | +        | NC       | $-V_{dc}/4$      |

| 0     | 0     | 1     | 0     | NC       | -        | +        | V dc/4           |

| 0     | 0     | 0     | 1     | NC       | NC       |          |                  |

| 0     | 0     | 0     | 0     | NC       | NC       | NC       | $-V_{dc}/2$      |

In this case, the charge of each capacitor is  $V_{dc}/4$ , so the voltages  $V_{f1}$ ,  $V_{f2}$  and  $V_{f3}$  will be  $3V_{dc}/4$ ,  $V_{dc}/2$  and  $V_{dc}/4$  respectively. So for example, for obtaining  $+V_{dc}/4$  at the output, the path can be positive terminal- $C_{f3}$  ( $V_{dc}/2 - V_{dc}/4$ ) charging  $C_{f3}$  (which is the second combination in table 2.4), positive terminal- $C_{f2}$ - $C_{f3}$  ( $V_{dc}/2 - V_{dc}/4$ ) charging  $C_{f2}$  and discharging  $C_{f3}$  (third combination in table 2.4) or two other combinations more. For 0 voltage, there are even more combinations (6), so the flexibility increases rapidly when increasing the number of levels.

The line voltage waveform of this five-level converter would be the same of the one shown in figure 2-12 for the NPC.

#### 2.3.0.3 Modular Multilevel Converters (MMC)

The two aforementioned topologies have different advantages and drawbacks, but they have one problem that makes them non suitable for many applications: they are not modular. MMC are much more interesting, because they have two advantages: in case you want to upgrade the system to higher rating, you just need to insert more submodules like the ones used in the system (they are equal) and in case some component fails, the system can still work, reducing its total rating.

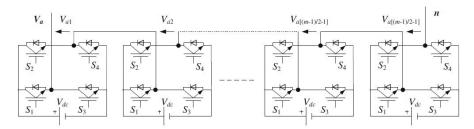

For the MMC, there are also different configurations. For example, the one shown in figure 2-15 with its corresponding waveform in figure 2-16.

Figure 2-15: General scheme of a MMC using full-bridge [10]

This configuration has many advantages but has one problem that makes it impossible to be used for most of the applications: it requires separated DC source for each full-bridge.

Taking into account all the problems that make the previous converters not suitable for our case (nonmodularity of NPC and flying capacitor and the necessity of

Figure 2-16: Output phase voltage waveform of an 11-level cascade inverter with 5 separate DC sources [10]

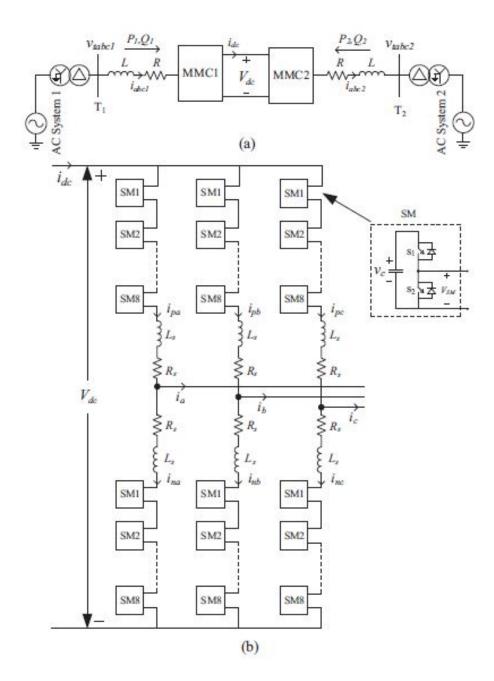

separated DC sources for the MMC using full-bridge) makes that the MMC using half-bridge, which is going to be explained now and whose scheme is shown in figure 2-15, is the one chosen for this kind of applications (and for our case).

The operation principle is simple. In each phase there are two branches (upper and lower) with different levels, each level with a capacitor with voltage of  $V_{dc}/N$ , being N the number of levels. These levels of each branch will act together as a

Figure 2-17: Schematic block diagram of MMC based HVDC system, (a) Single line diagram, (b) Internal circuit diagram of MMC converter station [11]

voltage source (which in the end will produce something close to a sinusoidal with a DC offset, being the voltage always positive). If we neglect the impedance and the resistance in the branch, the voltage output would be:

$$v_{ok} = V_{dc}/2 - v_{pk} = -V_{dc}/2 + v_{nk} (2.5)$$

Being  $v_{ok}$  the output voltage and  $v_{pk}$  and  $v_{nk}$  the voltage produced by the levels in the upper and the lower branch respectively.

With this, any voltage output could be produced, but the inductor in the middle has to be added in order to prevent surges due to the unbalance in the capacitor voltages (the voltage of each capacitor will not be exactly the desired one, so  $v_{pk}$  and  $v_{nk}$  will not be exactly the reference ones and there would be a shortcircuit in the output).

Apart from that, the inductor has two advantages more: limits current in faulty conditions and allows the control of current flowing inside the branch, without going to the output, which will allow the possibility of controlling capacitor voltages.

All the equations and the control of the system will be extensively explained in next chapter.

# MMC systems

In this chapter, all the equations of the system are going to be presented and the modulation technique is going to be explained. Then, the control strategy and its corresponding equations will be analyzed, finishing the analysis of all the system so that the results can be shown in next chapter.

### 3.1 Modelling of the system

The system explained in 2.3.0.3 can be approximated as the one shown in figure 3-1, where the n number of levels of each branch are substituted by a controllable voltage source.

Here it is important to remark the two assumptions that are done for this simplification: capacitance of the submodules is infinite (voltage in each level is constant an equal to the desired value) and number of levels is infinite (no harmonic distortion in the waveform produced by the levels of each branch). To compensate these assumptions done to eadily obtain the equations, a control of the capacitor voltage have to be added (to ensure capacitor voltage is close to the reference one) and a high number of levels and proper modulation is required. Both of them will be analyzed in later sections.

Now, all the equations of the system are going to be obtained (all the procedure and equations were extracted from [11]).

Figure 3-1: Single phase equivalent circuit of MMC [11]

If the inner difference current  $i_{diffk}$  (where k means the phase: a,b or c) is defined as:

$$i_{diffk} = \frac{i_{pk} + i_{nk}}{2} \tag{3.1}$$

The current in the positive and negative branch  $(i_{pk}$  and  $i_{nk})$  and the output current  $i_{ok}$  are related as:

$$i_{pk} = i_{diffk} + \frac{i_{ok}}{2} \tag{3.2}$$

$$i_{nk} = i_{diffk} - \frac{i_{ok}}{2} \tag{3.3}$$

The output voltage  $v_{ok}$  can be obtained from the DC link voltage  $V_{dc}$ , the upper and lower branch voltages  $(v_{pk}$  and  $v_{nk})$  and the voltage drop in the inductance  $L_s$  and the resistance  $R_s$ .

$$v_{ok} = \frac{V_{dc}}{2} - v_{pk} - L_s \frac{di_{pk}}{dt} - R_s i_{pk}$$

(3.4)

$$v_{ok} = -\frac{V_{dc}}{2} + v_{nk} + L_s \frac{di_{pk}}{dt} + R_s i_{pk}$$

(3.5)

By respectively suming and substracting equations 3.4 and 3.5, equations 3.6 and 3.7 can be obtained.

$$v_{ok} = e_k - \frac{L_s}{2} \frac{di_{ok}}{dt} - \frac{R_s}{2} i_{ok}$$

(3.6)

$$\frac{V_{dc}}{2} - \frac{v_{pk} + v_{nk}}{2} = L_s \frac{di_{diffk}}{dt} + R_s i_{diffk}$$

(3.7)

Being  $e_k$  the inner emf generated in phase k:

$$e_k = \frac{v_{nk} - v_{pk}}{2} \tag{3.8}$$

With equation 3.6 and considering that the connection to the grid voltage  $v_k$  is done by a series connection of  $R_g$  and  $L_g$ , equations 3.9 and 3.10 can be obtained.

$$v_k = v_{ok} - L_g \frac{di_{ok}}{dt} - R_g i_{ok} = e_k - (L_g + \frac{L_s}{2}) \frac{di_{ok}}{dt} - (R_g + \frac{R_s}{2}) i_{ok}$$

(3.9)

$$v_k = e_k - L\frac{di_{ok}}{dt} - Ri_{ok} \tag{3.10}$$

Where L and R are the equivalent inductance and resistance from the point of view of the output current control. It can be seen that the output current can be controlled acting over  $e_k$ .

The difference current  $i_{diffk}$  will cause also a differential voltage  $v_{diffk}$ , given by the following equation:

$$v_{diffk} = L_s \frac{di_{diffk}}{dt} + R_s i_{diffk} = \frac{V_{dc} - (v_{pk} + v_{nk})}{2}$$

(3.11)

With all the previous equations, the reference for the voltage of each branch can be obtained as shown in equations, where the subscript r means that is the reference and not the actual value.

$$v_{pk\_r} = \frac{V_{dc}}{2} - e_{k\_r} - v_{diffk\_r}$$

(3.12)

$$v_{nk\_r} = \frac{V_{dc}}{2} + e_{k\_r} - v_{diffk\_r}$$

(3.13)

It can be seen that since  $v_{diffk\_r}$  is substracted from both terms, it will not affect  $e_k$ , using the first for controlling the inner current of the branch (which will be used later for controlling the voltage in the capacitors) and the second for controlling the output voltage.

#### 3.1.1 abc to dq transformation

The matrix for the transformation from abc to dq0 and for the inverse transformation are shown in 3.14 and 3.15.

$$T = 2/3 \begin{bmatrix} sin(\Theta) & sin(\Theta - 2\pi/3) & sin(\Theta + 2\pi/3) \\ cos(\Theta) & cos(\Theta - 2\pi/3) & cos(\Theta + 2\pi/3) \\ 1/2 & 1/2 & 1/2 \end{bmatrix}$$

(3.14)

$$T^{-1} = \begin{bmatrix} sin(\Theta) & cos(\Theta) & 1\\ sin(\Theta - 2\pi/3) & cos(\Theta - 2\pi/3) & 1\\ sin(\Theta + 2\pi/3) & cos(\Theta + 2\pi/3)1/2 & 1 \end{bmatrix}$$

(3.15)

Using this transformation, the following equations are used to calculate the power:

$$P = 3/2(v_d i_d + v_q i_q + 2v_0 i_0) (3.16)$$

$$Q = 3/2(v_q i_d - v_d i_q) (3.17)$$

And for the current control the equation 3.10 for the three phases becomes the one shown in equations 3.18, 3.19 and 3.20 (this last one is for the zero component and it is not going to be used).

$$e_d - v_d + \omega L i_q = L \frac{di_d}{dt} + R i_d \tag{3.18}$$

$$e_q - v_q - \omega L i_d = L \frac{di_q}{dt} + R i_q \tag{3.19}$$

$$e_0 - v_0 = L\frac{di_0}{dt} + Ri_0 (3.20)$$

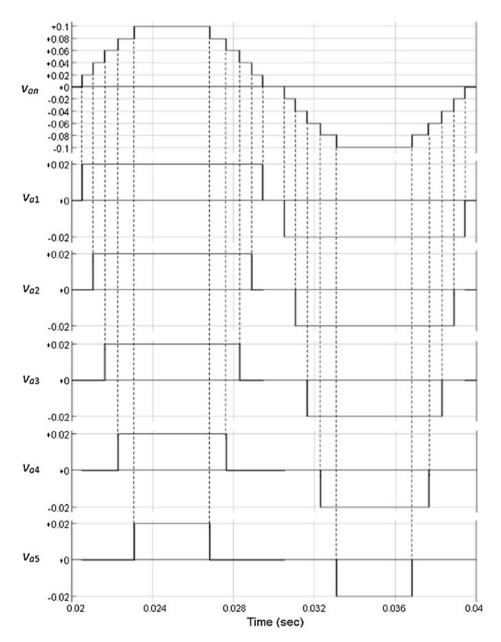

### 3.2 Modulation technique

The modulation technique is a bit different of the classical PWM but with some particularities. First of all, for this case the voltage produced for each branch is going to be always positive and, thus, the required carrier waveform too. Apart from that, the presence of more than one level means more than one carrier waveform will be required (one per level).

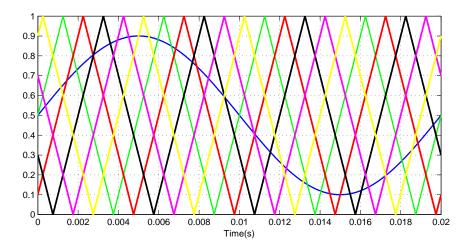

For an optimum reduction of harmonic distortion, the N carrier waveforms must have a phase shift of  $360^{\circ}/N$  [12]. This can be seen in figure 3-2, where the five carrier waveforms corresponding to a five-level MMC are plotted versus the modulating waveform. In figure 3-3 the resulting voltage is shown.

Apart from that, it is important to choose the phase-shift between the carrier waveforms of the upper and the lower branch. As explained in [12], there are two options for the selection of this angle: minimization of the harmonic content of the output voltage or minimizing the harmonic of the circulating current. In the case of HVDC, since the number of level is really high and the harmonic content of the output voltage is going to be small, the angle will be chosen to minimize the circulating current harmonic content. If N is even (as for our simulations), this angle will be 0 [12].

Figure 3-2: Modulating and carrier signals for a five-level MMC

Figure 3-3: Refence and resulting voltage

With this, we can already know the number of levels that have to be inserted. However, we still have to choose the inserted submodules in order to balance the voltage (all the capacitor in each branch having the same voltage).

For that purpose, a simple algorith is used. If n number of submodules have to be connected:

- If current  $(i_{pk} \text{ or } i_{nk})$  is positive (capacitors being charged), the n submodules with the lowest capacitor are connected.

- If current  $(i_{pk} \text{ or } i_{nk})$  is negative (capacitors being discharged), the n submodules with the highest capacitor are connected.

### 3.3 Control strategy

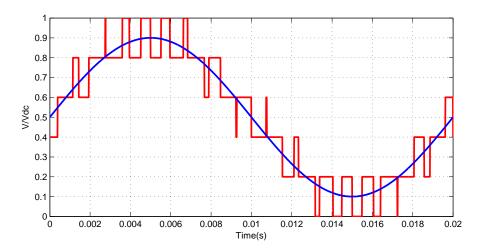

The control strategy followed for the system is really similar to the one explained in [11] and it is shown in figure 3-4.

Figure 3-4: Diagram of the control scheme (the image is a modification of the original in [11])

#### 3.3.1 Current control

The inner current control is obtained from equations 3.18 and 3.19, and we can appreciate the terms for feedforward compensation for the grid voltage and the coupling terms between d and q current equations.

For the tuning of both PI controllers, zero-pole cancellation is going to be used, as shown below (subscript for d and q is omitted because is the same for both axes).

$$C_i(s) = \frac{K_{pi}s + K_{ii}}{s} \tag{3.21}$$

$$G_i(s) = \frac{1}{Ls + R} \tag{3.22}$$

If we impose  $\frac{K_{pi}}{K_{ii}} = \frac{L}{R}$ , the pole in the plant is canceled with the zero of the controller, obtaining:

$$H_i(s) = \frac{C_i(s)G_i(s)}{1 + C_i(s)G_i(s)} = \frac{1}{1 + s\frac{R}{K_{i:i}}}$$

(3.23)

And the parameters of the regulator will be:

$$K_{ii} = 2\pi B W_i R \tag{3.24}$$

$$K_{pi} = 2\pi B W_i L \tag{3.25}$$

Where  $BW_i$  is the desired bandwith for the current loop and  $R = R_g + \frac{R_s}{2}$  and  $L = L_g + \frac{L_s}{2}$  are the equivalent resistance and inductance as explained in 3.9 and 3.10.

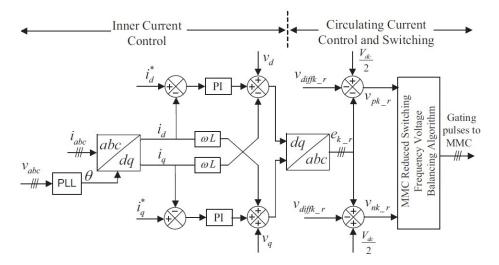

#### 3.3.2 Circulating current control

As explained in [11], voltage unbalances between the branches of each phase of the converter (due to charging and discharging of the capacitors) cause current circulation within the branches without affecting the output current.

It is necessary to minimize the currents in order to minimize the losses in the converter (and also to create less ripple on the capacitor voltages).

As stated in [11], these currents have two main components: a DC one, which is required to have power transfer with the DC link, and a negative sequence component with twice the fundamental frequency, as shown in the equations below.

$$I_{diffa} = \frac{I_{dc}}{3} + I_{ccs} sin(2\omega t + \phi)$$

(3.26)

$$I_{diffa} = \frac{I_{dc}}{3} + I_{ccs} sin[2(\omega t - \frac{2\pi}{3}) + \phi]$$

(3.27)

$$I_{diffa} = \frac{I_{dc}}{3} + I_{ccs} sin[2(\omega t + \frac{2\pi}{3}) + \phi]$$

(3.28)

As mentioned in section 3.1 and equations 3.11, 3.12 and 3.13, the differential

voltage  $v_{diffk}$  was going to be used the inner difference current.

The equations 3.11 in the dq reference for twice the frequency are:

$$v_{diffd} = R_s i_{diffd} + L_s \frac{di_{diffd}}{dt} + 2\omega L_s i_{diffq}$$

(3.29)

$$v_{diffq} = R_s i_{diffq} + L_s \frac{di_{diffq}}{dt} - 2\omega L_s i_{diffd}$$

(3.30)

$$v_{diff0} = R_s i_{diff0} + Ls \frac{di_{diff0}}{dt}$$

(3.31)

The control sheeme is shown for the dq axis in figure 3-5.

Figure 3-5: Control of the circulating current (the image is a modification of the original in [11])

The zero component of the current was not included in the control in [11]. However, it is interesting to control it to ensure that the DC component of the 3 differential currents are  $I_{dc}/3$  (if not, some oscillations appear in the DC current).

The control is the same that for d and q axis in 3-5 but without the feedforward term. It was seen in the simulations, that adding this control the ripple in the DC link current was significantly reduced.

The PI tuning is the same as for the output current control, but using  $R_s$  and  $L_s$  instead of R and L in equations 3.24 and 3.25.

#### 3.3.3 Active and reactive power control

For the control of the active and reactive power, the strategy followed in [6] was used.

The control diagram of the active and reactive power part is shown in figures 3-6 and 3-7, where  $\tau_i$  is the time constant of the current loop (inverse of  $2\pi BW_i$ ).

Figure 3-6: Diagram of the active power control loop

Figure 3-7: Diagram of the reactive power control loop

The same method used for the PI tuning in the current control loop will be used now.

$$C_P(s) = \frac{K_{pP}s + K_{iP}}{s} \tag{3.32}$$

$$G_P(s) = 3/2V_d \frac{1}{\tau_{is} + 1} \tag{3.33}$$

If we impose  $\frac{K_{pi}}{K_{ii}} = \tau_i$ , the pole in the plant is canceled with the zero of the controller, obtaining:

$$H_P(s) = \frac{C_P(s)G_P(s)}{1 + C_P(s)G_P(s)} = \frac{1}{1 + s\frac{2}{3V_dK_{iP}}}$$

(3.34)

And the parameters of the regulator will be:

$$K_{iP} = \frac{4\pi B W_P}{3V_d} \tag{3.35}$$

$$K_{pi} = \frac{8\pi^2 B W_P B W_i}{3V_d} {3.36}$$

Where  $BW_P$  is the desired bandwith for the power loop and  $V_d$  the rated voltage for the d axis (since  $v_q$  is going to be 0 because of the PLL in 3-4,  $V_d$  rated value is the peak nominal value of the phase voltage).

#### 3.3.4 Coordinated control of the converters

So far, the control of the individual converters has been explained. Now, the coordination of both converters is going to be analyzed.

Similarly to the thyristor-based system case, the converter in mainland will be in charge of controlling the DC link voltage. For that purpose, the power reference of that converter is controlled to vary the DC link voltage (since the power transfer direction is from the DC link to the AC network, if the power increases, the DC link voltage decreases and vice versa). Figure 3-8 shows the control diagram for this DC link voltage.

Figure 3-8: Diagram of the DC link voltage control loop

Since the transfer function, in this case, is not linear, the process of tuning of the PI is not so straightforward and it was done manually.

For the reactive power of the mainland converter and for both active and reactive power of the converters in the islands (Corsica and Sardinia), the reference can be set freely according to the requirements in the three grids.

Here, it can be seen one of the main advantages of MMC compared to thyristors. Meanwhile in the thyristor case, only the active power in the islands was controlled and the converters in the three terminals were consuming reactive power, in this system the reactive power can be controlled too, including the one in mainland and allowing the possibility of producing instead of consuming (which, in general, will be more convenient for the grid).

### Simulation

In this chapter, the simulation results are going to be presented. For that purpose, the data of the system was collected and is shown in the following section.

For this simulation, only the two main terminals of the system (Sardinia and mainland Italy) are going to be used. However, the operation with the third terminal would be exactly the same (if the rated power and currents are not exceeded), since the two converters in the island act independently (they only use the DC link from the rest of the system) and the third terminal from the point of view of the mainland converter (controlling DC link voltage, which means providing the power demanded by the other converters) will be just an extra load.

### 4.1 System data

The data from the current system was obtained from [13].

The system is rated for 300MW, 1500A and 200kV (in the thyristor-based system it was required to invert DC link polarity to invert power flow, so the system was design for that; however, using MMC this polarity change is not needed any more).

The AC network data are:

• Mainland: 400kV, short circuit capacity 6000MVA.

• Sardinia: 400kV, short circuit capacity 1350MVA.

• Corsica: 90kV, short circuit capacity 120MVA.

The transformer used for the thyristor case was different, because that kind of converter required a three-winding transformer with a especial configuration. For this new case, the transformer has to be two-windings with delta-star configuration.

Thus, a new transformer is required, but for the simulation the same approximate values (short-circuit impedances of 0.17p.u.) were used:

- Italy and Sardinia: rated power 364.8MVA, rated voltages 400kV and 100kV.

- Corsica: rated power 75MVA, rated voltages 90kV and 100kV.

And the DC line is composed by two parallel and equal lines, going from mainland Italy to Corsica with 22km overhead lines and 105km submarine cables and from Corsica to Sardinia: 156km overhead, 16km submarine and 86km overhead, having the conductors the following characteristics:

- Overhead conductors:  $755mm^2$  ACSR, with a resitance of  $0.0374\Omega/km$ .

- Submarine cable: solid copper conductor of  $683mm^2$  ACSR, with a resitance of  $0.0417\Omega/km$ .

The resistance of the connection to ground in the three terminals was neglected in the simulation.

Apart from that, comparing with other similar projects ([6] and [4]) the parameters of the converters were selected.

The branch resistance and inductance are  $1\Omega$  and 30mH and the ones for the connection to the AC system (secondary of the transformer) are  $0.25\Omega$  and 16mH.

The total capacitance of the branch was chosen to be  $100\mu F$  and the capacitance placed in each terminal of the DC link (to minimize ripple)  $500\mu F$ .

Finally, the bandwidth of the output and the difference current control loop is 300Hz, the one for the active and reactive loop is 60Hz and the parameters of the DC link voltage regulator are  $K_{pV} = 3.0781 \cdot 10^4$  and  $K_{iV} = 3.0781 \cdot 10^7$ .

#### 4.2 Results

The results of the simulation are going to be shown now. The simulations where done using Matlab/Simulink.

For the simulation 20 levels in each branch are going to be used, although the final number of levels would be higher (around 120-130), for speeding up the simulations.

The first simulation done was a step of 100MW for the power demand in Sardinia.

In figure 4-1, the step is shown together with the actual power received to Sardinia AC grid. The converter is able to control the power in a fast (less than 10ms to reach the final value) and accurate way (no error), although it has some noise.

Figure 4-1: Active power received by Sardinia AC grid

In figure 4-2, the voltage at the connection to the grid in Sardinia is shown and we can see that the waveforms are really close to a sine wave, although it has some noise.

The total harmonic distortion (THD) was found to be 1.83%.

The current waveform can be seen in figure 4-3 and we can appreciate that the waveform are almost perfect sine wave, having a THD of only 0.74%.

Figure 4-4 shows the difference and DC current. As mentioned in section 3.3.2, if this circulating current is not controlled properly, it appears an importan inverse sequence component of twice the fundamental frequency. In the figure, we can appreciate that the second component is not significant and it only has some oscillations

Figure 4-2: Voltage at the connection to the grid

Figure 4-3: Current at the connection to the grid

during the transient.

Even if the current seems so noisy, the THD is only 7.21% when the steady-state is reached (last cycle shown in the figure), so the circulating current control design can be considered to be successful.

In figure 4-4, the current in DC link (at the Sardinia converter) is shown together with the desired value  $(P_{ref}/V_{dc})$ . As mentioned in section 3.3.2, the control of the DC component of the circulating current is advisable in order to have a current in the DC link really close to a DC current.

The DC link current has noise too and with similar harmonic distortion, having a THD of 6.16%(difference current and DC link current are very related as shown in

Figure 4-4: Phase a difference current in Sardinia converter

Figure 4-5: DC link current at Sardinia terminal and desired value

equations 3.26, 3.27 and 3.26).

Figure 4-6 shows the voltage of three different capacitor in the same branch.

The first thing to observe is that the selection of the inserted capacitors works perfectly, because the voltage on all the capacitors of the branch is the same.

Second thing to observe is that the control scheme designed is able to mantain the capacitor voltage to the reference level  $(V_{dc}/N = 10kV)$  and to reduce the ripple (first harmonic has a peak value of 235V and second harmonic 65V).

Another simulation was carried out in order to check that, as mentioned when talking of the advantages of MMC, both converters of the system can control the reactive power transfer with the AC grid.

Figure 4-6: Capacitor voltage in one of the branches

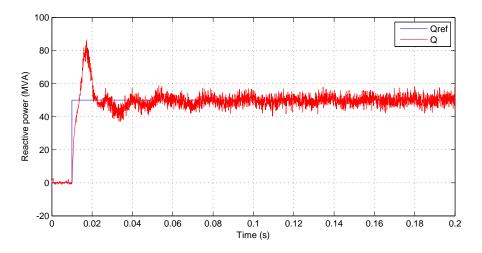

In figures 4-7 the active power received by the Sardinia AC network is shown and in figures 4-8 and 4-9 the reactive power in the AC network of Sardinia (sending) and mainland Italy (receiving).

Figure 4-7: Active power received by Sardinia AC grid

As expected, the system is able to control, apart from the active power in Sardinia, the reactive power in both converters, both for producing or consuming, which is a really importan advantage compared to the current system.

Figure 4-8: Reactive power received by Sardinia AC grid

Figure 4-9: Rective power received by Italy AC grid

### Conclusions

### 5.1 MMC vs. Thyristor based

As seen in the previous chapters, there are many advantages in the MMC that make the refurbishment of the system really interesting if economically feasible.

First of all, the system controllability is much higher than in the thyristor case. The most direct and important advantage of this controllability is the posibility to control the reactive power in all the converters. Meanwhile MMC system is able to either produce or consume reactive power in each terminal (within the rated values), the thyristor system is always consuming. This means a worse operation of the system and also economic issues, since reactive power compensation equipment is required, which means investment (for the installation and, now, for the maintenance) and more losses in the system.

Besides that, the higher controllability allows to minimize harmonic content in the inner circulating current and the DC link current. This also means less losses and less wearing in the components of the system.

Apart from that, the presence of a high number of levels means the distortion is importantly reduced. For the simulation only 20 levels were used (5 or 6 times less than the real system would have) and the harmonic content in the system is incredibly low (THD of the output curren of 0.74%).

This good operation in terms of harmonic distortion means that no filter is required

in the system. As for the reactive power compensation, this means less investment and less losses, apart from less wearing in some equipment especially sensitive to harmonics (like transformers).

Taking all of this into account, it is clear that the advantages of MMC against thyristors are really important and that the refurbishment should be taken seriously into consideration if the investment is feasible.

### 5.2 Degree of fulfilment of the initial objectives

The main objective of the work was completed in a successfully, achieving a really complete model of the system and a deep understanding of it.

However, some other objectives of the work were not achieved:

- The comparison of the designed system with the current one, mainly due to the lack of some information required for the proper simulation of the current systems (like filters, for example) which we did not manage to obtain from the company.

- Faulty conditions were not tested: the idea was to compare both systems reaction against faulty conditions.

However, the overall assessment of the work is positive, since the work on the modelling, control and simulation of the system was very complete.

# Future development

As future improvements of the work, apart from completing the objectives that were not achieved up to now, there are some other interesting tasks to be done.

- Study ways of working in overmodulation and how to control it. Like explained in [6], third harmonics can be inserted in the voltages to reduce the peak of the modulating waveform (3rd harmonic does not affect the final operation of this system) in order to be able to reach higher peak voltage.

- Analyze deeply the components selection and sizing to find the optimum compromise between performance and price.

- Study more extensively the PI tuning to optimize the control system operation.

Once all the above things were completed, the next objective would be to build a prototype to check the system in real operation before considering the final investment.

# Quality report

The global development of the project was done in a satisfactory way, but there were some problems that slow it down.

The main problem was the lack of communication from the company. Some information was requested with no repplies.

This lack of information slowed down the process and, from our part, the reaction to that problem was not the proper one, because we got stucked on the same problem, trying to compensate the missing information, instead of continuing with the rest of the work until receiving the information (which, in fact, was never received).

Apart from that, from the current perspective, some schedule would have been convenient for a better fulfilment of the objectives.

As mentioned for the problem of lack of information, it slowed down the process a lot and maybe some milestones in the schedule would have helped to realized on this and move on for a better use of the available time.

Despite this organizational problems, the technical and academic part of the work was very beneficial for the work with good resources for completing the thesis (good academic resources, like books and papers, for the understanding of the system).

## **Bibliography**

- [1] Siemens. HVDC History. https://www.energy.siemens.com/mx/en/power-transmission/hvdc/applications-benefits/hvdc-history.htm#content=1882%20%E2%80%93%201910%20First%20HVDCs

- [2] Jos Arrillaga. High Voltage Direct Current Transmission. 2nd Edition. Page 1. 1998.

- [3] Carlos Castillo Bonilla and Shweta Merilyn Tigga. Design and performance comparison of Two-level and Multilevel Converters for HVDC Applications. Department of Energy and Environment. Division of Electric Power Engineering. Chalmers University of Technology. Göteborg, Sweden, 2011.

- [4] Nicola Serbia. Modular Multilevel Converters for HVDC power stations. Engineering Sciences [physics]. Institut National Polytechnique de Toulouse INPT, 2014. English.

- [5] AB. HVDC: Economic and environmental advantages. http://new.abb.com/systems/hvdc/why-hvdc/economic-and-environmental-advantages

- [6] Marco Gambacorta. Analisi ed Applicazioni di Convertitori MMC alla Trasmissione in Corrente Continua. Faculty of Civil and Industrial Engineering. University of Rome "La Sapienza".

- [7] The Electric Online. HVDC. http://tijarohonline.blogspot.com.es/2011/01/hvdc.html

- [8] Mei Li. Multi-pulse SCR Rectifiers. Ryerson University. Toronto, Ontario, Canada, 2005

- [9] Ned Mohan, Tore M. Undeland and William P.Robins. Power Electronics: Converters, Applications and Design. Second Edition. 1995.

- [10] Shukla A., Nami A. (2015) Multilevel Converter Topologies for STATCOMs. In: Shahnia F., Rajakaruna S., Ghosh A. (eds) Static Compensators (STATCOMs) in Power Systems. Power Systems. Springer, Singapore

- [11] N. Geddada, A. Ukil and Y. M. Yeap. Circulating current controller in dq reference frame for MMC based HVDC system. IECON 2016 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, 2016, pp. 3288-3293.

- [12] B. Li, R. Yang, D. Xu, G. Wang, W. Wang and D. Xu. Analysis of the Phase-Shifted Carrier Modulation for Modular Multilevel Converters. IEEE Transactions on Power Electronics, vol. 30, no. 1, pp. 297-310, Jan. 2015

- [13] Cigre. Compendium of all HVDC projects. http://b4.cigre.org/ Publications/Other-Documents/Compendium-of-all-HVDC-projects