# Optimized design of a high input-voltage-ripple-rejection converter for LED lighting

M. Arias, I. Castro, D.G. Lamar, A. Vázquez, J. Sebastián

Electronic Power Supply Research Group; University of Oviedo; Campus de Viesques s/n; 33204 SPAIN

mail: ariasmanuel@uniovi.es

Abstract – The Asymmetrical Half Bridge (AHB) converter has been deeply analysed as second stage in acdc LED drivers. Galvanic isolation, high reliability and high efficiency are their main advantages while a limited duty cycle range (i.e., 0-0.5) and a poor dynamic behaviour are their main disadvantages. As second stage of an LED driver, the most demanding requirement for its control loop is cancelling the low-frequency ripple introduced by the first stage. According to its limited maximum attainable bandwidth, this is normally achieved by implementing a feedforward loop. Nonetheless, the static gain of the standard AHB converter presents a non-linear relation between the output voltage and the duty cycle. As a consequence, the effectiveness of this feedforward loop is limited. In this paper, the use of the Zeta Asymmetrical Half Bridge (ZAHB) converter as second stage of an LED driver is analysed and an optimized design is proposed. Regarding its advantages, it presents an extended duty cycle range (theoretically, 0-1.0). Besides, it presents a linear relation between the output voltage and the duty cycle. Therefore, although its dynamic behaviour is still limited, it can perfectly cancel the low-frequency ripple introduced by the first stage of the LED driver by means of a straightforward feedforward loop. The optimized design proposed in this paper is focused on minimizing the losses in the magnetic components (transformer and inductor) by wisely choosing the value of the two turns ratios of the transformer.

Keywords: Asymmetrical Half Bridge, feedforward, lowfrequency ripple, optimized magnetic design.

# I. INTRODUCTION

Light Emitting Diodes (LED) are becoming a wellstablished technology in lighting applications due to their many advantages [1]. Their luminous efficacy, already in the market, is as high as 200 lm/watt. Their reliability is also very high, with lifespans of 50,000 hours or even higher [2]. Other important advantages are their wide colour variety [3], the easiness of performing light dimming [4], the low environmental impact, their possible use in Visible Light Communication (VLC) [5]-[7], etc.

Regarding LED drivers, two different approaches can be found in literature and industry. On one hand, one-stage topologies [8]-[15], whose reduced size and cost make them the preferred option for retrofit lamps and other low-cost applications. Their main disadvantage is a shorter lifespan, derived from the fact that their only option in order to reduce the low-frequency ripple in the output is using electrolytic capacitors (in the case of ac-dc drivers). Moreover, their efficiency is also lower in comparison to two- or three-stage topologies because a single converter has to be designed for performing several tasks (output voltage regulation, power factor correction and, in some cases, providing galvanic isolation). On the other hand, two- and three-stage topologies [16]-[19] are the preferred option for high-quality applications, in which the cost is less important than other features like lifespan. In general, their efficiency is also higher because each stage can be optimized for performing just one task. Their main disadvantage, apart from cost and size, is that their use makes sense, generally speaking, only in ac-dc drivers: Power Factor (PF) correction is performed by the first stage while the second or third stages are in charge of cancelling the low-frequency ripple.

The Asymmetrical Half Bridge (AHB) converter [20]-[22] represents a suitable option for the second stage of an ac-dc driver. Its efficiency is very high due to the possibility of reaching Zero-Voltage Switching (ZVS) in primary switches [23]-[27]. Due to the control scheme of this topology and the limited output-voltage range required in LED drivers, its output filter can be very small. The voltage across the transformer secondary side, due to the aforementioned control scheme, also makes self-driven synchronous rectification easy to be implemented, leading to high efficiency in low-output-voltage applications [28], [29]. Its transformer, apart from providing galvanic isolation, leads to high step-up or -down conversion ratios without loss of efficiency. Obviously, the AHB converter also presents some disadvantages. The duty cycle range is limited to 0.0-0.5. This can be partially solved using the two-transformer AHB converter [30]-[31], in which the output inductor is replaced with an additional transformer connected in series to the original one. The resulting maximum duty cycle is higher than 0.5 but still lower than unity. Another important drawback of this family of converters is the resonance between the input capacitors and the magnetizing inductance [32]-[35]. This resonance is located at low frequencies and, as a consequence, limits the attainable bandwidth of the control loop. In general, this is not a problem for controlling the voltage/current of the LEDs as they can be considered as non-demanding loads regarding the dynamic behaviour of the driver. Nonetheless, cancelling the low-frequency ripple may require a bandwidth higher than the one that can be reached without compromising stability. To overcome this problem, a feedforward loop may be implemented in the control of the AHB converter [29], [36]. In this way, the feedforward loop attenuates the ripple and the feedback loop bandwidth can be tailored as much as required to reach stability and a reasonable emitted light regulation. Nevertheless, the dc gain of the AHB converter is not linear. The feedforward loop has to be then optimized for a single operating point (i.e., given values of the input and the output voltage). As a consequence, the low-frequency ripple cannot

be totally cancelled and this cancellation worsens as the operating point gets farther from the one used in the feedforward loop calculation.

In this paper, the Zeta AHB (ZAHB) converter is analysed as second stage of an LED driver as a way of overcoming the two main disadvantages of the traditional AHB converters [37], [38]. Its maximum theoretical duty cycle does reach unity. Moreover, the dc gain of this converter is linear. Therefore, although resonances still limits its maximum attainable bandwidth, the feedforward loop can perfectly cancel the low-frequency ripple at any operating point. This makes the ZAHB converter a perfect second stage topology for LED drivers, due to the especial demands imposed to the driver by the load. An optimized design guideline is also proposed for this converter. It is based on choosing the optimum conversion ratios of the transformer windings in order to minimize losses of the magnetic components. As will be seen, the effectiveness of the feedforward loop and the validity of the proposed design methodology are independent from the first-stage topology of the driver. Therefore, for the sake of clarity, in this paper only the output-voltage characteristics of the first stage (average value and low-frequency ripple) are considered (they are input variables for the design procedure).

The paper is organized as follows. In section II, the analysis of the feedforward loop is presented. In section III, the proposed optimized design is explained, based on the equations derived in section VI. Section IV presents the experimental results obtained with a 50-W prototype. Finally, section V gathers the conclusions extracted from this work.

### II. ANALYSIS OF THE ZAHB CONVERTER AND ITS FEEDFORWARD LOOP

This section will only describe the proposed topology briefly, as this has already been done in [37]. Nevertheless, this description will include the equations that are necessary for the analysis of the feedforward loop. This section will also include a comparison of the feedforward loop when implemented in the traditional AHB converter and in the ZAHB one.

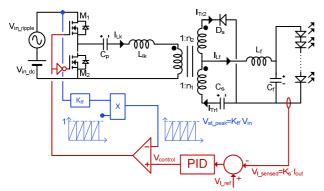

The schematic of the ZAHB converter is shown in Fig. 1. The MOSFETs have complementary driving signals, which means that one of them is always turned on (neglecting the dead times needed for achieving ZVS). As a

Fig. 1. Schematic of the ZAHB converter with a simple feedforward loop (blue) and a standard feedback loop (red).

consequence, the volt-second balance in the transformer and in the output inductor (assuming that the leakage inductance is negligible) leads to the following equations:

$$V_{Cp} = V_{in} D , \qquad (1)$$

$$V_{Cs} = V_{in} D n_t, \qquad (2)$$

$$V_{out} = V_{in} D n_t, \qquad (3)$$

where  $V_{Cp}$  and  $V_{Cs}$  are the voltages of the capacitors  $C_p$  and  $C_s$ ,  $V_{in}$  is the input voltage,  $V_{out}$  the output voltage, and  $n_t$  is the overall turns ratio of the transformer (i.e.,  $n_t=n_1+n_2$ ).

Equation (3) is the dc static gain of the ZAHB converter, while the static gain of the traditional AHB converter is:

$$V_{out\_AHB} = V_{in} D (1-D) n_t.$$

(4)

Considering that the purpose is implementing the second stage of an LED driver, the output current may be more interesting than the output voltage. Therefore, equations (3) and (4) may be rewritten as follows:

$$I_{out} = \frac{V_{in} D n_t - V_{\gamma\_string}}{R_{d\_string}},$$

(5)

$$I_{out\_AHB} = \frac{V_{in} D (1-D) n_t - V_{\gamma\_string}}{R_{d\_string}},$$

(6)

where  $V_{\gamma\_string}$  and  $R_{d\_string}$  are the knee voltage and the dynamic resistance of the whole LED string.

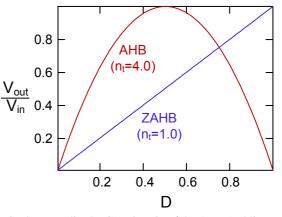

Comparing (3) and (4), or (5) and (6), it can be easily seen that for the same design conditions, the dc static conversion ratio is higher in the ZAHB converter, as stated in [37], due to the factor (1-D), which is always lower than unity. In Fig. 2, the normalized dc static voltage gain is represented for an AHB and a ZAHB converter. For the sake of clarity, this figure is based on equations (3) and (4), and not on (5) and (6), as a way of avoiding the knee voltage and the dynamic resistance influence in the explanation, which are not necessary to understand the reasons for the better performance of the feedforward loop in the ZAHB converter. Both converters are designed to obtain the same output voltage at their corresponding maximum duty cycle. As can be seen, the AHB converter reaches its maximum at D=0.5, whereas the ZAHB converter reaches the maximum output voltage at D=1.0 using a transformer with a turns ratio four

Fig. 2. Normalized DC static gain of the AHB (red line) and the ZAHB (blue line) converters for the same design conditions.

times lower. This reduced turns ratio leads to several advantages, such as reduction in the magnetizing current offset or reduction in the voltage stress in the diode. Nevertheless, the most important fact for LED lighting is that the ratio between the output voltage and the duty cycle is linear in the ZAHB converter and not in the standard AHB converter. As a consequence, the implementation of the feedforward loop in the first one (i.e., ZAHB converter) is easier than in the second one (i.e., standard AHB converter). The most common and straightforward implementation of the feedforward loop implies that the peak value of the triangular or sawtooth waveform used in the PWM generator is proportional to the input voltage:

$$D = \frac{V_{control}}{V_{st\_peak}} = \frac{V_{control}}{K_{ff}} \,, \tag{7}$$

where  $V_{control}$  is the control voltage generated by the feedback control loop,  $V_{st\_peak}$  is the peak value of the sawtooth voltage and  $K_{ff}$  is the constant of proportionality of the feedforward loop.

In the traditional AHB converter (whose static gain is shown in (4)), the use of this feedforward loop (equation (7)) leads to the following output voltage equation:

$$V_{out\_AHB} = V_{in} \frac{V_{control}}{K_{ff\_AHB} V_{in}} \left( 1 - \frac{V_{control}}{K_{ff\_AHB} V_{in}} \right) n_{t} = \frac{V_{control}}{K_{ff\_AHB}} \left( \frac{K_{ff\_AHB} V_{in} - V_{control}}{K_{ff\_AHB} V_{in}} \right) n_{t}$$

$$(8)$$

where  $K_{ff\_AHB}$  is  $K_{ff}$  in the feedforward loop of the traditional AHB converter. This equation shows that the output voltage still depends on the input voltage. Using (6), the feedforward loop would lead to the following expression of the output current when the AHB converter is supplying an LED string:

$$I_{out\_AHB} = \frac{\frac{V_{control}}{K_{ff\_AHB}} \left(\frac{K_{ff\_AHB} V_{in} - V_{control}}{K_{ff\_AHB} V_{in}}\right) n_t - V_{\gamma\_string}}{R_{d\_string}}$$

(9)

When the converter is used as second stage of a PF Corrector (PFC),  $V_{in}$  can be expressed as:

$$V_{in} = V_{in_nom} \left( 1 + r \sin(2 \omega t), \right), \tag{10}$$

where r is the relative value of the low-frequency ripple and  $\omega$  is the pulsation of the grid.

The value of  $K_{ff\_AHB}$  should be tuned using (8) or (9) for a given operating point; for instance, the nominal input and output voltages (or nominal input voltage and output current):

$$K_{ff\_AHB} = V_{control\_nom} n_t \frac{1 \pm \sqrt{1 - 4 \frac{V_{out\_AHB\_nom}}{V_{in\_nom} n_t}}}{2 V_{out\_AHB\_nom}} =$$

$$= V_{control\_nom} n_t \frac{1 \pm \sqrt{1 - 4 \frac{I_{out\_AHB\_nom} R_{d\_string} + V_{\gamma\_string}}}{V_{in\_nom} n_t}}{2 (I_{out\_AHB\_nom} R_{d\_string} + V_{\gamma\_string})}$$

(11)

As can be seen, the value of  $K_{ff\_AHB}$  is dependent on the input-voltage value chosen for the calculation (in this case,  $V_{in\_nom}$ ). This has several disadvantages. The first one is that the low-frequency ripple is not perfectly cancelled because  $K_{ff\_AHB}$  is constant while its value should actually change according to  $V_{in}$ .

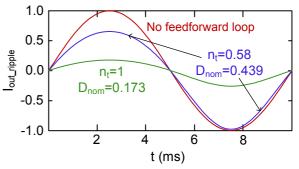

The second one, related to the first one, is that the closer the duty cycle to 0.5, the worse the ripple cancellation with a linear feedforward loop (as the one presented in (7)). This can be easily understood paying attention to Fig. 2. In the vicinity of 0.5, the slope of the static gain is quite low. Therefore, large variations of the duty cycle are required for cancelling the low-frequency ripple. On the other hand, at lower ranges of the duty cycle, the dc gain gets a higher slope. Smaller variation of the duty cycle are then required for cancelling the same low-frequency ripple. One consequence of this can be seen in Fig. 3, where the output current ripple of an AHB converter operating at a higher nominal duty cycle is worse than the ripple of another AHB converter operating at a lower nominal duty cycle. Nevertheless, the last one requires a transformer with a higher turns ratio, which implies higher stress in components and lower efficiency. Another consequence, the worst one, is that the variations in the slope of the dc gain also leads to an uneven effect of the feedforward loop due to its linear behaviour (see (7)). As can be seen in Fig. 3 for the D<sub>nom</sub>=0.439 design, the positive part of the ripple is smaller than the negative one. This is because when the ripple is negative, the feedforward loop needs to increase the duty cycle, moving to ranges in which the dc gain slope is lower. Therefore, large variations of the duty cycle are required. When the ripple is positive, the feedforward loop reduces the duty cycle, moving to ranges in which the slope is higher and, consequently, the required variation is smaller. Nonetheless, the feedforward loop is linear, so positive and negative parts of the ripple are attenuated by means of equal variations of the duty cycle (with different sign).

This problem of the traditional AHB converters with the feedforward loop and the low-frequency ripple has been addressed in [29] and [36]. In the first one, the authors propose a double feedforward loop, so it has a different gain for the positive and the negative part of the ripple. In [36], the authors propose a digital feedforward loop based on a low-cost microcontroller. Although both solutions lead to an improvement in the feedforward loop, the ripple cancellation

Fig. 3. Normalized output current ripple of the standard AHB converter with no feedforward loop (red) with feedforward loop with a nominal duty cycle equal to 0.439 (blue) and with a nominal duty cycle equal to 0.173.

is still no perfect and the cost and complexity of the proposed systems are considerably increased.

For the ZAHB converter, the simple feedforward loop implementation also satisfies (7); therefore (3) turns into:

$$V_{out} = V_{in} \frac{V_{control}}{K_{ff_{-}ZAHB} V_{in}} n_t = \frac{V_{control}}{K_{ff_{-}ZAHB}} n_t$$

(12)

In the same way, (5) turns into:

$$I_{out} = \frac{\frac{V_{control}}{K_{ff-ZAHB}} n_t - V_{\gamma_{-}string}}{R_{d_{-}string}}$$

(13)

The value of  $K_{\rm ff_ZAHB}$  can be defined considering any operating point (for instance, the nominal one):

$$K_{ff_{-ZAHB}} = \frac{V_{control_nom}}{V_{out_nom}} \quad n_t =$$

$$= \frac{V_{control_nom}}{I_{out_{-AHB_nom}} R_{d_{-string}} + V_{\gamma_{-string}}} \quad n_t,$$

(14)

leading to the following static gains:

$$V_{out} = \frac{V_{control}}{V_{control\_nom}} V_{out\_nom}$$

(15)

$$I_{out} = \frac{\frac{V_{control}}{V_{control\_nom}} \left( I_{out\_AHB\_nom} R_{d\_string} + V_{\gamma\_string} \right) - V_{\gamma\_string}}{R_{d\_string}}$$

(16)

The output voltage and the output current are now completely independent from the input voltage, but they still can be controlled by the feedback loop by means of  $V_{control}$ .

This automatic cancellation of the low-frequency ripple represents a great advantage of the ZAHB converter when used in LED lighting applications. The control transfer function of the ZAHB converter (duty cycle to output voltage or current) presents the typical resonance between the input capacitor and the magnetizing inductance of the transformer, which is normally located at very low frequencies. As a consequence, the maximum attainable bandwidth of the feedback loop is not always high enough as to cancel the low-frequency ripple introduced by the first stage of the LED driver (i.e., a PFC without electrolytic capacitors). Thanks to the linearity in the dc static gain, it is possible to use a simple feedforward loop to cancel the effect of the low-frequency ripple, leaving the feedback loop in charge of just controlling the emitted light of the lamp. In this way, the feedback loop can be slow enough to assure stability just because in many situations, the regulation of the emitted light does not required very fast responses.

# III. OPTIMIZED DESIGN OF THE ZAHB CONVERTER

For the sake of clarity, this section will not present the development of the equations used in the optimized design. That is included in section VI, and the explanation performed in this section will be based on the resulting final equations. The optimized design proposed in this section looks for the reduction in the overall losses of the converter. As will be seen, this is achieved by wisely choosing the value of  $n_1$  and  $n_2$  for reducing the overall losses in the two magnetic components of the topology.

According to (3), the overall turns ratio of the transformer,  $n_t$ , can be expressed as the required turns ratio in order to obtain the nominal output voltage for the maximum attainable duty cycle when the input voltage is at its minimum value (due to the low-frequency ripple). Theoretically, the maximum duty cycle is unity in the ZAHB converter, but the dead times for achieving ZVS should be considered. Other effects derived from the leakage inductance and the operation principle of the converter may also lead to a reduction of the effective duty cycle. Considering (10), the value of  $n_t$  can be expressed as:

$$n_t = \frac{V_{out\_nom}}{V_{in} \ (1-r) \ D_{max}} \tag{17}$$

where  $D_{max}$  is the maximum attainable duty cycle.

Once  $n_t$  is defined, the maximum voltage withstood by the diode  $D_s$  is also defined:

$$V_{Ds} = (V_{in} - V_{Cp}) \quad n_t + V_{Cs} = V_{in} \quad n_t$$

(18)

Also, the voltage withstood by the MOSFETs is limited to  $V_{in}$ , as in any half-bridge structure, and the average voltages of capacitors  $C_p$  and  $C_s$  are already defined in (1) and (2). As can be seen, none of these voltages depends only on  $n_1$  or  $n_2$ , but on  $n_t$ . Hence, the switching losses (and the voltage ratings) in the semiconductors are tied once  $D_{max}$  is chosen.

Regarding the current stress on the components, it is enough to calculate the currents through the three windings of the transformer as a function of time. With them, the currents through any component of the ZAHB converter can be calculated. In section VI, the equations of the three currents are derived. In that section, it is also shown that the ripple in the output inductor current and in the magnetizing inductance current can be disregarded in comparison to the ripple in the leakage inductance. As a consequence, the equations of the three currents can be simplified.

The current through the leakage inductance is:

$$i_{Lk}(t) \approx \begin{cases} I_{out} n_t & \text{when } 0 < t < D T \\ I_{out} n_t \left( 1 - \frac{2}{\left(1 - D\right)^2 T} \left( t - D T \right) \right) & \text{when } D T < t < T \end{cases}$$

(19)

This current can be used for calculating the current through MOSFETs  $M_1$  and  $M_2$  and through capacitor  $C_p$ .

The current through the first secondary winding, which is also the current through  $C_s$ , satisfies:

$$i_{Tr1}(t) \approx \begin{cases} I_{out} & \text{when } 0 < t < DT \\ I_{out} \left( 1 - \frac{2}{(1-D)^2 T} (t-DT) \right) & \text{when } DT < t < T \end{cases}$$

(20)

while the current though the second secondary winding (and diode  $D_s$ ) satisfies (see Fig. 1 for the current positive sign):

$$0 \quad when \quad 0 < t < D T$$

$$i_{Tr2}(t) \approx \left\{ -2 \ I_{out} \ \frac{t - D \ T}{(1 - D)^2 \ T} \quad when \quad D \ T < t < T \right\}$$

(21)

As can be seen, none of the currents through the semiconductors depend on  $n_1$  or  $n_2$  (only on  $n_t$ ) if the ripple in the magnetizing inductance and the output inductor is disregarded. In the case these ripples cannot be disregarded, section VI also includes the complete equations, which can be used instead of the simplified ones without affecting the proposed design methodology. For the sake of simplicity, the explanation provided here will be based on the simplified equations.

The currents through the capacitors are also independent from  $n_1$  and  $n_2$ ; nonetheless, losses in capacitors are generally disregarded.

The values of  $n_1$  and  $n_2$  cannot be then used for minimizing the losses in the semiconductors and optimize the design of the converter as they are all defined once  $n_t$  is chosen. The optimized design of the ZAHB converter will be then based on the losses in the magnetics (transformer and inductor) because, as will be seen, they are dependent on  $n_1$ and  $n_2$ .

The core losses in the output inductor,  $P_{Lf\_core},$  can be expressed as:

$$P_{Lf\_core} = Vol_{Lf} \ c_{Lf} \left( \frac{n_1 \ V_O \ (1-D)}{2 \ n_t \ N_{Lf} \ Ae_{Lf} \ f} \right)^{y_{Lf}} \ f^{x_{Lf}}$$

(22)

where  $N_{Lf}$  is the number of turns of the inductor,  $Vol_{Lf}$  is the volume of the magnetic core of the inductor,  $Ae_{Lf}$  is the effective area of the magnetic core, f is the switching frequency and  $x_{Lf}$ ,  $y_{Lf}$  and  $c_{Lf}$  are parameters defined by the chosen magnetic material. As can be seen, the core losses in the output inductor depend on  $n_1^{yLf}$ .

The conduction losses,  $P_{Lf\_copper}$ , are:

$$P_{Lf\_copper} = I_{Lf\_rms}^2 \rho \frac{lm_{Lf} N_{Lf}^2}{Aw_{Lf}}, \qquad (23)$$

where  $lm_{Lf}$  is the mean length per turn and  $Aw_{Lf}$  is the window area, both of the magnetic core, and  $I_{Lf_rms}$  is the rms value of the current through the inductor.

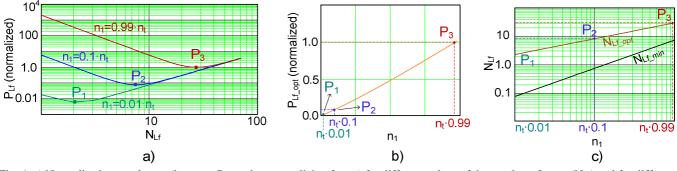

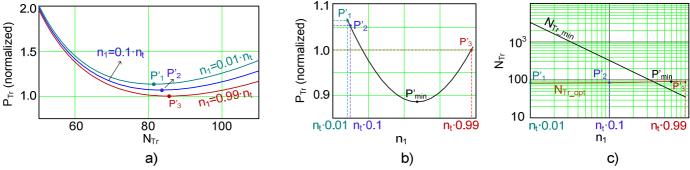

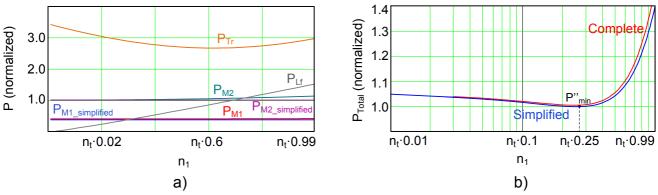

In Fig. 4a, the normalized overall losses in the inductor,  $P_{Lf}$ , are represented for different values of  $n_1$  and  $N_{Lf}$  (and for a given magnetic material). The normalization factor are the minimum losses for  $n_1=0.99 \cdot n_t$ . The part with negative slope of each curve represents the designs (according to the number of turns) in which core losses are dominant, while the positive-slope parts are copper-loss

dominant. Obviously, the optimum point for each curve (i.e., each  $n_1$  value) is the one with flat slope. As can be seen, as  $n_1$  increases, the losses in the optimum point,  $P_{Lf_opt}$ , increases in a linear way (as shown in Fig. 4b). Therefore, from the inductor design point of view, the lower  $n_1$ , the better. Moreover, as  $n_1$  is increased, the optimum number of turns,  $N_{Lf_opt}$ , at which the total losses in the inductor are minimized, also increases. This can be seen in Fig. 4a and also in Fig. 4c.

There is an additional issue to be considered in the design of the output inductor. The number of turns,  $N_{Lf}$ , should be higher than a given value in order to avoid the saturation of the core. This value,  $N_{Lf}$  min, can be defined as:

$$N_{Lf_{\rm min}} = \frac{I_{o} V_{o} (1 - D_{\rm min}) n_{1}}{2 n_{t} f B_{Lf_{\rm sat}} A e_{Lf}}$$

(24)

where  $I_o$  is the nominal output current and  $B_{Lf sat}$  is the maximum density flux of the chosen magnetic material. If  $N_{\text{Lf}\_\text{min}}$  is higher than  $N_{\text{Lf}\_\text{opt}}\text{,}$  there are only two possible options to reach a valid design. The first one is designing the inductor with a number of turns equal to  $N_{Lf_{min}}$ , which represents a design not optimized from the losses point of view (it would be a copper-loss-dominant design). The second one is increasing the size of the chosen magnetic core with the purpose of reducing  $N_{Lf_{min}}$  (as can be seen, (24) is proportional to  $Ae_{Lf}^{-1}$ ). Nonetheless, with this second option the size of the converter is compromised. Obviously, the design of the ZAHB converter should aim at choosing a value of  $n_1$  which assures that  $N_{Lf\_min}$  is lower than  $N_{Lf\_opt}$ . As can be seen in Fig. 4c,  $N_{Lf\_min}$  increases with higher values of  $n_{\rm l}.$  Moreover, the slope of  $N_{Lf\_min}$  is higher than the slope of N<sub>Lf opt</sub>. From the saturation point of view, as for the losses, the lower  $n_1$ , the better, because the resulting inductor will be farther from saturation. This may lead to a reduction in the size of the magnetic core because there is room to increase the value of N<sub>Lf min</sub> without reaching saturation.

Regarding the transformer, a similar analysis can be done. The core losses,  $P_{Tr\_core}$ , can be calculated as follows:

$$P_{Tr\_core} = Vol_{Tr} c_{Tr} \left( \frac{V_o (1-D)}{2 n_t N_{Tr} A e_{Tr} f} \right)^{y_{Tr}} f^{x_{Tr}}$$

(25)

where  $N_{Tr}$  is the number of turns of the primary side winding,  $Vol_{Tr}$  is the volume and  $Ae_{Tr}$  the effective area, both of the magnetic core chosen for the transformer, and  $c_{Tr}$ ,  $y_{Tr}$  and  $x_{Tr}$  are parameters defined by the material of the

Fig. 4. a) Normalized power losses (losses at  $P_3$  used as normalizing factor) for different values of the number of turns ( $N_{Lf}$ ) and for different values of the turns ratio of the transformer ( $n_1$ ); b) Normalized losses as a function of  $n_1$  for the optimum value of  $N_{Lf}$  in each case; c) Optimum number and minimum number of turns ( $N_{Lf}$  opt and  $N_{Lf}$  min) as a function of  $n_1$ .

magnetic core. As can be seen, the transformer core losses are independent from  $n_1$  or  $n_2$  (not like the core losses in the inductor).

The copper losses in the transformer,  $P_{Tr\_copper}$ , can be expressed as:

$$P_{Tr_{-copper}} = I_{lk_{-ms}}^{2} \rho N_{Tr}^{2} \cdot \frac{lm_{Tr}}{Aw_{Tr}} fw_{Tr_{-pri}} + I_{Tr_{1}-ms}^{2} \rho N_{Tr}^{2} n_{1}^{2} \frac{lm_{Tr}}{Aw_{Tr}} fw_{Tr_{1}} + I_{Tr_{2}-ms}^{2} \rho N_{Tr}^{2} n_{2}^{2} \frac{lm_{Tr}}{Aw_{Tr}} fw_{Tr_{2}} ,$$

(26)

where  $I_{lk\_rms}$  is the rms value in the primary winding,  $I_{Tr1\_rms}$ and  $I_{Tr2\_rms}$  are the rms value of the currents through the two secondary windings,  $Aw_{Tr}$  is the window area of the core of the transformer and  $fw_{Tr\_pri}$ ,  $fw_{Tr1}$  and  $fw_{Tr2}$  represent the percentage of the window area used by each winding. The way these factors are defined may vary, but two possible conditions are levelling the circular mils per amp (CMA) factor or levelling the losses in the three windings. The last option may be expressed as follows:

$$f_{W_{Tr_pri}} = \frac{I_{Lk_rms}^2}{I_{Lk_rms}^2 + n_1^2 I_{Tr_1_rms}^2 + n_2^2 I_{Tr_2_rms}^2},$$

(27)

$$fw_{Tr1} = \frac{n_1^2 I_{Tr1\_rms}^2}{I_{Lk\_rms}^2 + n_1^2 I_{Tr1\_rms}^2 + n_2^2 I_{Tr2\_rms}^2}$$

(28)

$$f_{W_{Tr2}} = \frac{n_2^2 I_{Tr2\_rms}^2}{I_{Lk\_rms}^2 + n_1^2 I_{Tr1\_rms}^2 + n_2^2 I_{Tr2\_rms}^2}$$

(29)

Although the currents are independent from  $n_1$  or  $n_2$ , as can be derived from equations (19)-(21), the copper losses in the transformer depend on  $n_1$  and  $n_2$  due to the way the window area is shared by the three windings (see (26)-(29)). Fig. 5a shows the total losses in the transformer for three different values of  $n_1$  (the same as those used in Fig. 4), for a given magnetic material, and for different values of  $N_{Tr}$ , the number of turns of the primary winding. The normalization factor is the power dissipated by the transformer at P'<sub>3</sub>, which is the minimum for  $n_1=0.99 \cdot n_t$ , the same value of  $n_1$ used in the normalization of the inductor losses. As can be seen in Fig. 5b, the variation of the losses as a function of  $n_1$ is not linear, as happens in the inductor. It presents a minimum point in the vicinity of  $n_1=0.6 \cdot n_t$ . The optimum number of turns N<sub>tr\_opt</sub> is not linear either, and presents a maximum also in the vicinity of  $n_1 = 0.6 \cdot n_t$ .

Saturation in the transformer core has to be avoided.

Therefore:

$$N_{Tr_{min}} = \frac{V_o \ D_{min} \ (1 - D_{min})}{2 \ n_1 \ n_t \ f \ B_{Tr_{sat}} \ Ae_{Tr}}$$

(30)

where  $N_{Tr\_min}$  is the minimum number of turns to avoid saturation in the transformer core and  $B_{Tr\_sat}$  is the maximum magnetic flux, which depends on the material of the core. As can be seen, the minimum number of turns in the transformer decreases linearly with  $n_1$  (represented in Fig. 5c), completely different from the behaviour of  $N_{Lf\_min}$ .

From the transformer point of view, the criterion for choosing  $n_1$  is completely different from the one defined by the inductor. As can be seen in Fig. 5c, for low values of  $n_1$ , the magnetic core would be saturated. Therefore,  $n_1$  should be higher than the value defined by the intersection between  $N_{Lf\_min}$  and  $N_{Lf\_opt}$  in Fig. 5c and as close as possible to the point P'<sub>min</sub> in Fig. 5b.

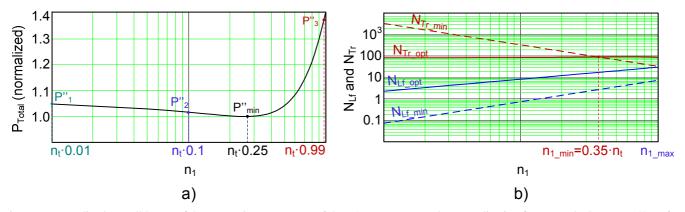

Now that the effect of  $n_1$  (and  $n_2$ ) in the losses of all the components are clearly identified, it is possible to propose the optimized design of the ZAHB converter based on the minimization of the overall losses in the magnetic components under nominal conditions. Nonetheless, each magnetic component fixes different criteria for choosing the best value for  $n_1$ . The optimized design starts then with the addition of the losses in the transformer and in the inductor. Fig. 6a shows a design example related to the losses presented in Fig. 4 and Fig. 5. As can be seen, the minimum losses are now located at a value of  $n_1$  different from both, the one that optimizes the inductor and the one that optimizes the transformer. The other issue to take into consideration is assuring that none of the magnetic components reaches saturation. For the sake of clarity, Fig. 4c and Fig. 5c are represented in Fig. 6b together. As can be seen, the transformer needs a value higher than  $n_{1 \text{ min}}$  (around  $0.35 \cdot n_{t}$ in this particular case) in order to assure that it does not reach saturation for the optimum number of turns, N<sub>Tr opt</sub>. In this particular case, saturation in the inductor for the optimum number of turns ( $N_{Lf_{min}}=N_{Lf_{opt}}$ ), occurs for a value of  $n_1$ higher than  $n_t$  (not shown). Therefore,  $n_{1\_max}$  is equal to  $n_t$ . For other designs, as the slope of  $N_{Lf min}$  is higher than  $N_{lf opt}$ , their intersection may occur at values lower than nt. The final value of  $n_1$  should be then in between  $n_1_{min}$  and  $n_1_{max}$  (Fig. 6b) and should assure the minimum overall losses (Fig. 6a). In other words,  $n_1$  should be as close as possible to the value that defines P"min but without exceeding the range defined

Fig. 5. a) Normalized power losses (losses at P'<sub>3</sub> used as normalizing factor) for different values of the number of turns of the primary winding  $(N_{Tr})$  and for different values of the turns ratio of the transformer  $(n_1)$ ; b) Normalized losses as a function of  $n_1$  for the optimum value of  $N_{Tr}$  in each case; c) Optimum number and minimum number of turns  $(N_{Tr_opt} \text{ and } N_{Tr_min})$  as a function of  $n_1$ .

Fig. 6. a) Normalized overall losses of the magnetic components of the ZAHB converter (the normalization factor are the losses at  $P''_{min}$ ) for different values of  $n_1$ . All the point are calculated according to the optimum number of turns for the inductor and the transformer; b) comparison of the optimum and minimum number of turns for both magnetic components according to  $n_1$ .

by  $n_{1\_min}$  and  $n_{1\_max}$ . According to this, in the proposed example the final value of  $n_1$  should be equal to  $n_{1\_min}=0.35 \cdot n_t$ .

Once the value of  $n_1$  is chosen, it is possible to obtain the optimum number of turns for each magnetic component  $(N_{Tr\_opt} \mbox{ and } N_{Lf\_opt} \mbox{ in Fig. 6b}).$  Then, the typical design of magnetic components can be applied (type of wire, number of strands to avoid skin effect, turns arrangement, simulation and estimation of leakage inductance and final temperature, etc.). Once this is done, it is possible to decide if the type, size and material chosen at the beginning are the most suitable ones or if they have to be increased, decreased or changed, according to different factors such as Circular Mils per Amp (CMA), the final temperature according to 3D simulation, etc. If the size or material of any of the two magnetic components is changed, a new whole iteration has to be performed. The only difference with a standard iterative design is that the iteration is not applied to the single magnetic component, but it starts with the calculation of the overall losses as a function of  $n_1$  and the valid range of this parameter according to the magnetic saturation in the inductor and the transformer.

#### **IV. EXPERIMENTAL RESULTS**

The experimental results have been obtained with the prototype shown in Fig. 7. The main parameters and components are shown in Table 1. As can be seen, the control stage can be implemented using a standard analog controller due to the simplicity of the control loops. Nonetheless, it can be easily implemented with any digital system such as an FPGA or a DSP if required. The maximum

Fig. 7. Photograph of the prototype.

duty cycle attainable by the control circuit is 85%. Apart from that, dead times in order to achieve ZVS under any circumstances and leakage inductance influence should be considered. Therefore,  $D_{max}$  is chosen equal to 70%. The value of  $n_t$  is then around 0.20. According to Fig. 6a and Fig. 6b, the value of  $n_1$  should be 0.070 while the value of  $n_2$ should be then 0.130. With these two values it is possible to determine the optimum number of turns for both, the inductor (17 turns), and the transformer (81 turns on the primary winding).

| Parameter/Common ant                         |                                                                         |

|----------------------------------------------|-------------------------------------------------------------------------|

| Parameter/Component                          | Value/Part number                                                       |

| Nominal input voltage                        | 325 V <sub>dc</sub>                                                     |

| Input-voltage ripple (pk-pk)                 | 65 V <sub>pp</sub> (20% of nominal input voltage)                       |

|                                              | 100 Hz                                                                  |

| Output voltage                               | 37 V                                                                    |

| Nominal power                                | 50 W                                                                    |

| Current range                                | Full dimming                                                            |

| Switching frequency                          | 120 kHz                                                                 |

| Control IC                                   | UC3824N                                                                 |

| MOSFETs (M <sub>1</sub> and M <sub>2</sub> ) | FQD2N60C (600 V, 1.9 A, N channel)                                      |

| Diode (D <sub>s</sub> )                      | HTG5150 (150 V, 5 A, Schottky)                                          |

| Primary capacitor (C <sub>p</sub> )          | 0.68 µF, MKT (2 in parallel)                                            |

| Secondary capacitor (C <sub>s</sub> )        | 0.82 µF, MLCC (3 in parallel)                                           |

| Transformer                                  | ETD29                                                                   |

|                                              | N <sub>Tr</sub> =81 turns, n <sub>1</sub> =0.070, n <sub>2</sub> =0.130 |

|                                              | $L_m = 15 \text{ mH}, L_{lk} = 31 \mu \text{H}$                         |

| Inductor (L <sub>f</sub> )                   | E20                                                                     |

|                                              | $N_{Lf}$ =17 turns, $L_{f}$ = 130 µH                                    |

| Magnetic material                            | 3F3                                                                     |

|                                              | $(c=0.062 \times 10^{-10}, x=1.189, y=2.55)$                            |

| Filter capacitor (C <sub>f</sub> )           | 0.82 µF, MLCC (3 in parallel)                                           |

Table 1. Main parameters and components of the prototype

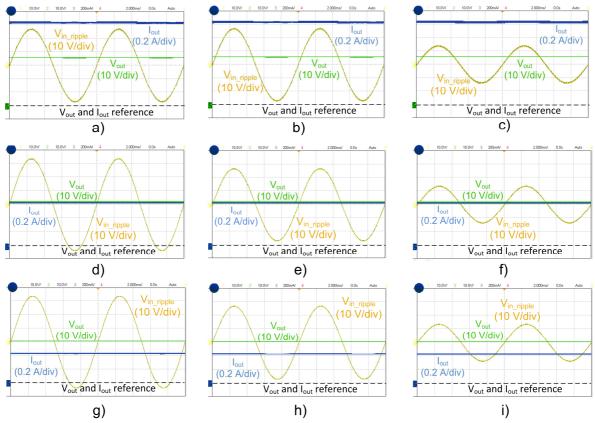

In Fig. 8, the output voltage and output current are presented for different ripples in the input voltage (columns in Fig. 8) and different output voltages/currents (rows in Fig. 8). As can be seen, neither the output voltage nor the output current present any relevant ac component due to the fact that the feedforward loop, in this topology, leads to a perfect cancellation of the ripple, no matter the input voltage ripple or output voltage level. The feedback loop can be slow then, overcoming the typical stability problem that the AHB converter family presents due to the resonance between the magnetizing inductance and the input capacitor.

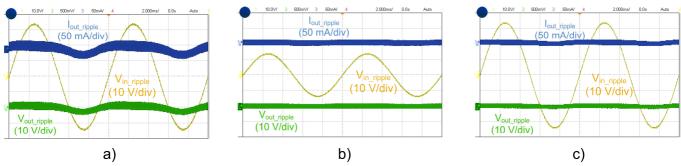

In Fig. 9, a detail of the output voltage and the output current ripple (only ac component) is shown under different

Fig. 8. Cancellation of the ripple for different output voltages (green) and currents (blue), and different input-voltage ripples (yellow).

operating conditions. As can be seen, they are cancelled in all situations. In Fig. 9a, the output voltage and current are fixed at a level slightly higher than the nominal one (then, out of the design conditions). When the input voltage decreases due to the ripple, the duty cycle tends to counter this by increasing its value. Nonetheless, it reaches its maximum value before the input-voltage ripple has reached its minimum one. As a consequence, there is a small variation in the output voltage and current when the input voltage ripple is negative. As already mentioned, this is because the converter is operating outside the design conditions and, even in that situation, the cancellation is almost perfect, with a peak-to-peak current ripple lower than 2% (disregarding the switching-frequency ripple). This highlights the relevance of wisely choosing  $n_t$  at the beginning of the design in order to take into account all the

dead times, limits imposed by the controller, leakage inductance effect, etc. In Fig. 9b, the same output voltage and current (out of nominal range) are fixed while the input voltage ripple is reduced. As can be seen, in this situation the duty cycle has enough margins to keep the output constant. Finally, in Fig. 9c, a detail of the output ripple under nominal conditions (37 V) and highest input voltage ripple (70 V<sub>pk-pk</sub>) is shown. As can be seen, the ripple is cancelled.

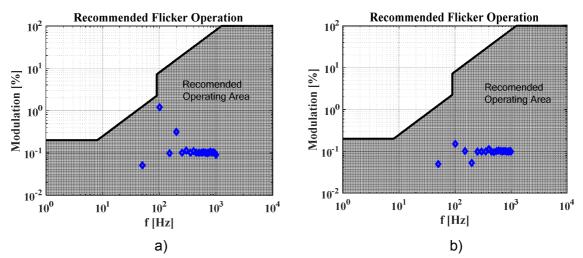

According to the IEEE Recommended Practices regarding flicker [43], the Modulation of the light should be kept within the Recommended Flicker Operation Area (shaded area). This Modulation has to be calculated for each harmonic of the ac component (i.e., ripple) of the light as follows [44]:

Fig. 9. Input voltage ripple (ac value, yellow), output voltage ripple (ac value, green), and output current ripple (ac value, blue) for: a) maximum input voltage ripple and 39-V output voltage; b) minimum input voltage ripple and 39-V output voltage; c) maximum input voltage ripple and 70 voltage; c) maximum input vol

Fig. 10. Flicker analysis according to [43] for a) Fig. 9a [outside nominal conditions] and b) Fig. 9c [in nominal conditions].

$$Modulation(\%) = \frac{L_{\max} - L_{\min}}{L_{\min} + L_{\max}} 100$$

(31)

where  $L_{min}$  and  $L_{max}$  are the minimum and maximum luminance of the LEDs due to each harmonic of the ac component. The results for the emitted light in Fig. 9a and Fig. 9c are presented in Fig. 10. As can be seen, even when the ripple is higher than expected due to the operation out of nominal conditions (Fig. 9a and Fig. 10a), all the harmonics fall within the shaded area. Even those corresponding to the lowest frequencies, which are the most critical ones regarding flickering. As can be seen in Fig. 10b, in nominal conditions (the ones to be analysed according to [43]) the results are even better, with all the harmonic components around 0.1%.

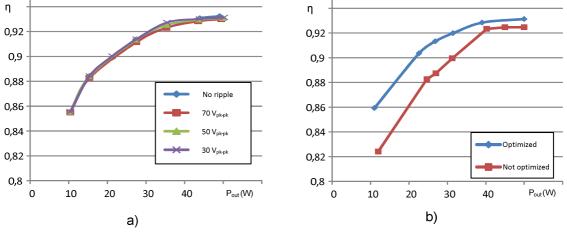

In Fig. 11a, the efficiency for different ripples in the input voltage is shown. As can be seen, the efficiency of the ZAHB converter is in the range of other converters of the same family, mainly due to the fact that primary switches reach ZVS. It should be said that efficiency can be improved in low-voltage applications implemented with this topology (or any other AHB converter) thanks to the possibility of easily implementing self-driven synchronous rectification. Considering a standard first stage, such as the PFC Boost

converter operating in Critical Conduction Mode (Boundary Conduction Mode) [39], [40], the overall peak efficiency of the two-stage LED driver would be in the range 91-92% or even higher, depending on the output voltage and current specifications. Moreover, the effectiveness of the feedforward loop and the validity of the design methodology proposed in this paper for the ZAHB converter will not be affected by the topology of the first stage [41], [42].

To see how the proposed design guideline improves the efficiency, a different design has been made. In this second design, the semiconductors and the capacitors are exactly the same as in the first prototype, as well as the size and the magnetic material of both, the inductor and the transformer. Nonetheless, the turns ratios of the transformer are not the ones resulting from the optimized design of the topology (0.070 and 0.130, respectively), which were used in the first prototype. These new turns ratios are 0.16 and 0.04. Apart from that difference, the design of the two magnetic components is carried out trying to minimize their overall losses, as for the first prototype (i.e., selecting the optimum number of turns). The results are shown in Fig. 11b. As can be seen, the proposed design presents better efficiency. It should be said that this proposed design only minimizes the

Fig. 11. a) Efficiency for different input voltage ripples and different values of the output power (i.e., dimming); b) Efficiency for an optimized ZAHB converter and for a not-optimized one.

losses in the magnetic components. Therefore, the degree of impact in the overall efficiency of the converter depends on the percentage that the losses in the magnetic components represent out of the total losses.

### V. CONCLUSIONS

The ZAHB converter still presents the typical resonance between the input capacitor and the magnetizing inductance. Therefore, the cancelation of the low-frequency ripple in its output voltage cannot be achieved by means of its feedback loop. Nonetheless, the static gain in this converter presents a linear relation between the output voltage and the duty cycle, not as other topologies of the same family (i.e., standard AHB, AHB with Two Transformers, etc.). This allows a simple feedforward loop to perfectly cancel the low-frequency ripple without stability problems. Regarding the design of the topology, the main functional characteristics (static gain, voltage withstood by semiconductors, etc.) are independent from the two turns ratios of the transformer or dependent on n<sub>t</sub>. In other words, they do not depend only on  $n_1$  (or only on  $n_2$ ). On the other hand, the losses in the magnetic components do depend on n<sub>1</sub>. Consequently, it is possible to avoid the typical design in which  $n_1$  is made equal to  $n_2$  just as a way of simplifying the resulting equations or the construction of the transformer. In the proposed design, the value of  $n_t$  is defined according to the main functional characteristics (nominal input voltage, low-frequency ripple, maximum attainable duty cycle and nominal output voltage). Then, the value of  $n_1$  (and  $n_2$ ) is chosen so that the overall losses in the magnetic components are minimized.

#### VI. ANNEX

#### CALCULATION OF THE CURRENTS

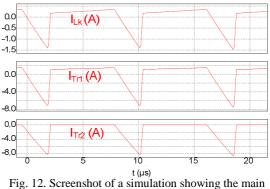

In this section, the equations of the currents through the three windings of the transformer will be derived. In Fig. 12, the current through the leakage inductance ( $I_{Lk}$ ), and through the two secondary windings ( $I_{Tr1}$  and  $I_{Tr2}$ ) are shown (according to Fig. 1 current signs).

The current through the leakage inductance during  $D \cdot T$  is equal to the current through the output inductor reflected to the primary side plus the current through the magnetizing inductance:

$$i_{Lk}(t) = \left[ \left( I_{out} + \frac{V_{in} n_1 (1-D)}{L_f} \left( t - \frac{D T}{2} \right) \right) n_1 \right] + \left[ I_{out} n_2 + \frac{V_{in}}{L_m} \left( t - \frac{D T}{2} \right) \right]$$

(32)

when 0 < t < D T

where  $L_f$  is the value of the output inductor and T is the switching period.

The leakage current during  $(1-D)\cdot T$  should be calculated according to the voltages in  $C_p$  and  $C_s$ . This calculation needs also the value of the leakage inductance.

Fig. 12. Screenshot of a simulation showing the main currents of the topology.

This is not advisable due to two reasons. First, it needs the transformer to be completely designed, including the arrangement and geometry of all the layers of the three windings. That is not possible because the proposed optimized design procedure is based on wisely choosing  $n_1$  and  $n_2$ , so it is not possible to define the physical design of the transformer previously. Second, the value of the leakage inductance is not so well predicted by numerical or analytical methods (unlike the magnetizing inductance of the transformer). Basing the calculation of the current on the estimated leakage inductance is not as accurate as it may be desirable.

The capacitor  $C_p$  is in series with the leakage inductance, therefore, the average value of the leakage current, in steady state, has to be zero. Moreover, as shown in Fig. 12, it can be considered that the current presents a linear behaviour during (1-D)·T. Therefore, it can be expressed as:

$$i_{Lk}(t) = I_{out} n_t \left( 1 - \frac{2(t - DT)}{(1 - D)^2 T} \right) + +ripple \left( 1 - \frac{2(1 - D)(t - DT)}{(1 - D)^2 T} \right)$$

when  $DT < t < T$  (33)

where

$$ripple = \left(\frac{V_{in} n_1^2 (1-D)}{L_f} + \frac{V_{in}}{L_m}\right) \frac{D T}{2}$$

(34)

This last factor represents the effect on the starting value of the leakage current during  $(1-D)\cdot T$  due to the magnetizing and output inductor current ripples during  $D\cdot T$ .

It should be mentioned that the current ripple in the output inductor and in the magnetizing inductance are considerably lower than the ripple in the leakage inductance during  $(1-D)\cdot T$ . Therefore, during  $D\cdot T$ , the current in the leakage inductance can be considered constant (see Fig. 12), leading to:

$$\dot{I}_{Lk}(t) \approx \left(I_{out} \ n_1\right) + \left(I_{out} \ n_2\right) = I_{out} \ n_t \quad \text{when} \quad 0 < t < D \ T \tag{35}$$

For the same reason, the factor *ripple* can be neglected in (33), leading to:

$$i_{Lk}(t) \approx I_{out} n_t \left( 1 - \frac{2(t - DT)}{(1 - D)^2 T} \right) \quad when \quad DT < t < T$$

(36)

As can be seen, the current through the leakage inductance is not actually independent from  $n_1$  (see (32), (33) and (34)), but due to the fact that the ripple during D·T can be neglected, the current can be considered only dependent on  $n_t$  (see Fig. 12a).

The current through the first secondary winding can be obtained in a similar way. The average value of the current of this first winding has to be zero due to capacitor  $C_s$ . During D·T, the current through the first secondary winding is equal to the current through the output inductor:

$$i_{TR1}(t) = I_{out} + \frac{V_{in} n_1 (1-D)}{L_f} \left( t - \frac{D T}{2} \right) \quad when \quad 0 < t < D T \qquad (37)$$

Nonetheless, the ripple during  $D \cdot T$  can be neglected in comparison to the ripple introduced in the current during (1-D)·T. Therefore:

$$i_{TR1}(t) \approx I_{out}$$

when  $0 < t < D T$  (38)

During  $(1-D)\cdot T$ , the current will present a linear behaviour and, consequently:

$$i_{TR1}(t) = \left[ I_{out} + \frac{V_{in} n_1 (1-D)}{L_f} \left( \frac{D T}{2} \right) \right] \left[ 1 - \frac{2 (t-D T)}{(1-D)^2 T} \right] , \qquad (39)$$

when  $D T < t < T$

which neglecting the ripple in the output inductor can be rewritten as:

$$i_{TR1}(t) \approx I_{out} \left[ 1 - \frac{2(t - DT)}{(1 - D)^2 T} \right] \quad when \quad DT < t < T$$

(40)

Finally, the current through the second secondary winding is straightforward applying Kirchhoff Rules to the secondary side of the transformer:

$$i_{TR2}(t) = 0 \quad when \quad 0 < t < D T \tag{41}$$

$$i_{TR2}(t) = -I_{out} \frac{2(t-DT)}{(1-D)^2T} + \frac{V_{in}D}{2L_f}$$

when  $DT < t < T$ . (42)

$$\cdot \left[ (n_1-1)(1-D)T + (t-DT)\left(1-\frac{2n_1}{1-D}\right) \right]$$

Disregarding the ripple:

$$i_{TR2}(t) = 0$$

when  $0 < t < DT$  , (43)

$$i_{TR2}(t) \approx -I_{out} \ \frac{2(t-DT)}{(1-D)^2 T} \quad when \quad DT < t < T$$

$$(44)$$

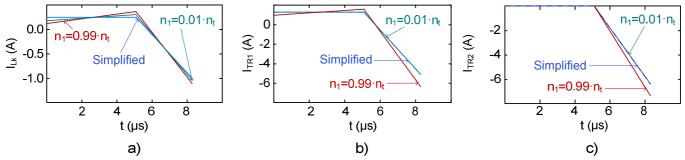

The optimized design proposed in the paper is based on the simplified equation obtained in the previous section. In most of the design, the results are perfectly valid and equal to the results that would have been obtained with the non-simplified equations. In Fig. 13, the currents obtained with the complete equations ((32), (33), (38), (39), (41) and (42)) and with the simplified ones ((35), (36), (38), (40), (43) and (44)) are represented for the ZAHB converter proposed in section IV under nominal conditions. As can be seen, the differences are small and they do not significantly affect the results obtained.

It should be taken into account that losses in the semiconductors are not considered in the proposed optimization because they do not depend on  $n_1$  or  $n_2$  according to the simplified equations. Nonetheless, if the complete equations are considered, the losses in those components may change according to  $n_1$ . Nonetheless, these changes can be normally neglected. In Fig. 14, the losses in the magnetic components and the losses in the switches are represented according to the full equations. As can be seen, the losses in the semiconductors are of the same order of magnitude (Fig. 14a), but they are nearly constant so, in general, they can be omitted in the search of the optimum value of  $n_1$  (Fig. 14b).

# CALCULATION OF THE MAGNETIC-COMPONENT LOSSES

The losses in the magnetic components consist of losses in the core and losses in the copper (i.e., magnetic losses and conduction losses). The equations of the copper losses, both in the inductor and in the transformer, are straightforward. On the other hand, the equations of the core losses should be derived.

The losses in the core can be expressed as:

$$P_{core} = Vol_{Lf} \ c \ \left(\frac{B}{2}\right)^{y} \ f^{x}$$

(45)

In the inductor, the magnetic field can be expressed as:

$$B_{Lf} = \frac{L_f I_{pp}}{N_{Lf} A e_{Lf}}$$

(46)

The value of  $L_f$  is defined considering the acceptable ripple in the current inductor for a given operating condition. For the sake of clarity, it has been considered that the inductor ripple is defined in nominal conditions:

Fig. 13. Current for two different values of n<sub>1</sub> (extreme values) according to the complete equations and also according to the simplified ones. a) Leakage current; b) current through the first secondary winding; c) current through the second secondary winding.

Fig. 14. a) Losses (normalized to  $P_{M2\_simplified}$ ) in all the magnetic components and in the semiconductors as a function of  $n_1$ ; b) Overall losses as a function of  $n_1$  according to the complete equations and to the simplified ones.

$$L_{f} = \frac{V_{o} n_{1} (1-D)}{f n_{i} I_{pp}}$$

(47)

Hence,

$$P_{Lf\_core} = Vol_{Lf} \ c_{Lf} \left( \frac{n_1 \ V_O \ (1-D)}{2 \ n_t \ N_{Lf} \ Ae_{Lf} \ f} \right)^{y_{Lf}} \ f^{x_{Lf}}$$

(48)

In the transformer, the core losses can be easily obtained considering that the value of the magnetizing current, which defines the magnetic field, satisfies:

$$I_{mag_{pp}} = \frac{V_{in} - V_{Cp}}{L_{mag}} D T = \frac{V_{in} (1-D)}{L_{mag}} D T = \frac{V_o (1-D)}{n_r L_{mag}} T$$

(49)

The magnetic field is defined as:

$$B_{Tr} = \frac{L_{mag} I_{mag_pp}}{N_{Tr} A e_{Tr}}$$

(50)

Therefore,

$$P_{Tr\_core} = Vol_{Tr} \ c_{Tr} \left( \frac{V_o \ (1-D)}{2vn_t v N_{Tr} \ Ae_{Tr} v f} \right)^{y_{Tr}} f^{x_{Tr}}$$

(51)

The minimum number of turns can be easily obtained using (46) and (47) in the case of the inductor and (49) and (50) in the case of the transformer:

$$B_{Lf_{max}} = \frac{V_o n_1 (1-D)}{N_{Lf_{min}} n_t A e_{Lf} f}$$

(52)

$$B_{Tr_{max}} = \frac{V_o (1-D)}{N_{Tr_{min}} n_t A e_{Tr} v f}$$

(53)

#### VII. REFERENCES

- B. Lehman and A. Shteynberg, "Professional Education Seminars: LED lighting: trends, standards, optics and power electronics," in Applied Power Electronics Conference and Exposition (APEC), Fort Worth, 2011.

- [2] L. Gu; X. Ruan; M. Xu; K. Yao, "Means of Eliminating Electrolytic Capacitor in AC/DC Power Supplies for LED Lightings," Power Electronics, IEEE Transactions on , vol.24, no.5, pp.1399,1408, May 2009.

- [3] K. H. Loo, Y. M. Lai, S. C. Tan, C. K. Tse, "On the Color Stability of Phosphor-Converted White LEDs Under DC, PWM, and Bilevel Drive," Power Electronics, IEEE Transactions on, vol.27, no.2, pp.974-984, Feb. 2012.

- [4] S. Tan, "General η-Level Driving Approach for Improving Electricalto-Optical Energy-Conversion Efficiency of Fast-Response Saturable

Lighting Devices," Industrial Electronics, IEEE Transactions on , vol.57, no.4, pp.1342,1353, April 2010.

- [5] H. Haas, L. Yin, Y. Wang and C. Chen, "What is LiFi?," in Journal of Lightwave Technology, vol. 34, no. 6, pp. 1533-1544, March15, 15 2016.

- [6] H. Haas, "LiFi: Conceptions, misconceptions and opportunities," 2016 IEEE Photonics Conference (IPC), Waikoloa, HI, USA, 2016, pp. 680-681.

- [7] K. Modepalli; L. Parsa, "Single Stage LED Driver with Power Factor Correction for Illumination and Visible Light Communication," in IEEE Industry Applications Magazine, vol.PP, no.99, pp.XX5-XX5.

- [8] Y. Wang, Y. Guan, K. Ren, W. Wang, D. Xu, "A Single-stage LED Driver Based on BCM Boost Circuit and LLC Converter for Street Lighting System", IEEE Trans. on Industrial Electronics, vol. 62, no. 9, pp. 5446-5457, 2015.

- [9] Y. Guo, S. Li, A. T. L. Lee, S.-C. Tan, C. K. Lee, S. Y. R. Hui, "Single-Stage AC/DC Single-Inductor Multiple-Output LED Driver", vol. 31, no. 8, pp. 5837-5850, 2016.

- [10] J. Kim; J. Lee; G. Moon, "Isolated Switch-Mode Current Regulator With Integrated Two Boost LED Drivers," Industrial Electronics, IEEE Transactions on, vol.61, no.9, pp.4649,4653, Sept. 2014.

- [11] Y. Li; Chen, Ch. Chen, "A Novel Single-Stage High-Power-Factor ACto-DC LED Driving Circuit With Leakage Inductance Energy Recycling," Industrial Electronics, IEEE Transactions on , vol.59, no.2, pp.793,802, Feb. 2012.

- [12] Y. Li; Ch. Chen, "A Novel Primary-Side Regulation Scheme for Single-Stage High-Power-Factor AC–DC LED Driving Circuit," Industrial Electronics, IEEE Transactions on , vol.60, no.11, pp.4978,4986, Nov. 2013.

- [13] J A. Pawellek and T. Duerbaum, "LED-ballasts in lighting applications — A comparison of cost effective one stage topologies," 2016 18th European Conference on Power Electronics and Applications (EPE'16 ECCE Europe), Karlsruhe, 2016, pp. 1-10.

- [14] D X. Liu; Q. Yang; Q. Zhou; J. Xu; G. Zhou, "Single-Stage Single-Switch Four-Output Resonant LED Driver with High Power Factor and Passive Current Balancing," in IEEE Transactions on Power Electronics , vol.PP, no.99, pp.1-1.

- [15] D. G. Lamar, J. Sebastian, M. Arias and M. M. Hernando, "A low-cost AC-DC High-Brightness LED driver with Power Factor Correction based on standard Peak-Current Mode Integrated Controllers," 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, 2010, pp. 463-470.

- [16]Q. Hu; R. Zane, "Off-line LED driver with bidirectional second stage for reducing energy storage," Energy Conversion Congress and Exposition (ECCE), 2011 IEEE, vol., no., pp.2302,2309, 17-22 Sept. 2011.

- [17] H. Ma; J. Lai; Q. Feng; W. Yu; C. Zheng; Z. Zhao, "A Novel Valley-Fill SEPIC-Derived Power Supply Without Electrolytic Capacitor for LED Lighting Application," Power Electronics, IEEE Transactions on , vol.27, no.6, pp.3057,3071, June 2012.

- [18] M. Arias, D. Lamar, D. Balocco, A. Diallo, and J. Sebastian, "High-Efficiency LED Driver without Electrolytic Capacitor for Street Lighting," Industry Applications, IEEE Transactions on, vol. PP, pp. 1-1, 2012.

- [19]D. Bailey, "An Idea to Simplify LED Lighting Purchase Decisions," Bodo's Power, p. 18, July 2011 2011.

- [20] P. Imbertson and N. Mohan, "Asymmetrical Duty Cycle Permits Zero Switching Loss in PWM Circuits with No Conduction Loss Penalty," Industry Applications, IEEE Transaction on, vol. 29, p. 121, January 1993.

- [21] M. Arias, D.G. Lamar, F.F. Linera, D. Balocco, A. A. Diallo, J. Sebastián, "Design of a Soft-Switching Asymmetrical Half-Bridge Converter as Second Stage of an LED Driver for Street Lighting Application," Power Electronics, IEEE Transactions on , vol.27, no.3, pp.1608,1621, March 2012.

- [22] H. Kim, J. Jung, and J. Baek, "Analysis and Design of a Multi-output Converter using Asymmetrical PWM Half-bridge Flyback Converter Employing a Parallel-series Transformer," Industrial Electronics, IEEE Transactions on, vol. PP, pp. 1-1, 2012.

- [23] O. Garcia, J. A. Cobos, J. Uceda, and J. Sebastian, "Zero voltage switching in the PWM half bridge topology with complementary control and synchronous rectification," in Power Electronics Specialists Conference, 1995. PESC '95 Record., 26th Annual IEEE, 1995, pp. 286-291 vol.1.

- [24]L. Bor-Ren, C. Huann-Keng, T. Chao-Hsien, and C. Kao-Cheng, "Analysis and Implementation of an asymmetrical half-bridge converter," in Power Electronics and Drives Systems, 2005. PEDS 2005. International Conference on, 2005, pp. 407-412.

- [25]R. Oruganti, H. Phua Chee, J. T. K. Guan, and C. Liew Ah, "Softswitched DC/DC converter with PWM control," Power Electronics, IEEE Transactions on, vol. 13, pp. 102-114, 1998.

- [26] X. Xu, A. M. Khambadkone, T. M. Leong, and R. Oruganti, "A 1-MHz Zero-Voltage-Switching Asymmetrical Half-Bridge DC/DC Converter: Analysis and Design," Power Electronics, IEEE Transactions on, vol. 21, pp. 105-113, 2006.

- [27] Mishima , T.; Nakaoka , M.; , "Practical Evaluations of a ZVS-PWM DC–DC Converter With Secondary-Side Phase-Shifting Active Rectifier," Power Electronics, IEEE Transactions on, vol.26, no.12, pp.3896-3907, Dec. 2011.

- [28]J. A. Cobos, O. Garcia, J. Sebastian, J. Uceda, and F. Aldana, "Optimized Synchronous Rectification Stage for Low Output Voltage (3.3 V) DC/DC Conversion," presented at the Power Electronics Specialists Conference, 1994. PESC '94 Record., 25th Annual IEEE, Taipei (Taiwan), 1994.

- [29] M. Arias, M. Fernández, D. G. Lamar, D. Balocco, A. Aguissa Diallo, J. Sebastián, "High-Efficiency Asymmetrical Half-Bridge Converter Without Electrolytic Capacitor for Low-Output-Voltage AC-DC LED Drivers," Power Electronics, IEEE Transactions on, vol. 28, pp. 2539-2550, 2013.

- [30]L. Yi-Hsin, C. Tsou-Min, and C. Chern-Lin, "Analysis and design of the two-transformer asymmetrical half-bridge converter," in Industrial Electronics Society, 2005. IECON 2005. 31st Annual Conference of IEEE, 2005, p. 6 pp.

- [31]B. R. Lin and T. Chao-Hsien, "Analysis of Parallel-Connected Asymmetrical Soft-Switching Converter," Industrial Electronics, IEEE Transactions on, vol. 54, pp. 1642-1653, 2007.

- [32]S. Abedinpour, R. Liu, G. Fasullo, and K. Shenai, "Small-signal analysis of a new asymmetrical half-bridge DC-DC converter," in

Power Electronics Specialists Conference, 2000. PESC 00. 2000 IEEE 31st Annual, 2000, pp. 843-847 vol.2.

- [33] M. Arias, M. F. Diaz, D. G. Lamar, F. M. Fernández Linera and J. Sebastián, "Small-Signal and Large-Signal Analysis of the Two-Transformer Asymmetrical Half-Bridge Converter Operating in Continuous Conduction Mode," in IEEE Transactions on Power Electronics, vol. 29, no. 7, pp. 3547-3562, July 2014.

- [34] F. F. Linera, J. Sebastian, J. Diaz, and F. Nuno, "A novel feedforward loop implementation for the half-bridge complementary-control converter," in Applied Power Electronics Conference and Exposition, 1998. APEC '98. Conference Proceedings 1998., Thirteenth Annual, 1998, pp. 363-368 vol.1.

- [35] J. Sebastian, J. A. Cobos, O. Garcia, and J. Uceda, "An overall study of the half-bridge complementary-control DC-to-DC converter," in Power Electronics Specialists Conference, 1995. PESC '95 Record., 26th Annual IEEE, 1995, pp. 1229-1235 vol.2

- [36]M. Arias, M. F. Diaz, J. E. R. Cadierno, D. G. Lamar and J. Sebastián, "Digital Implementation of the Feedforward Loop of the Asymmetrical Half-Bridge Converter for LED Lighting Applications," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 3, no. 3, pp. 642-653, Sept. 2015.

- [37]J. B. Lee, K. B. Park, J. K. Kim, H. S. Youn and G. W. Moon, "A New Center-Tapped Half-Bridge Zeta Converter With Small Transformer DC-Offset Current and Low Voltage Stress," in IEEE Transactions on Power Electronics, vol. 30, no. 12, pp. 6593-6603, Dec. 2015.

- [38] J. I. Baek, J. K. Kim, J. B. Lee, H. S. Youn and G. W. Moon, "Integrated Asymmetrical Half-Bridge Zeta (AHBZ) Converter for DC/DC Stage of LED Driver With Wide Output Voltage Range and Low Output Current," in IEEE Transactions on Industrial Electronics, vol. 62, no. 12, pp. 7489-7498, Dec. 2015

- [39]http://www.st.com/content/ccc/resource/technical/document/application \_note/5b/8c/20/a9/32/14/45/3b/CD00256065.pdf/files/CD00256065.pdf /jcr:content/translations/en.CD00256065.pdf. Last access: 22nd may 2017.

- [40] Y. Wang, Y. Guan, D. Xu and W. Wang, "A CLCL Resonant DC/DC Converter for Two-Stage LED Driver System," in IEEE Transactions on Industrial Electronics, vol. 63, no. 5, pp. 2883-2891, May 2016.

- [41]M. F. Menke, R. V. Tambara, F. E. Bisogno, M. F. da Silva and Á. R. Seidel, "Two-stage digitally controlled led driver based on buck-boost and DC/DC LLC resonant converter," 2016 12th IEEE International Conference on Industry Applications (INDUSCON), Curitiba, 2016, pp. 1-8.

- [42] P. Fang, Y. j. Qiu, H. Wang and Y. F. Liu, "A Single-Stage Primary-Side-Controlled Off-line Flyback LED Driver With Ripple Cancellation," in IEEE Transactions on Power Electronics, vol. 32, no. 6, pp. 4700-4715, June 2017.

- [43]EEE Recommended Practices for Modulating Current in High-Brightness LEDs for Mitigating Health Risks to Viewers," in IEEE Std 1789-2015, vol., no., pp.1-80, June 5 2015.

- [44] B. Lehman and A. J. Wilkins, "Designing to Mitigate Effects of Flicker in LED Lighting: Reducing risks to health and safety," in IEEE Power Electronics Magazine, vol. 1, no. 3, pp. 18-26, Sept. 2014.