## Comparative Analysis between Three Level NPC Inverter and Dual Inverter Motor Drives for SPM

#### Synchronous Machines by

Anuradha Sampath Mudalige

Submitted to the Department of Electrical Engineering, Electronics, Computers and Systems in partial fulfillment of the requirements for the degree of Erasmus Mundus Joint Master Degree in Sustainable Transportation and Electrical Power Systems at the UNIVERSIDAD DE OVIEDO August 2019 © Universidad de Oviedo 2019. All rights reserved.

Author .....

Certified by..... Andrea Formentini Assistant Professor Thesis Supervisor Certified by.... Luca Rovere PhD Thesis Supervisor

### Comparative Analysis between Three Level NPC Inverter and Dual Inverter Motor Drives for SPM Synchronous Machines

by

Anuradha Sampath Mudalige

Submitted to the Department of Electrical Engineering, Electronics, Computers and Systems on August 30, 2019, in partial fulfillment of the requirements for the degree of Erasmus Mundus Joint Master Degree in Sustainable Transportation and Electrical Power Systems

#### Abstract

Permanent Magnet Synchronous Machines (PMSM) have gained increasing interest in industrial applications. Selection of the best motor drive topology for an application is a decision that involves consideration of various factors. In this research, a comprehensive comparative analysis is conducted between a Three Level Neutral Point Clamped (NPC) inverter based motor drive and a dual inverter based motor drive for Surface Permanent Magnet Synchronous Machines (SPMSM).

Control systems and modulation schemes for the two drive topologies are designed considering a SPMSM available within the facilities of the Power Electronics, Machines and Control Group (PEMC) of the University of Nottingham (UoN). Comparative analysis is conducted via mathematical modelling of the drive topologies and through a series of simulations in Matlab/Simulink for control implementations in conjunction with PLECS Blockset for thermal modelling of power electronic elements. Finally, feasibility of the two drive control philosophies are experimented by coding the controllers in C and implementing them in a laboratory experimental setup.

#### **Keywords**:

SPMSM, three level NPC, dual-inverter motor drive, uCube, Matlab, Simulink, PLECS Blockset, thermal modelling, C

Thesis Supervisor: Andrea Formentini Title: Assistant Professor

Thesis Supervisor: Luca Rovere

Title: PhD

#### Acknowledgments

This work was conducted at the Power Electronics, Machines and Control Group (PEMC) of the University of Nottingham - UK in partial fulfilment of the requirements for the Erasmus Mundus Joint Master Degree in Sustainable Transportation and Electrical Power Systems (EMJMD STEPS).

I would like to thank thesis supervisors Prof. Andrea Formentini and Dr. Luca Rovere for their constant guidance which was instrumental for the success of this work. The opportunity given to access the PEMC laboratory facilities and the support extended in experimental work is noted with gratitude.

It is with profound gratitude that I acknowledge the professors from University of Oviedo, University of Nottingham and Polytechnic Institute of Coimbra whose efforts were behind my success story with EMJMD STEPS. The Education, Audiovisual and Culture Executive Agency of the European Union (EACEA) is thankfully noted for its financial assistance.

I wish to express my indebtedness to my beloved parents and brother for the moral support, encouragement and guidance extended in many ways at all stages of my life.

Last but not least, I would like to thank all the people and colleagues I met from around the world for providing a good company for two years of postgraduate studies across three countries in Europe.

## Contents

| 1        | Intr | oduction                                                               | <b>21</b> |

|----------|------|------------------------------------------------------------------------|-----------|

|          | 1.1  | Background                                                             | 21        |

|          | 1.2  | Motivation and Research Objectives                                     | 21        |

|          | 1.3  | Research approach and organization of the thesis                       | 23        |

|          | 1.4  | Tools used in the research                                             | 24        |

| <b>2</b> | Stat | te of the Art                                                          | 27        |

|          | 2.1  | Applications of Synchronous Machines                                   | 27        |

|          | 2.2  | PMSM drive topologies                                                  | 29        |

|          |      | 2.2.1 Single inverter drive topologies                                 | 29        |

|          |      | 2.2.2 Dual inverter drives with separate voltage sources               | 29        |

|          |      | 2.2.3 Dual inverter drives with a common voltage source $\ldots$ .     | 30        |

|          |      | 2.2.4 Dual inverter drives with a single voltage source and a floating |           |

|          |      | capacitor                                                              | 31        |

|          | 2.3  | Selection of modulation strategies for the drives                      | 32        |

| 3        | Mat  | thematical Model for OEW-PMSM                                          | 35        |

|          | 3.1  | Mathematical model of a conventional PMSM                              | 35        |

|          | 3.2  | Extension of the mathematical model to OEW machine configuration       | 36        |

|          | 3.3  | Implementation of OEW-PMSM mathematical model                          | 38        |

| 4        | Dev  | elopment of Modulation Schemes                                         | 41        |

|          | 4.1  | Implementation of SVPWM scheme for two level inverter                  | 42        |

|          |      | 4.1.1   | Operating principle                                                  | 43 |

|----------|------|---------|----------------------------------------------------------------------|----|

|          |      | 4.1.2   | Main steps                                                           | 43 |

|          |      | 4.1.3   | Implementation of the modulation scheme in Simulink $\ldots$         | 45 |

|          | 4.2  | Imple   | mentation of SVPWM scheme for three level NPC inverter               | 47 |

|          |      | 4.2.1   | Operating principle                                                  | 49 |

|          |      | 4.2.2   | Main steps                                                           | 50 |

|          |      | 4.2.3   | Implementation of the modulation scheme in Simulink $\ldots$         | 52 |

|          | 4.3  | THD a   | analysis of two level and three level NPC inverter voltage waveforms | 53 |

| <b>5</b> | Cor  | ntrol S | ystem for Three Level NPC Inverter Drive                             | 55 |

|          | 5.1  | Design  | n specifications                                                     | 55 |

|          |      | 5.1.1   | Voltage and current constraints                                      | 55 |

|          | 5.2  | Contro  | ol scheme                                                            | 56 |

|          |      | 5.2.1   | Inner control loops                                                  | 56 |

|          |      | 5.2.2   | Outer control loops                                                  | 58 |

|          |      | 5.2.3   | Concept of Maximum Torque Per Amp - (MTPA) for SPMSM                 | 58 |

| 6        | Cor  | ntrol S | ystem for Dual Inverter Drive with a Floating Capacitor              |    |

|          | Brie | dge     |                                                                      | 61 |

|          | 6.1  | Design  | n specifications                                                     | 61 |

|          |      | 6.1.1   | Voltage and current constraints                                      | 62 |

|          | 6.2  | Contro  | ol Scheme                                                            | 62 |

|          |      | 6.2.1   | Control of inverter A                                                | 63 |

|          |      | 6.2.2   | Control of inverter B                                                | 65 |

| 7        | Lab  | orator  | y Experiments                                                        | 69 |

|          | 7.1  | Exper   | imental setup                                                        | 69 |

|          | 7.2  | Imple   | mentation of single inverter based speed control system              | 72 |

|          |      | 7.2.1   | Control software development                                         | 72 |

|          |      | 7.2.2   | Implementation procedure                                             | 73 |

|          |      | 7.2.3   | Experimental results                                                 | 76 |

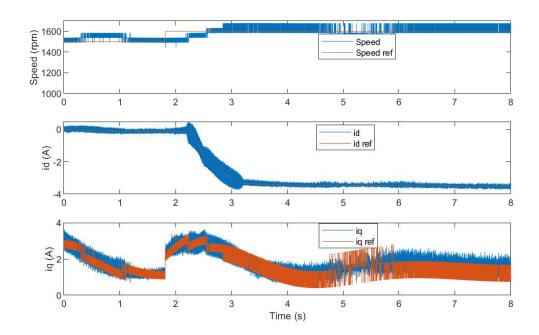

|              | 7.3 | Imple          | mentation of dual inverter based speed control system with a          |     |

|--------------|-----|----------------|-----------------------------------------------------------------------|-----|

|              |     | floatin        | ng capacitor bridge                                                   | 78  |

|              |     | 7.3.1          | Control software development                                          | 79  |

|              |     | 7.3.2          | Implementation procedure                                              | 79  |

|              |     | 7.3.3          | Experimental results                                                  | 80  |

|              | 7.4 | Imple          | mentation of dual inverter drive with a common voltage source .       | 81  |

|              |     | 7.4.1          | Experimental procedure                                                | 82  |

|              |     | 7.4.2          | Experimental results                                                  | 83  |

| 8            | Cor | nparis         | on of Drive Topologies                                                | 85  |

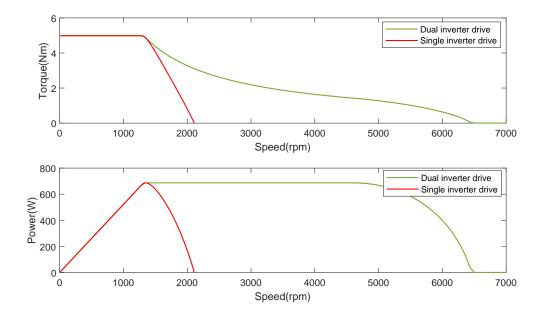

|              | 8.1 | Speed          | range of the machine, limits of deliverable torque and mechanical     |     |

|              |     | power          | ·                                                                     | 85  |

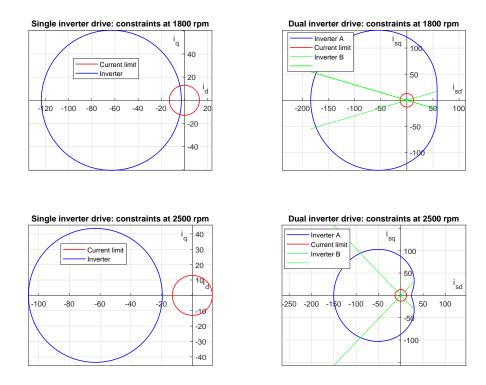

|              |     | 8.1.1          | Analysis based on admissible domain of stator currents $\ . \ . \ .$  | 85  |

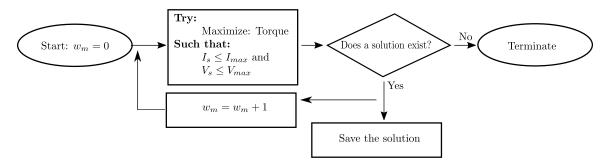

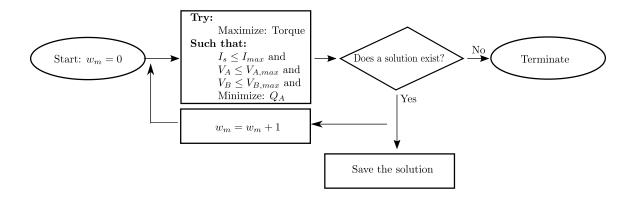

|              |     | 8.1.2          | Analysis by formulating a maximization problem $\ldots \ldots \ldots$ | 88  |

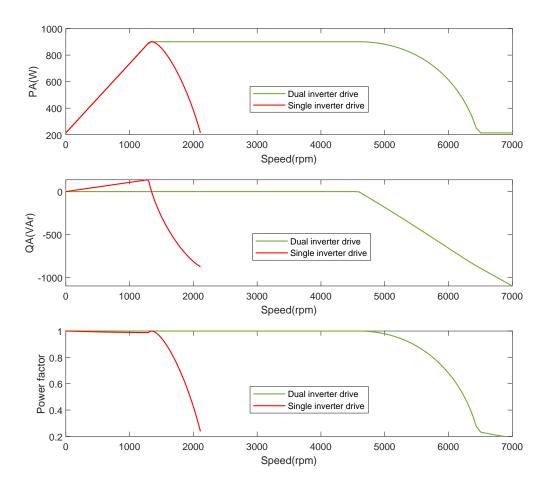

|              | 8.2 | Main           | inverter active and reactive power delivery                           | 91  |

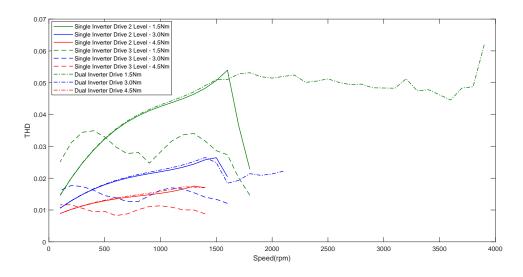

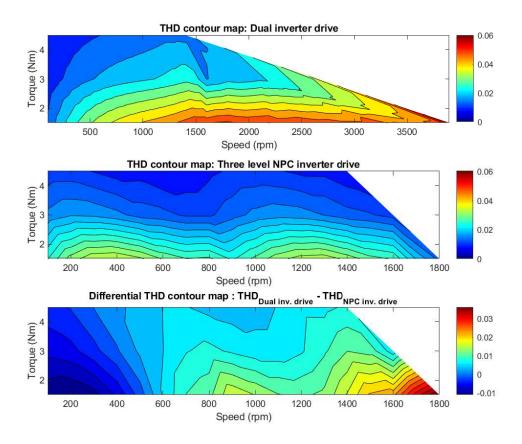

|              | 8.3 | THD            | of stator current                                                     | 93  |

|              |     | 8.3.1          | Overview                                                              | 93  |

|              |     | 8.3.2          | Simulation procedure                                                  | 93  |

|              |     | 8.3.3          | Simulation results and analysis                                       | 94  |

|              | 8.4 | Efficie        | ency analysis                                                         | 96  |

|              |     | 8.4.1          | Overview                                                              | 96  |

|              |     | 8.4.2          | Losses in the system and definition for efficiency                    | 96  |

|              |     | 8.4.3          | Thermal modelling of the motor drives                                 | 97  |

|              |     | 8.4.4          | Simulation results and analysis                                       | 100 |

|              | 8.5 | Fault          | tolerant capability                                                   | 104 |

| 9            | Cor | nclusio        | ns and Future Work                                                    | 107 |

|              | 9.1 | Conclu         | usions                                                                | 107 |

|              | 9.2 | Future         | e work                                                                | 108 |

| $\mathbf{A}$ | Tab | $\mathbf{les}$ |                                                                       | 111 |

| В | Figures                                              | 113 |

|---|------------------------------------------------------|-----|

| С | Programming                                          | 115 |

|   | C.1 C code for dual inverter drive vector controller | 115 |

## List of Figures

| 1-1  | Schematic diagram of the power electronic arrangements of the drive     |    |

|------|-------------------------------------------------------------------------|----|

|      | topologies                                                              | 22 |

| 2-1  | Classification of motors used in industrial applications $[34]$         | 28 |

| 2-2  | Schematic of dual inverter drive topology with separate voltage sources | 30 |

| 2-3  | Schematic of dual inverter drive topology with common voltage source    | 31 |

| 3-4  | Masked view of the implemented OEW-PMSM model                           | 39 |

| 4-1  | Schematic representation of a typical two level inverter                | 42 |

| 4-2  | Space-vector diagram for a two-level inverter                           | 43 |

| 4-3  | Space Vector Pulse Width Modulator for two level inverter imple-        |    |

|      | mented in Simulink                                                      | 46 |

| 4-4  | First level internal view of the two level Space Vector Pulse Width     |    |

|      | Modulator                                                               | 46 |

| 4-5  | Schematic representation of a typical three level NPC inverter $\ldots$ | 47 |

| 4-6  | Space-vector diagram for three-level NPC inverter                       | 48 |

| 4-7  | Effects of different voltage vectors on DC-link capacitor voltage       | 49 |

| 4-8  | Space Vector Pulse Width Modulator for three level NPC inverter im-     |    |

|      | plemented in Simulink                                                   | 52 |

| 4-9  | First level internal view of the three level Space Vector Pulse Width   |    |

|      | Modulator                                                               | 52 |

| 4-10 | Phase-to-phase voltages and phase currents with two inverters           | 53 |

| 4-11 | THD of phase-to-phase voltage waveforms                                 | 54 |

| 5 - 1 | Speed control system for the SPMSM based on a three level NPC              |     |

|-------|----------------------------------------------------------------------------|-----|

|       | inverter drive                                                             | 57  |

| 7-1   | Experimental setup                                                         | 70  |

| 7-2   | Closer views of the SPMSM and uCube                                        | 71  |

| 7-3   | d axis current response for a step reference change                        | 76  |

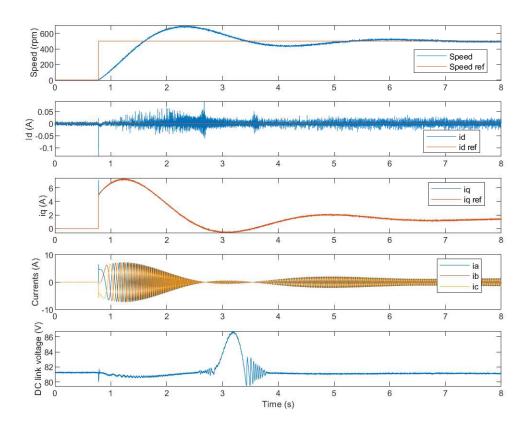

| 7-4   | Performance of the control system for a step reference change in speed     |     |

|       | below flux weakening region                                                | 77  |

| 7-5   | Performance of the control system for a step reference change in speed     |     |

|       | into the flux weakening region                                             | 78  |

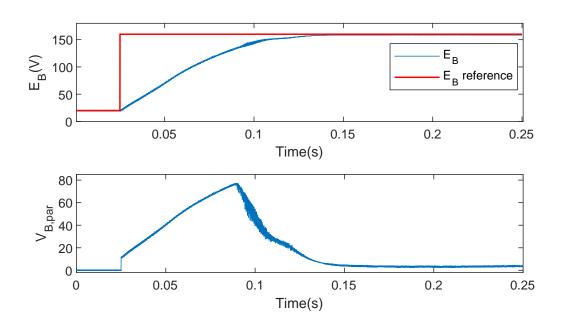

| 7-6   | Performance of the voltage regulator for a step voltage reference change   |     |

|       | from 20V to 160V                                                           | 81  |

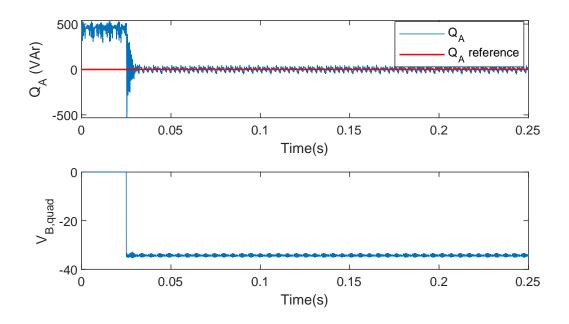

| 7-7   | Performance of the reactive power controller                               | 82  |

| 7-8   | Zero-Sequence Current flow in dual inverter drive with shared DC links.    | 83  |

| 8-1   | Representation of voltage and current constraints for single and dual      |     |

|       | inverter drives at 1800rpm and 2500rpm                                     | 88  |

| 8-2   | Proposed algorithm for obtaining operating limits of the single inverter   |     |

|       | drive                                                                      | 89  |

| 8-3   | Proposed algorithm for obtaining operating limits of the dual inverter     |     |

|       | drive                                                                      | 89  |

| 8-4   | Torque and mechanical power limits for single inverter and dual in-        |     |

|       | verter drives                                                              | 90  |

| 8-5   | Main inverter active-reactive power delivery and power factor $\ldots$     | 92  |

| 8-6   | THD of stator current                                                      | 94  |

| 8-7   | THD of stator current: contour map representation                          | 95  |

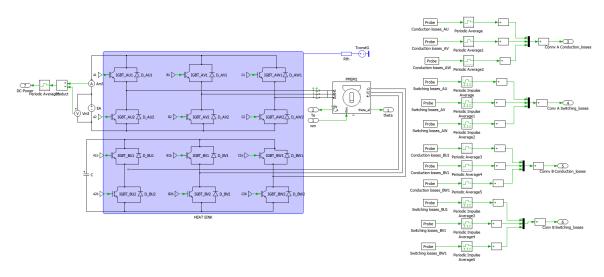

| 8-8   | PLECS thermal model for dual inverter drive                                | 97  |

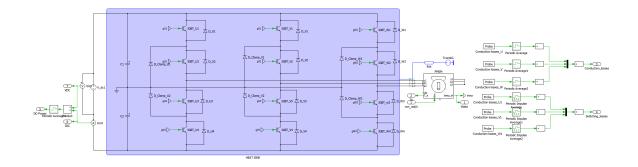

| 8-9   | PLECS thermal model for three level NPC inverter drive                     | 98  |

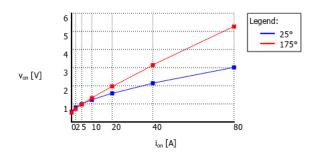

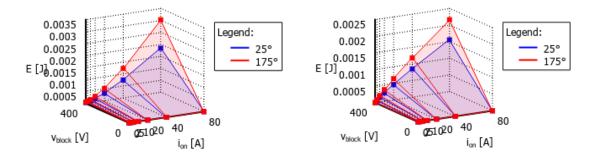

| 8-10  | 2D look-up table for conduction loss calculation                           | 99  |

| 8-11  | 3D look-up table for switching loss calculation                            | 100 |

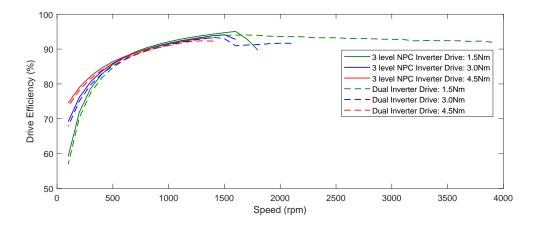

| 8-12  | Efficiency of the two drive topologies assessed at three torque levels . 1 | 00  |

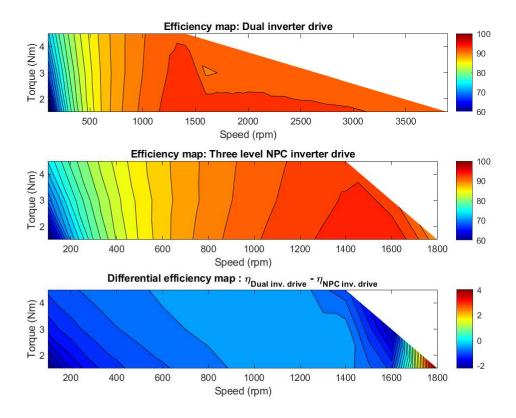

| 8-13 | Efficiency maps                                           | 101 |

|------|-----------------------------------------------------------|-----|

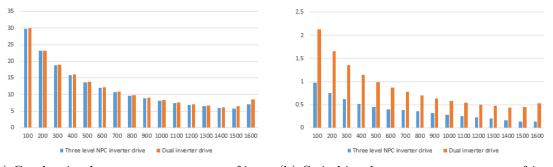

| 8-14 | Split of drive losses at 3.0Nm load torque                | 102 |

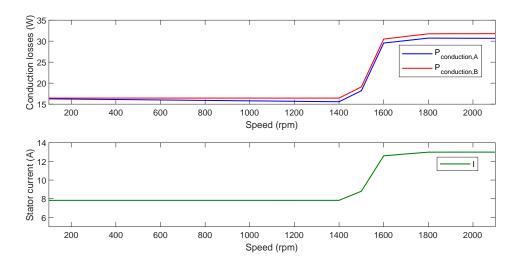

| 8-15 | Dual inverter drive: split of conduction losses           | 104 |

| 8-16 | Dual inverter drive: split of switching losses            | 105 |

| B-1  | Sequence of switching states for two level inverter SVPWM | 113 |

## List of Tables

| 1.1 | SPMSM Parameters                                                          | 23  |

|-----|---------------------------------------------------------------------------|-----|

| 4.1 | Two level inverter switching states convention                            | 42  |

| 4.2 | Three level NPC inverter switching states convention                      | 48  |

| 4.3 | Three level NPC inverter different switching combinations $\ldots \ldots$ | 49  |

| 4.4 | Formulas for NTV dwelling time calculations                               | 51  |

| 6.1 | Dual inverter drive design specifications                                 | 62  |

| A.1 | Three level NPC inverter SVPWM switching sequences                        | 112 |

## Acronyms

| AC          | Alternating Current.                                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------|

| ADC         | Analog to Digital Conversion.                                                                          |

| BDCM        | Brushless DC Motor.                                                                                    |

| EACEA       | The Education, Audiovisual and Culture Ex-<br>ecutive Agency of the European Union.                    |

| EMJMD STEPS | Erasmus Mundus Joint Master Degree in Sus-<br>tainable Transportation and Electrical Power<br>Systems. |

| EV          | Electric Vehicle.                                                                                      |

| FOC         | Field Oriented Control.                                                                                |

| FPGA        | Field Programmable Gate Array.                                                                         |

| HEV         | Hybrid Electric Vehicle.                                                                               |

| IM          | Induction Motor.                                                                                       |

| ISR         | Interrupt Servive Routine.                                                                             |

| NPC         | Neutral Point Clamped.                                                                                 |

| NTV         | Nearest Three Vectors.                                                                                 |

| OEW      | Open-End Winding.                        |  |

|----------|------------------------------------------|--|

| OEW-PMSM | Open-End Winding Permanent Magnet Syn-   |  |

|          | chronous Machine.                        |  |

|          |                                          |  |

| PEMC     | Power Electronics, Machines and Control  |  |

|          | Group.                                   |  |

| PL       | Programmable Logic.                      |  |

| PM       | Permanent Magnet.                        |  |

| PMSM     | Permanent Magnet Synchronous Machine.    |  |

| PS       | Processing System.                       |  |

| PWM      | Pulse Width Modulation.                  |  |

|          |                                          |  |

| SHEPWM   | Selected Harmonic Elimination PWM.       |  |

| SoC      | System on Chip.                          |  |

| SPM      | Surface Permanent Magnet.                |  |

| SPMSM    | Surface Permanent Magnet Synchronous Ma- |  |

|          | chine.                                   |  |

| SPWM     | Sinusoidal Pulse Width Modulation.       |  |

| SPWMTHI  | SPWM with Third Harmonic Injection.      |  |

| SVPWM    | Space Vector PWM.                        |  |

|          |                                          |  |

| UoN      | University of Nottingham.                |  |

|          |                                          |  |

| XSDK     | Xilinx Software Development Kit.         |  |

|          |                                          |  |

| ZSC      | Zero Sequence Current.                   |  |

## Nomenclature

- $\bar{\varphi_s}, \varphi_{sd}, \varphi_{sq}$  Stator flux vector and its d,q components

- $\bar{i_s},\,i_{sd},\,i_{sq}$  Stator current vector and its d,q components

- $\bar{V}_A$ ,  $V_{Ad}$ ,  $V_{Aq}$  Inverter A voltage vector and its d,q, components

- $\bar{V}_B, V_{Bd}, V_{Bq}$  Inverter B voltage vector and its d,q, components

$\bar{v_s}, v_{sd}, v_{sq}$  stator voltage vector and its d,q components

- $\omega$  shaft speed in electrical rad/s

- $E_A$  DC link voltage of the three level NPC inverter , DC link voltage of the inverter A of dual inverter drive

- ${\cal I}_{s,max}\,$  Maximum allowable stator current of the machine

- $L_d, L_q$  d,q axix stator inductance

- $L_s$  Stator inductance

- p number of pole pairs

- $R_s$  Stator resistance

- T Electro-mechanocal torque

- $V_{A,max}$  Maximum limit of three level NPC inerter voltage vector, Maximum limit of inverter A voltage vector

- $V_{B,max}$  Maximum limit of inverter B voltage vector

$V_{B,par}$  Component of the inverter B voltage vector parallel to stator current vector

- $V_{B,quad}$  Component of the inverter B voltage vector orthogonal to stator current vector

- Inverter A Inverter connected with the power supply in dual inverter drive with floating capacitor bridge

- Inverter B Inverter associated with the floating capacitor in dual inverter drive with floating capacitor bridge

### Chapter 1

## Introduction

#### 1.1 Background

Many desirable features offered by Permanent Magnet Synchronous Machine (PMSM)s such as high torque density and better efficiency of the machine design, have made them a popular choice in industrial applications. Overall performance of the motor drive application, however, not only depends on the electrical machine, but also on associated control system and most importantly on the motor drive topology that feeds the machine. Therefore, selection of the best motor drive topology for a given industrial application involving a PMSM is an important engineering decision to be made.

In this research, performance of two motor drive topologies are comparatively assessed for their suitability in PMSM applications, exclusively focusing on Surface Permanent Magnet Synchronous Machine (SPMSM)s that find widespread industrial applications.

#### **1.2** Motivation and Research Objectives

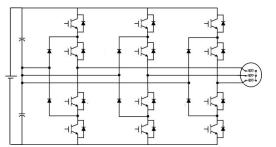

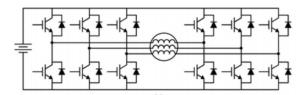

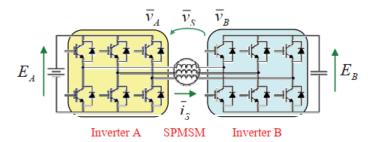

Main objective of this research is to comparatively analyse the performance of a SPMSM motor drive based on a three level Neutral Point Clamped (NPC) inverter against a dual inverter drive with a floating capacitor bridge whose power electronics arrangements are shown in Figure 1-1a and 1-1b respectively.

(a) Three level NPC inverter drive

(b) Dual inverter drive with a floating capacitor

Figure 1-1: Schematic diagram of the power electronic arrangements of the drive topologies

First topology is essentially based on classical PMSM motor control architecture, however, instead of a two level inverter, this drive employs a three level NPC inverter to feed the machine.

The second drive topology considered in this research is based on a comparatively novel control philosophy for electrical machines. In this case, it consists of two, standard two-level inverters feeding the machine in its Open-End Winding (OEW) configuration with a floating capacitor associated with one of the inverters. This topology is one of the three dual inverter drive topologies that have gained extensive interest in academia in recent history.

A performance analysis between these two drive topologies is particularly interesting due to three reasons. Firstly, as clearly identifiable in the Figure 1-1, both drive topologies consist of equal number of power electronic switching devices. Secondly, dual inverter drives are generally assumed to generate multi-level stator voltage waveforms comparable to a multi-level inverter drives, which makes it worth investigating the performance of such a dual inverter drive against a three level inverter drive. Thirdly, even though there are many studies in literature that attempt to make comparisons between classical motor drives based on two level and three level inverters (such as [12]) or between different dual inverter drive topologies (such as [38]), no study in the literature has made an effort to compare the two drive topologies that are the subject of this research.

Performance of the two drive topologies are to be assessed considering their applicability for a low power SPMSM prototype available within the facilities of the Power Electronics, Machines and Control Group (PEMC) of the University of Nottingham (UoN). Specifications of this SPMSM have been presented in Table 1.1 [29]

| Parameter                             | Value             |

|---------------------------------------|-------------------|

| Pole number 2p                        | 6                 |

| PM material                           | NdFeB             |

| PM remanence flux density $B_{ref}$   | 1.24T             |

| PM relative permeability $\mu_r$      | 1.031             |

| Power rating                          | $1.5 \mathrm{kW}$ |

| Peak value of the current $I_{rated}$ | 13A               |

| Rated speed $\omega_{m,rated}$        | 3000rpm           |

| Torque constant $k_T$                 | 0.128 Nm/A        |

| Line to line voltage constant $k_v$   | 15.5  V/krpm      |

| Outer stator diameter                 | 95 mm             |

| Inner stator diameter                 | 49.5 mm           |

| Axial length                          | 90 mm             |

| Airgap length                         | 1 mm              |

| Magnets thickness                     | 4 mm              |

| Stator inductance $L_d$ , $L_q$       | 1.35 mH           |

| Stator resistance $R_s$               | $0.8434 \ \Omega$ |

Table 1.1: SPMSM Parameters

## 1.3 Research approach and organization of the thesis

Research was commenced with a literature review on the broader context of the research theme and state of the art developments in PMSM motor drive topologies. Most significant findings of this review are briefed in **Chapter 2** of this thesis.

Thereafter, the mathematical model of a PMSM was investigated, and its ex-

tended version for OEW configuration of a PMSM was derived and implemented in Simulink. Details of this implementation have been presented in **Chapter 3**

It was followed by the development of modulation schemes (based on Space Vector Modulation strategy) for two level and three level NPC inverters which are the fundamental power electronic systems involved in studied PMSM drive topologies. Work carried out in this respect are presented in **Chapter 4**

Control systems for three level and dual inverter motor drives are presented in Chapter 5 and Chapter 6 respectively.

Laboratory experiments carried out to implement the control systems associated with the two drive topologies are explained in **Chapter 7**.

Results of the comparative analysis conducted on two SPMSM motor drive topologies are presented in **Chapter 8**.

Thesis ends with its **Chapter 9** that dedicates to present conclusions of the research and proposals for possible future work.

#### 1.4 Tools used in the research

Simulation studies related to control implementations in this research were conducted in **Simulink**<sup>®</sup>(version 9.2) graphical programming environment by **MathWorks**, in conjunction with **MATLAB**<sup>®</sup> multi-paradigm numerical computing environment and its proprietary programming language.

**PLECS Blockset**(version 4.1.8), a popular tool of choice for high speed simulations of power electronic systems[1] by **Plexim**, was used to conduct thermal modelling of the designed motor drive systems. PLECS Blockset facilitates seamless integration with  $MATLAB^{\ensuremath{\mathbb{R}}}/Simulink^{\ensuremath{\mathbb{R}}}$ .

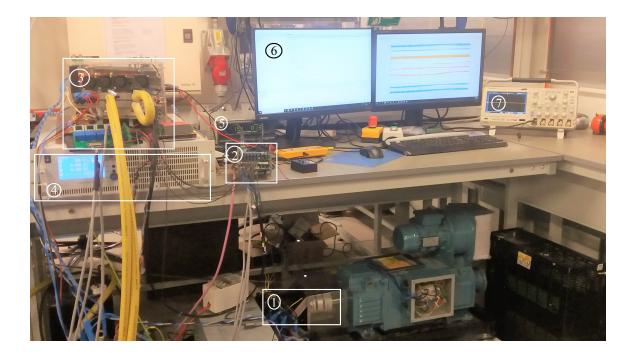

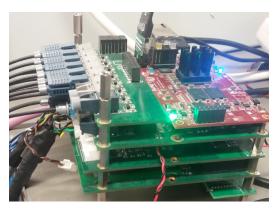

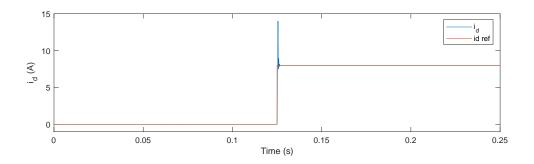

Laboratory experiments related to this work were based on a SPMSM prototype available within the facilities of PEMC of the UoN. Control systems were implemented in uCube [16], a custom made control platform developed at the University of Nottingham. C programming language (with occasional use of C++) was used to program the uCube with the aid of Xilinx Software Development Kit (XSDK) (version 2017.4)

## Chapter 2

### State of the Art

This chapter presents a brief review on applications of PMSMs and state of the art motor drive topologies. It also contains a review on state of the art inverter modulation schemes that formed the basis for rational selection of modulation strategies for the drive topologies in subsequent design steps.

#### 2.1 Applications of Synchronous Machines

Synchronous machines are well known for their widespread applications as synchronous generators in AC power grids. However, their applications are not just limited to generating mode. Many desirable features of synchronous machines, specifically, those of PMSMs such as higher power density, higher torque density [6], higher efficiency and lesser heating [34] have made them a popular choice for industrial applications including Electric Vehicle (EV) applications.

A common classification of electric motors used in industrial applications is shown in Figure 2-1. Some research has indicated that Permanent Magnet (PM) motor drives, including PMSMs and Brushless DC Motor (BDCM)s could become serious competitors to the Induction Motor (IM)s due to their overall better efficiency indicators, effective use of reluctance torque, lesser losses and compact motor size [26],[33]. In PMSMs, power losses are mainly associated with the stator whereas the rotor offers an almost loss-free design [8]

Figure 2-1: Classification of motors used in industrial applications [34]

The electric motor represents one of the key components for EVs. In such an application, the motor used for the drive train is desirable to have a high torque and power density, a high starting torque, a wide speed range, a high intermittent overload capability and a reasonable price ([11], [41], [43], [20]). In such a context, PMSMs are becoming more attractive due to their inherent features that fulfil these expectations.[14] Moreover, the fact that a relatively low-power PMSM can provide sufficient power for the drive train of a medium sized car, thus minimizing the requirement for expensive permanent magnets, has made PMSMs a popular choice for Hybrid Electric Vehicle (HEV)s. Some good examples are Toyota Prius and Honda Insight HEVs which are both equipped with PMSMs [40], [10].

SPMSMs, the specific type of PMSM focused in this research, offer additional benefits such as simplified manufacturing process, robustness and lower cost due to their solid rotor core design. However, one of the drawbacks of SPMSMs is their limited speed range compared to rest of the PMSM types, but research on dual inverter drive topologies have shown that this drawback can be effectively resolved by employing dual inverter motor drives in OEW configuration of the machine. [6]

#### 2.2 PMSM drive topologies

Motor drive topologies, in general, can be divided into two major classes namely single inverter based drives and dual inverter based drives. Single inverter drive topology can be considered as the most common and classical motor drive topology in industrial applications. Dual inverter based motor drives are emerging nowadays as a promising alternative for conventional motor drives.

There has been much research investigating applicability of dual inverter drive topologies for different types of electrical machines. In [13], [19] and [24] authors have presented their findings on applying dual inverter drive topology for IM applications. [27] proposes a novel power circuit topology for IM dual inverter drive topologies, in which a rectifier-inverter is embedded within a conventional two-level inverter. Author in [31] has extensively studied the applicability of dual inverter drive topologies for PMSMs. Reference [25] discusses applicability of dual inverter drive topologies for Synchronous Reluctance Machines and proposes a speed control system based on one of the dual inverter drive topologies.

#### 2.2.1 Single inverter drive topologies

Single inverter drives, controlled based on Field Oriented Control (FOC) philosophy, and fed by two level voltage source inverters have been the most common motor drive in majority of the applications involving PMSMs and IMs. Applications of multi level inverters such as three level NPC inverters can also be found in motor drive applications. In [12], the authors have presented an extensive comparative analysis between two level and three-level inverter drives for EV applications.

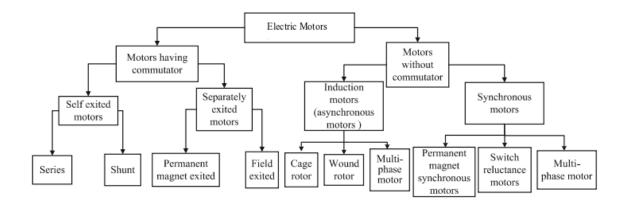

#### 2.2.2 Dual inverter drives with separate voltage sources

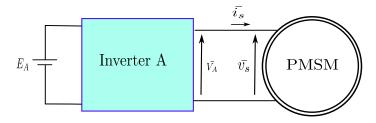

Power electronics arrangement of this drive topology has been shown in Figure 2-2. It is evident that the two two-level inverters that feed the machine in its OEW configurations have their own DC power supplies in this topology.

Figure 2-2: Schematic of dual inverter drive topology with separate voltage sources

Presence of separate DC power supplies facilitates maximization of the output voltage vector on the machine's stator produced by the drive while avoiding the common mode impedance. Some of the key advantages of this topology are no generation of common mode (zero sequence) currents in the motor winding and best DC bus voltage utilization. However, the fact that the drive requires two separate DC power sources, renders it more expensive and less practical in an industrial application. Requirement for separate DC voltage sources may be obtained by means of isolated voltage transformers or with completely independent battery packs. Specially, in terms of EV applications, having two separate batteries on board is not convenient for obvious reasons such as weight and cost. [29]

Authors in [18],[21] and [17] have proved one of the distinct features of this dual inverter topology, i.e. the capability to regulate the load power sharing between the two power sources within a switching period. This allows the control system to adjust the power flow between two DC power sources and manage their state of charge in an effective manner.

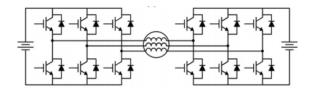

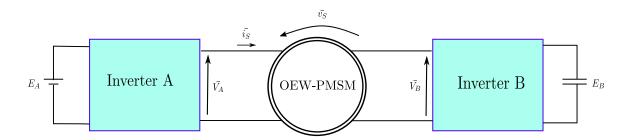

#### 2.2.3 Dual inverter drives with a common voltage source

Inverter and power source arrangement of a typical dual inverter drive with a common voltage source is shown in Figure 2-3.

The obvious advantages of employing a single DC power source for the drive are reduced cost, minimal weight and overall simplicity of the the drive system. This has made it to attract the attention of the research community and there are many studies such as [29] that exclusively studies applicability of this topology for industrial

Figure 2-3: Schematic of dual inverter drive topology with common voltage source

applications.

However, one of the critical flaws of this design is the zero-sequence current loop it allows in the system leading to flow of Zero Sequence Current (ZSC)s. Authors in [42] and [35] have researched extensively to investigate root causes for the presence of ZSC in this drive topology. The author in [29] has investigated the possibility to eliminate the presence of ZSC in high speed PMSM applications involving this drive topology.

### 2.2.4 Dual inverter drives with a single voltage source and a floating capacitor

The third dual inverter drive topology, the one with a single voltage source with a floating capacitor bridge is the drive topology that will be focused in this research. Schematic representation of this drive topology was already presented in Chapter 1. The control philosophy of this drive topology can be found in Chapter 6.

One of the key advantages of this drive topology is the absence of ZSC flow in the system in contrary to the dual inverter drive topology with a common DC power source. In EV applications, it is a common practice to employ a DC-DC converter before the inverter that feeds the electrical motor to have a voltage boost [29]. This drive topology can serve the same purpose of voltage boost with additional benefits such as increased speed range of the machine. In [22] authors have also shown the possibility to increase the constant torque region of the machine by employing this drive topology.

#### 2.3 Selection of modulation strategies for the drives

This section summarises the results of the literature review conducted in order to select suitable modulation strategies for the drive systems that are analysed in this research.

Modulation strategies can be classified into two main classes viz. fundamental switching frequency modulation schemes and high frequency Pulse Width Modulation (PWM) schemes[36]. Former class of modulation schemes are simple to implement and less resource intensive in terms of required processing power, and result in low switching losses due to limited number of switching events per cycle of fundamental frequency. However, they suffer with high level of harmonics in the current waveform, that needs be filtered by bulky and uneconomical low-pass filters[7].

Contrary to fundamental frequency modulation schemes, high frequency PWM schemes allow the designer to optimize the harmonic content in the waveforms [7]. For an application such as a motor drive considered in this study, less harmonics in resulting stator current waveforms, in turn result in reduced torque ripples and minimal losses in the machine.

There are many possible PWM schemes proposed in literature. Some of the most common are Sinusoidal Pulse Width Modulation (SPWM), SPWM with Third Harmonic Injection (SPWMTHI), Selected Harmonic Elimination PWM (SHEPWM) and Space Vector PWM (SVPWM) [7][36].

SPWM technique is probably the most commonly used scheme and is simple to implement. SVPWM schems, in contrary, are computation intensive, and somewhat complicated in implementation, yet can be treated as the best among all the PWM techniques [7] in terms of utilization of DC link[30] (DC link utilization for SPWM is restricted to  $V_{DC}/2$  whereas SVPWM schemes can utilize the DC link up to  $V_{DC}/\sqrt{3}$ ), current ripples and ease of adaptation for multi level inverter topologies. Therefore, modulation schemes for both two level and three level NPC inverters used in the motor drives developed in this study are designed based on corresponding SVPWM schemes.

## Chapter 3

## Mathematical Model for OEW-PMSM

This chapter explains the mathematical model of an Open-End Winding Permanent Magnet Synchronous Machine (OEW-PMSM) that will be used in subsequent studies related to the dual inverter motor drive. Chapter commences by explaining the mathematical model of a conventional PMSM and will be followed by presenting its extension to OEW configuration. At the end of the chapter, there is a section explaining the work carried out to implement this mathematical model in Simulink.

#### 3.1 Mathematical model of a conventional PMSM

Fig. 3-1 shows the schematic diagram of a conventional PMSM driven by a single inverter drive system, in terms of space vectors, under the assumption that d axis is aligned with the PM excitation field. Mathematical model for the machine in dq0 reference frame can be expressed in terms of equations 3.1 - 3.5 ([6],[29])

$$v_{sd} = R_s i_{sd} - \omega \varphi_{sq} + \frac{d\varphi_{sd}}{dt}$$

(3.1)

$$v_{sq} = R_s i_{sq} + \omega \varphi_{sd} + \frac{d\varphi_{sq}}{dt}$$

(3.2)

Figure 3-1: Schematic diagram of a conventional PMSM fed by a single inverter system, represented in terms of space vectors

$$\varphi_{sd} = L_d i_{sd} + \varphi_e \tag{3.3}$$

$$\varphi_{sq} = L_q i_{sq} \tag{3.4}$$

$$T = \frac{3}{2}p[\varphi_e i_{sq} + i_{sd}i_{sq}(L_d - L_q)]$$

(3.5)

where  $v_{sd}$  and  $v_{sq}$  are the d-q components of the stator voltage vector  $\bar{v}_s$ ,  $\varphi_{sd}$  and  $\varphi_{sq}$  are the d-q components of the stator flux vector  $\bar{\varphi}_s$  and T is the electromechanical torque generated by the machine.  $i_{sd}$  and  $i_{sq}$  represent the d-q components of the stator current vector  $\bar{i}_s$ . d,q stator inductances, stator resistance and permanent magnet flux are given by  $L_d, L_q, R_s$  and  $\varphi_e$  respectively.

With reference to Fig. 3-1, relationship between machine's stator voltage vector  $\bar{v_s}$  and the inverter output voltage vector  $\bar{V_A}$  in this drive system is given by equation 3.6

$$v_s = \bar{V_A} \tag{3.6}$$

# 3.2 Extension of the mathematical model to OEW machine configuration

In OEW configuration of a PMSM, one can access either ends of the three phase stator windings. This allows us to design a drive system that involves two inverters (Inverter A and Inverter B) feeding machine. Schematic diagram of such a dual inverter drive system has been shown in Fig. 3-2 in terms of space vectors.

Figure 3-2: Schematic diagram of a OEW-PMSM fed by a dual inverter system, represented in terms of space vectors

With reference to Fig. 3-2, it can be noted that machine's stator voltage vector  $\bar{v}_s$  is now given by equation 3.7

$$v_s = \bar{V_A} - \bar{V_B} \tag{3.7}$$

where  $V_A$  and  $V_B$  are the output voltage vectors of inverter A and inverter B respectively. By expressing voltage vectors in terms of d,q components, equation 3.7 can be rewritten as given by equation 3.8 and components can be further decomposed as given by 3.9 and 3.10

$$v_{sd} + jv_{sq} = (V_{Ad} + jV_{Aq}) - (V_{Bd} + jV_{Bq})$$

(3.8)

$$v_{sd} = V_{Ad} - V_{Bd} \tag{3.9}$$

$$v_{sq} = V_{Aq} - V_{Bq} \tag{3.10}$$

This additional consideration on stator voltage vector  $\bar{v}_s$  allows us to express the mathematical model for an OEW-PMSM in terms of same equations 3.1 - 3.5 used to describe a conventional PMSM.

### 3.3 Implementation of OEW-PMSM mathematical model

Even though simulation models for a conventional PMSM are readily available in commonly used simulation platforms such as Matlab/Simulink and PLECS, no built in models are available that facilitate simulation requirements involving open end winding configuration of PMSMs. Therefore, the mathematical model for an OEW-PMSM expressed in d-q reference frame was implemented in Matlab/Simulink.

Figure 3-3 shows the masked view of implemented OEW-PMSM model and its block parameters dialog box. The model was designed to accept d,q components of inverter A and inverter B voltage vectors (VAd, VAq, VBd, VBq) and shaft speed  $(wm_rad/s)$  as inputs and to return d,q components of stator current (Id, Iq), electromechanical torque generated by the machine (Te) and electrical angular position of the rotor (the) as outputs. Block parameters dialog box allows one to specify the parameters of the machine under consideration.

Implemented model under mask is shown in Figure 3-4. Model equations have been implemented mainly with the aid of RL branches, controlled voltage sources, a Matlab function block to perform additional calculations and an integrator block to calculate rotor's electrical angular position. This model can be used to simulate either a conventional PMSM or a PMSM in its OEW configuration. In former case, one has to feed zero for the Inverter B voltage inputs (VBd, VBq).

|   |          | Block Parameters: OEW PMSM X                                                                      |

|---|----------|---------------------------------------------------------------------------------------------------|

|   |          | Subsystem (mask)                                                                                  |

| 6 |          | Implements an Open End Winding Permanent Magnet Synchronous Machine in rotor d,q reference frame. |

|   | wm_rad/s | Parameters                                                                                        |

|   | Те 🕨     | Stator resistance Rs E                                                                            |

| 2 | VAd      | d axis stator inductance Ld                                                                       |

|   | Id 🕨     | q axis stator inductance Lq Lq                                                                    |

| 7 | VAq      | Number of pole pairs p p                                                                          |

|   | lq >     | Permanent magnet flux Fim Fim                                                                     |

| 1 | VBd      | Initial d axis current Id0 0                                                                      |

|   | the >    | Initial q axis current Iq0 0                                                                      |

| 1 | ÷        | Initial d axis position the0 0                                                                    |

|   | OEW PMSM |                                                                                                   |

|   |          | OK Cancel Help Apply                                                                              |

Figure 3-3: Implemented OEW-PMSM Simulink model and its block parameters dialog

Figure 3-4: Masked view of the implemented OEW-PMSM model

### Chapter 4

## Development of Modulation Schemes

As already outlined in this thesis, dual inverter drive topology analyzed in this study is composed of two, two-level inverters. Performance of the dual inverter drive topology is to be compared against a single inverter motor drive based on a three level NPC inverter. Therefore, it is necessary to select and implement appropriate modulation schemes for two level and three level NPC inverter systems.

Modulation schemes provided by Matlab/Simulink and PLECS simulation platforms, were found incapable to cater the simulation requirements under this analysis. Specially, the modulation scheme provided by PLECS software for the three level NPC inverter was found to loose control over DC link voltage balancing under unbalanced and transient conditions. Therefore, modulation schemes for both two level and three level inverter topologies were carefully selected and implemented in Simulink as an initial step of the motor drive design process.

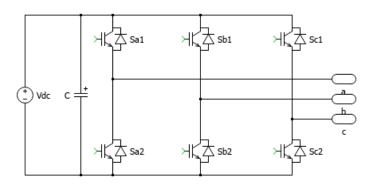

### 4.1 Implementation of SVPWM scheme for two level inverter

Schematic diagram of a typical two level inverter is shown in Figure 4-1. Switches of the inverter, at a given instant, can be either ON or OFF (denoted as 1 and 0 respectively in subsequent notations). However, in order to avoid a short circuit on the DC link, upper and lower switches in the same leg must always operate in complimentary states. This implies that there are only eight possible switching combinations for the inverter that can be written as **OOO**, **POO**, **PPO**, **OPO**, **OPP**, **OOP**, **POP**, **POP**, **PPP** by adopting the convention specified in Table 4.1(three letters in this notation refer to the switching state of a,b,c legs of the inverter, stated in sequential order).

| Switching state | Switch status, Phase $x = a,b,c$ |          |  |

|-----------------|----------------------------------|----------|--|

| Switching state | $S_{x1}$                         | $S_{x2}$ |  |

| Р               | 1                                | 0        |  |

| 0               | 0                                | 1        |  |

Table 4.1: Two level inverter switching states convention

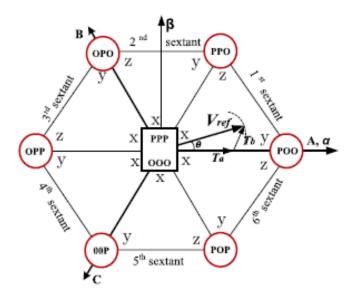

Space vector representation of these voltage vectors (in  $\alpha - \beta$  reference frame) is shown in Figure 4-2. Vectors corresponding to switching states **OOO** and **PPP** are zero in magnitude. Magnitude of the remaining vectors can be shown to be equal to  $\frac{2}{3}V_{DC}$  [36]

Figure 4-1: Schematic representation of a typical two level inverter

Figure 4-2: Space-vector diagram for a two-level inverter

### 4.1.1 Operating principle

In order to generate required voltage waveform out of the inverter using SVPWM principle, firstly, it is necessary to locate the reference voltage vector within the space vector diagram and identify the Nearest Three Vectors (NTV)s surrounding it. Reference vector can then be represented as a vector sum of the NTVs together with appropriate switching times for each of the NTV during a given switching period.

### 4.1.2 Main steps

Implemented SVPWM scheme can be described as a process consisting of three main steps viz. identification of NTVs, NTV duty cycle calculation and determination of switching states.

### 1. Identification of Nearest Three Vectors

Requested a,b,c voltage references are first converted to  $\alpha - \beta$  stationary reference

frame using the Clarke transform given by equation 4.1[36].

$$\begin{pmatrix} V_{\alpha} \\ V_{\beta} \end{pmatrix} = \begin{pmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{pmatrix} \begin{pmatrix} V_{a} \\ V_{b} \\ V_{c} \end{pmatrix}$$

(4.1)

Having calculated  $\alpha$ ,  $\beta$  components, magnitude and phase of the reference voltage vector  $\bar{V}_{ref}$  can easily be obtained. With these information  $\bar{V}_{ref}$  can be written as,

$$\bar{V}_{ref} = \sqrt{V_{\alpha}^2 + V_{\beta}^2} \angle \tan^{-1} \frac{V_{\beta}}{V_{\alpha}}$$

(4.2)

Information on magnitude and angle can be used to exactly locate  $\bar{V}_{ref}$  within the space vector diagram.

#### 2. Calculation of dwelling times

Assuming that NTVs corresponding to  $\bar{V}_{ref}$  located on the space vector diagram are  $v_x, v_y$  and  $v_z$ , reference voltage vector can be synthesized by means of appropriate combinations of the NTVs as given by equation 4.3

$$V_{ref}.T_s = v_x.T_x + v_y.T_y + v_z.T_z$$

(4.3)

where  $T_s$  is the switching period of the inverter (inverse of the switching frequency).  $T_x$ ,  $T_y$  and  $T_z$  refer to the dwelling times for each of the NTV during a switching period. Dwelling time for the three NTVs should add up to the switching period and can be expressed as,

$$T_s = T_x + T_y + T_z \tag{4.4}$$

By considering above relationships and geometric relationships of vector representation in the space vector diagram, following general expressions were derived for dwelling times. x,y,z vectors that correspond to this notation have been indicated for each of the sector in the space vector diagram.

$$T_x = a\sin(S\frac{\pi}{3} - \theta) \tag{4.5}$$

$$T_y = a\sin(\theta - (S-1)\frac{\pi}{3})$$

(4.6)

$$T_z = T_s - (T_x + T_y) (4.7)$$

where S is the sector number (1, 2..., 6) within which  $\bar{V}_{ref}$  is located in. *a* is defined as the modulation index and  $\theta$  is the angle of the  $\bar{V}_{ref}$  given by following expressions.  $V_{DC}$  refers to the DC link voltage of the inverter.

$$a = \sqrt{3} \frac{\sqrt{V_{\alpha}^2 + V_{\beta}^2}}{V_{DC}} \tag{4.8}$$

$$\theta = \tan^{-1} \frac{V_{\beta}}{V_{\alpha}} \tag{4.9}$$

#### 3. Determination of switching states.

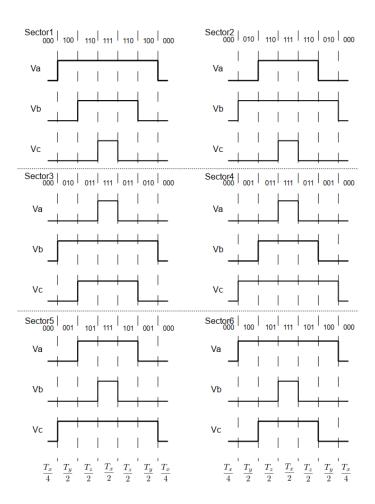

Implemented modulator divides a switching period into seven segments of duration  $\frac{T_x}{4}$ ,  $\frac{T_y}{2}$ ,  $\frac{T_z}{2}$ ,  $\frac{T_x}{2}$ ,  $\frac{T_z}{2}$ ,  $\frac{T_y}{2}$  and  $\frac{T_x}{4}$ . If the reference vector is located in the first sector, for each segment of time, it sequentially assigns the states OOO - POO - PPO - PPP - PPO - POO - OOO. Switching state assignment algorithm for all the cases is given in Appendix B under Figure B-1

### 4.1.3 Implementation of the modulation scheme in Simulink

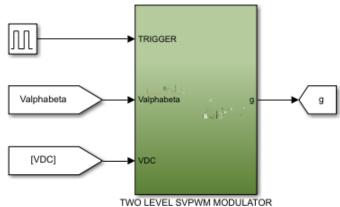

Figure 4-3 shows the two level SVPWM modulator subsystem implemented in Simulink. Modulator receives  $\alpha,\beta$  components of the reference voltage vector  $\bar{V}_{ref}$  and DC link voltage of the inverter as inputs. It includes an additional port that accepts a trigger that is used to synchronize the modulator with the intended switching frequency of the inverter. Modulator outputs the gate pulses that can be used drive a two level inverter.

Figure 4-3: Space Vector Pulse Width Modulator for two level inverter implemented in Simulink

First level internal view of the modulator subsystem in shown in Figure 4-4.

Figure 4-4: First level internal view of the two level Space Vector Pulse Width Modulator

Logical implementations in this level can be divided in to two categories, namely triggered logics and continuous logics. Triggered logics are executed once at the beginning of each switching period and are responsible for sector determination of the reference voltage vector and dwelling time calculations. Triggered logics block returns information related to seven time segments and sector of the reference voltage vector. These information are passed to comparison logics and "State assignment" Matlab script that are collectively responsible for generating the gate pulses. Triggered logics have also been implemented in the form of a Matlab script, and are not shown in this discussion in order to maintain conciseness of the thesis.

### 4.2 Implementation of SVPWM scheme for three level NPC inverter

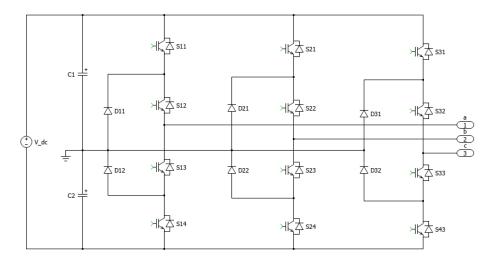

Schematic representation of a typical three level NPC inverter is shown in Figure. 4-5. This topology consists of four power electronic switches and two clamping diodes in each leg, whose connection points are connected to the common connection point of the two DC link capacitors.

Figure 4-5: Schematic representation of a typical three level NPC inverter

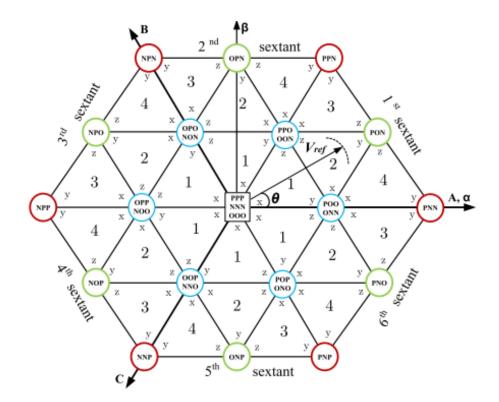

Convention adopted in denoting the switching states is shown in Table 4.2. There are three possible switching states for each leg. Consequently, it results in 27 switching state combinations. Voltage vectors generated by the inverter at these switching states are shown in Figure 4-6 in the form of a space vector diagram. Table 4.3 tabulates the magnitude of each of the vectors, classifying them as null, small, medium

Figure 4-6: Space-vector diagram for three-level NPC inverter

and large vectors.

It is possible to identify that there exist more than one switching state resulting in identical voltage vectors in the space vector diagram, which will be called as "redundant vectors" in subsequent discussion, whose existence serves a useful function in maintaining voltage balance of the two DC link capacitors.

| Switching state | Status of the switches, Phase x(a,b,c) |          |          |          |

|-----------------|----------------------------------------|----------|----------|----------|

|                 | $S_{x1}$                               | $S_{x2}$ | $S_{x3}$ | $S_{x4}$ |

| Р               | 1                                      | 1        | 0        | 0        |

| 0               | 0                                      | 1        | 1        | 0        |

| Ν               | 0                                      | 0        | 1        | 1        |

Table 4.2: Three level NPC inverter switching states convention

| Switching vector combination | Voltage level                       |  |

|------------------------------|-------------------------------------|--|

| PPP,NNN,OOO                  | 0 (Null vectors)                    |  |

| PPO,OON,POO,ONN,POP,ONO,     | $V_{dc}/3$ (Small vectors)          |  |

| OOP,NNO,OPP,NOO,OPO,NON      |                                     |  |

| PON,OPN,NPO,NOP,ONP,PNO      | $V_{dc0/\sqrt{3}}$ (Medium vectors) |  |

| PNN,PPN,NPN,NPP,NNP,PNP      | $2V_{dc}/3$ (Large vectors)         |  |

Table 4.3: Three level NPC inverter different switching combinations

### 4.2.1 Operating principle

Basic concept behind SVPWM strategy on any multi-level inverter, remains unchanged to that applicable for a two level inverter. Similar to the two level SVPWM scheme, it involves identifying NTVs for the reference voltage vector and synthesizing it by means of appropriate NTV and dwelling time combinations.

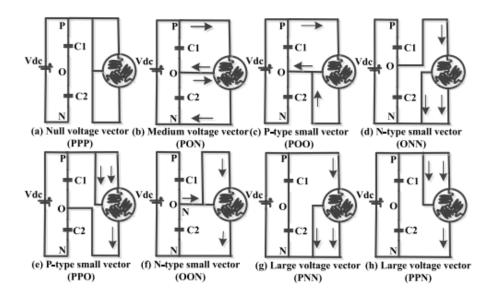

### DC link voltage balancing

DC link voltage balancing is an important concern in multi-level inverters. For a three level NPC inverter, it can be shown that different voltage vectors affect differently on capacitor voltage balancing problem. Figure 4-7 indicates the effect of each of the voltage vectors in sector 1 of the space vector diagram on capacitor voltage balancing.

Figure 4-7: Effects of different voltage vectors on DC-link capacitor voltage

Null (a) and large voltage vectors (g and h) have no effect on the dc-link voltage balancing as they are not connected to the neutral point of the inverter. Therefore, only the small voltage (c, d, e, and f) and medium voltage (b) vectors are mainly responsible for the balancing problem. [12]. In the implemented modulation scheme, this phenomenon is appropriately utilized to select redundant voltage vectors in order to maintain the capacitor voltage balance of the inverter.

### 4.2.2 Main steps

### 1. Identification of Nearest Three Vectors

As clearly identifiable in the given space vector diagram for a three level NPC inverter, each of the six sectors consists of four triangular regions, which will be referred to as "sub-sectors" in subsequent text. (Sub-sectors are numbered 1 to 4 in the given space vector diagram). Therefore, identifying the NTVs at a given point of operation requires a slightly advanced computation methodology compared to the case of two level SVPWM sector identification. In order to facilitate a generalised approach for sub-sector identification, and subsequent NTV determination process, a generalized reference-vector coordinates  $V'_{\alpha}$  and  $V'_{\beta}$  are defined[23] as given by following equations.

$$V'_{\alpha} = |\bar{V}_{ref}| \cos[\theta - (S-1)\frac{\pi}{3}]$$

(4.10)

$$V'_{\beta} = |\bar{V}_{ref}|\sin[\theta - (S-1)\frac{\pi}{3}]$$

(4.11)

Equations follow same notations adopted in the discussion for two level SVPWM scheme. With this treatment, and based on simple geometric relationships on the space vector diagram, logic for sub-sector identification can be formulated as given by following equations;

if

$$V'_{\alpha} < \frac{V_{dc}}{3} - \frac{\sqrt{3}}{3} V'_{\beta}$$

then, Sub-sector = 1 (4.12)

else if

$$V'_{\alpha} > \frac{V_{dc}}{3} + \frac{\sqrt{3}}{3} V'_{\beta}$$

then Sub-sector = 4 (4.13)

else if

$$V'_{\beta} < \frac{\sqrt{3}V_{dc}}{6}$$

then Sub-sector = 2 (4.14)

else Sub-sector

$$= 3$$

(4.15)

### 2. Calculation of dwelling times

Once the NTVs of the reference voltage vector are identified, dwelling times for each of the vector is calculated based on the generalized set of equations given in Table 4.4. x,y,z vectors that correspond to this notation have been indicated for each of the sub-sector in the space vector diagram.

|              | $T_x$                                       | $T_y$                                      | $T_z$                                 |

|--------------|---------------------------------------------|--------------------------------------------|---------------------------------------|

| Sub-sector 1 | $1 - 2a\sin[\theta - (S-2)\frac{\pi}{3}]$   | $2a\sin(S\frac{\pi}{3}-\theta)$            | $2a\sin[\theta - (S-1)\frac{\pi}{3}]$ |

| Sub-sector 2 | $1 - 2a\sin[\theta - (S-1)\frac{\pi}{3}]$   | $-1 + 2a\sin[\theta - (S-2)\frac{\pi}{3}]$ | $1 - 2a\sin(S\frac{\pi}{3} - \theta)$ |

| Sub-sector 3 | $2 - 2a\sin[\theta - (S-2)\frac{\pi}{3}]$   | $-1 + 2a\sin[\theta - (S-1)\frac{\pi}{3}]$ | $2a\sin(S\frac{\pi}{3}-\theta)$       |

| Sub-sector 4 | $2 - 2a\sin[\theta - (S - 2)\frac{\pi}{3}]$ | $-1 + 2a\sin(S\frac{\pi}{3} - \theta)$     | $2a\sin[\theta - (S-1)\frac{\pi}{3}]$ |

Table 4.4: Formulas for NTV dwelling time calculations

#### 3. Determination of switching states

Switching state assignment step in implemented modulator is based on the algorithm presented in [12]. It takes into account the voltage of the upper and lower capacitors of the DC link at the beginning of each switching period to assign the switching states in order to maintain neutral point voltage balance. Adopted state assignment algorithm is given in Appendix A.

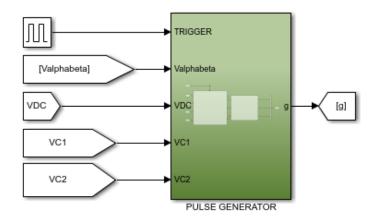

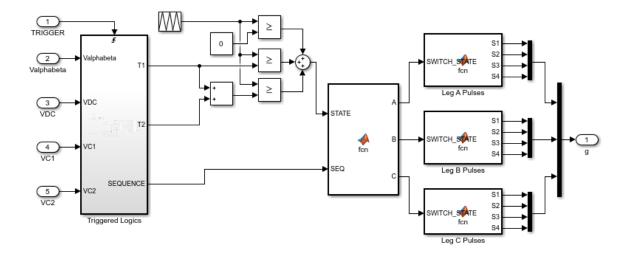

### 4.2.3 Implementation of the modulation scheme in Simulink

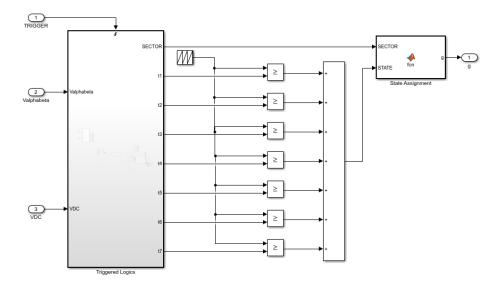

The modulator subsystem implemented in Simulink is shown in Figure 4-8. Figure 4-9 shows the first level internal view of the modulator.

Figure 4-8: Space Vector Pulse Width Modulator for three level NPC inverter implemented in Simulink

Figure 4-9: First level internal view of the three level Space Vector Pulse Width Modulator

Implementation has adopted a similar paradigm to that of the two level SVPWM modulator implementation. However, as evident in the figure, the modulator now accepts instantaneous voltages of DC link capacitors as additional inputs in order to use them as inputs for subsequent switching state assignment logics.

# 4.3 THD analysis of two level and three level NPC inverter voltage waveforms

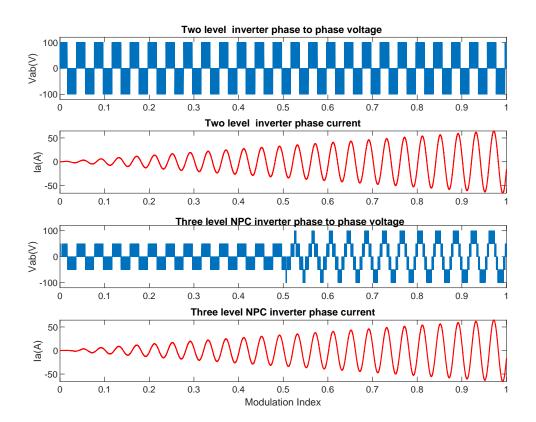

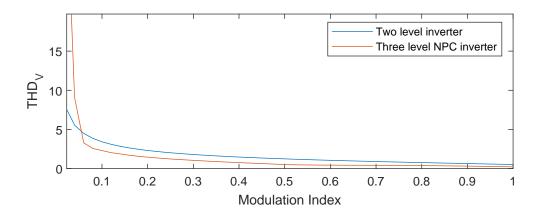

A Total Harmonic Distortion(THD) analysis of phase-to-phase voltage waveforms generated by two level and three level inverters triggered by implemented modulators was conducted. Voltage and current waveforms of the two inverters with the modulation index varying from 0 to 1 is shown in Figure 4-10. Variation of THD of the phase to phase voltages with varying modulation indices under two inverters is shown in Figure 4-11.

Figure 4-10: Phase-to-phase voltages and phase currents with two inverters

It is evident that three level inverter performs well with respect to THD in generated voltage waveform, except at very low modulation indices where it effectively acts as a two level inverter.

Figure 4-11: THD of phase-to-phase voltage waveforms

### Chapter 5

## Control System for Three Level NPC Inverter Drive

This chapter explains the speed control system applicable for the three level inverter drive. It is based on classical Field Oriented Control (FOC) scheme used to control SPMSMs. FOC system in this context assumes that the d axis is aligned on the direction of permanent magnet flux of the rotor.

### 5.1 Design specifications

Parameters of the SPMSM given in Table 1.1 were used to design the three level NPC inverter based speed control system. DC link voltage of the three level NPC inverter  $(E_A)$  was considered as 80V.

### 5.1.1 Voltage and current constraints

Operating limits of the speed control system are constrained by voltage and current limits offered by the machine and the inverter.

Maximum permissible current  $I_{s,max}$  which can be the nominal thermal current of he machine at steady state or the the nominal current of inverters in transient overload conditions, limits the torque capability of the motor drive.[6] In this design,  $I_{s,max}$  is taken as 13A which is the rated current of the machine. Therefore steady state stator current vector  $\bar{i_s}$  has to be limited within its maximum limit as given by equation 5.1

$$|\bar{i}_s| \le I_{s,max} \tag{5.1}$$

Above the based speed, machine behaviour is also constrained by the available DC link voltage of the inverter, i.e,

$$|\bar{V}_A| \le V_{A,max} \tag{5.2}$$

where  $V_{max}$  is the maximum voltage that can be generated by the three level NPC inverter, which depends on the modulation strategy. In this study, the inverter is based on SVPWM. Therefore, maximum voltage that can be generated in the linear operating range is:

$$V_{A,max} = \frac{E_A}{\sqrt{3}} \tag{5.3}$$

### 5.2 Control scheme

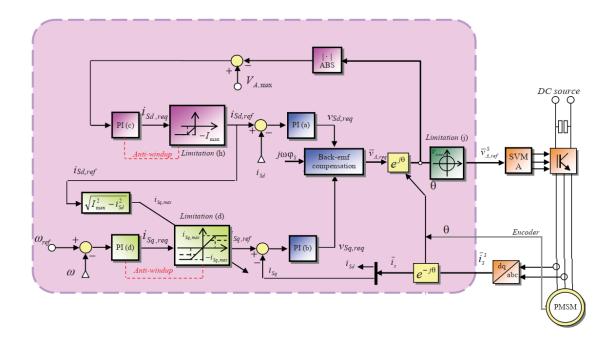

Control scheme adopted in this design for driving the SPMSM shown in Fig.5-1.

It consists of inner control loops that are responsible for controlling d,q components of stator current and outer control loops that generate corresponding current references.

### 5.2.1 Inner control loops

PI regulators (a) and (b) in inner control loops are responsible for controlling stator currents. Inputs to these two controllers are respective current errors and they output  $V_{d,ref}^*$ ,  $V_{q,ref}^*$  components of voltage reference for the inverter  $(\bar{V}_{ref}^*)$ . Feed-forward

Figure 5-1: Speed control system for the SPMSM based on a three level NPC inverter drive

terms resulting from back-emf terms are added to the output of these controllers in order to improve transient performance of the control system.

$\bar{V}_{ref}^*$  is limited to  $V_{A,max}$  within the d-q control axis system by employing a saturation logic and voltage reference  $\bar{V}^s *_{ref}$  is sent as an input to the modulation scheme of the inverter to generate requested reference voltage at machine's stator terminals.

By neglecting the terms  $-\omega\varphi_{sq}$  and  $\omega\varphi_{sd}$  in equation 3.1 and 3.2 respectively and considering the fact that  $L_d = L_q = L_s$  for our machine, one can observe that Laplace transform on equations results in identical plant transfer functions for both id and iq in a control perspective. Common plant transfer function applicable for both PI regulators (a) and (b) can be written as given in equation 5.4

$$P_i(S) = \frac{i_s(S)}{v(S)} = \frac{1}{R_s + SL_s}$$

(5.4)

Regulators were tuned by considering the closed loop transfer function involving a PI controller with a natural frequency( $\omega_n$ ) of 200Hz and a damping factor  $\zeta$  0.75 for the closed loop current response.

### 5.2.2 Outer control loops

PI controller (c) generates the reference for d axis current component  $i_{sd}*$ . Input to the controller is the difference between  $V_{A,max}$  and magnitude of  $V_{ref}^*$ . Output of the regulator is limited between  $I_{s,max}$  and 0. Saturation feedback is used as an input to the regulator to avoid integrator wind-up.

PI regulator (d) takes care of issuing reference for the q component of stator current  $i_{sq}*$ . It receives speed error  $(\omega_m^* - \omega_m)$  as the input. Output of the regulator is limited between  $\pm I_{q,avail}$  that is given by,

$$\pm I_{q,avail} = \sqrt{I_{s,max}^2 - i_{sd}^2 *}$$

(5.5)

Saturation feedback is employed as an input to the controller in order to avoid overshoots in th speed response due to integrator wind-up.

PI control parameters for the speed regulator in this design were obtained by considering a natural frequency ( $\omega_n$ ) of 6Hz and a damping factor  $\zeta$  0.70

### 5.2.3 Concept of Maximum Torque Per Amp - (MTPA) for SPMSM

Mathematical expression for the electromagnetic torque generated by a PMSM was already introduced in Chapter 3 under equation 3.5. The first term in the equation  $(\varphi_e i_{sq})$  is termed as magnet alignment torque and the second term that is proportional to  $(L_d - L_q)$  is termed as reluctance torque. [37] SPMPMs are characterized by equal values for  $L_d$  and  $L_q$ . Therefore, for the case of a SPMSM, equation 3.5 can be simplified and rewritten as given by equation 5.6.

$$T = \frac{3}{2}p(\varphi_e i_{sq}) \tag{5.6}$$

This implies that maximum torque per unit of stator current is generated when d component of stator current is maintained at zero as long as the machine does not require flux weakening control in order to maintain stator voltage vector below permissible maximum limit.

### Chapter 6

## Control System for Dual Inverter Drive with a Floating Capacitor Bridge

This chapter explains the control system adopted for the control of the dual inverter drive with a floating capacitor bridge. It is based on the control scheme published in [6].

### 6.1 Design specifications

The control system explained in this chapter will be implemented for the SPMSM whose specifications are given in Table 1.1. Figure 6-1 shows how two level inverters, (inverter A and inverter B) are interfaced with the SPMSM in its open end winding configuration.

In Figure 6-1, DC link voltages of inverter A and inverter B have been denoted by  $E_A$  and  $E_B$  respectively.  $\bar{v}_A$ ,  $\bar{v}_B$  and  $\bar{v}_S$  indicate voltage vectors of inverter A, inverter B and the stator of the SPMSM respectively.  $\bar{i}_s$  represents the stator current vector. Table 6.1 tabulates the values for fixed  $E_A$ , upper limit considered for  $E_B$  and capacitance(C) of the DC link capacitor associated with the inverter B.

Figure 6-1: Schematic diagram of the OEW-SPMSM fed by inverter A and inverter B with a floating capacitor

| Parameter Symbol | Value      |

|------------------|------------|

| $E_A$            | 80V        |

| $E_{B,max}$      | 160V       |

| С                | $160\mu F$ |

Table 6.1: Dual inverter drive design specifications

### 6.1.1 Voltage and current constraints

Maximum stator current  $I_{s,max}$  has to be limited to 13A similar to the case of single inverter based motor drive. Control system must also ensure that the voltage requests commanded to inverter A and inverter B are within their maximum limits.i.e.

$$|\bar{V}_A| \le V_{A,max} \text{ and } |\bar{V}_B| \le V_{B,max}$$

$$(6.1)$$

Upper limits for voltages can be stated as in equation 6.2 considering the SVPWM scheme adopted for the inverters in this design.

$$V_{A,max} = \frac{E_A}{\sqrt{3}}$$

and  $V_{B,max} = \frac{E_B}{\sqrt{3}}$  (6.2)

### 6.2 Control Scheme

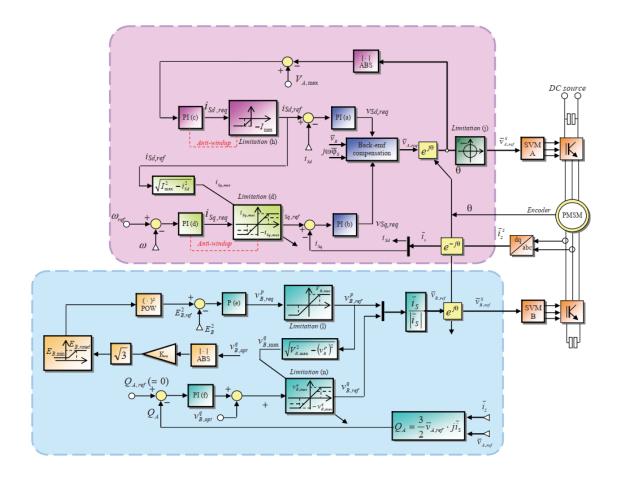

Overall control scheme for the OEW-PMSM fed by the dual inverter system is shown in Figure 6-2. It consists of two sub control systems. Subsystem in pink background deals with the control of inverter A whereas that in light blue background is responsible for controlling inverter B, which involves the floating capacitor.

Figure 6-2: Block diagram of the control scheme for the OEW-PMSM fed by the dual inverter system.

### 6.2.1 Control of inverter A

Purpose of the controls implemented for the inverter A that is connected to the external power supply from which the system receives real power, can be considered to be very much similar to the objectives of the FOC system implemented for the inverter in the case of a single inverter based motor drive. Main objective of this sub-control system is to control the speed of the machine at the set-point commanded by the user via control of stator currents.

#### Relationship between voltage vectors

With reference to Figure 6-1 and based on Kirchhoff's voltage law, relationship between voltage vectors of the inverters and that of the machine can be written as in equation 6.3

$$\bar{v_s} = \bar{v_A} - \bar{v_B} \tag{6.3}$$

This relationship implies the ability to boost the stator voltage of the machine by appropriate manipulation of inverter A and B voltage vectors. This is one of the key benefits of the dual inverter topology over the single inverter drive design considered in previous chapter.

In a control point of view for the inverter A, equation 6.3 indicates that, by adding inverter B voltage vector  $\bar{v}_B$  as a compensation term at the end of the current controllers' control action, it is possible to maintain plant equations for the d,q current control of the inverter A unchanged compared to the single inverter based control system investigated in previous chapter. With this modification, same control parameters calculated for current, speed and flux controllers in single inverter based drive design can be used for the controllers associated with inverter A of the dual inverter drive.

### Control of flux, speed and stator current

As indicated in the pink area of the control system shown in Figure 6-2, control scheme for inverter A involves PI controllers (a) and (b) in the inner control loops for controlling d,q components of stator currents and associated outer PI controllers (c) and (d) that generate corresponding current references. Apart from the additional  $v_B$  compensation added after the control action of PI controllers (a) and (b), overall architecture of the control system and design considerations are similar to the case of the control system design presented in previous chapter. Notations similar to the control system for single inverter drive given in Figure 5-1 have been adopted in this figure considering the ease of cross reference between the two cases for the reader.

### 6.2.2 Control of inverter B

Control systems implemented for inverter B serves two purposes. Firstly, it involves controls for controlling the DC link voltage of the floating capacitor of inverter B ( $E_B$ ).  $E_B$  can either be maintained at a fixed reference value of  $E_{B,max}$  at the expense of increased switching losses associated with the inverter B or it can be varied depending on operating point of the machine in an attempt to minimize the losses associated with the inverter B. Control system adopted in this study is based on the latter option where DC link voltage reference will be varied depending on the operating point of the machine.

Secondly, it attempts to compensate reactive power of the inverter A by injecting or absorbing reactive power from the system. This function allows the inverter A to maximize transferable active power to the PMSM in compliance with the voltage and current constraints of the drive.

#### Selection of control reference frame

Contrary to the inverter A controls, controls for the inverter B are implemented in a reference frame synchronous with the stator current space vector  $i_s$ . As outlined in subsequent sections, mathematical formulations based on such a reference frame facilitate development of independent control loops for inverter B for reactive power control and floating capacitor voltage control.

#### Principle of floating capacitor voltage control

In a reference frame synchronous to the stator current vector, output voltage vector of inverter B, can be expressed as in equation 6.4,

$$\bar{v_B} = (v_{B,par} + jv_{B,quad}) \frac{\bar{i_s}}{|\bar{i_s}|}$$

(6.4)

where  $v_{B,par}$  and  $v_{B,quad}$  respectively, are the parallel and orthogonal components of  $\bar{v_B}$  with respect to  $\bar{i_s}$

By neglecting losses of the inverter B, instantaneous active power exchanged by

the inverter B should be equal to the rate of change of electromagnetic energy stored in the floating capacitor C. This relationship can be mathematically expressed by equation 6.5

$$\frac{d}{dt}(\frac{1}{2}CE_B^2) = \frac{3}{2}\bar{i_s}.\bar{v_B}$$

(6.5)

"." in this context refers to the dot product meaning the sum of the products of corresponding d and q components of the first and second vector.

Now, in a reference frame synchronous to  $\bar{i_s}$ , one can deduce that equation 6.6 can be rewritten as given by following equation

$$\frac{d}{dt}(\frac{1}{2}CE_B^2) = \frac{3}{2}|\bar{i_s}|v_{B,par}$$

(6.6)

This leads to an interesting observation that the electromagnetic energy stored in the floating capacitor (and its voltage) is completely independent of  $v_{B,quad}$  and depends solely on the parallel component  $v_{B,par}$  with respect to  $\bar{i_s}$ . Furthermore, it implies that  $v_{B,par}$  should be zero in steady state operation of the drive.

### Principle of reactive power control

Expression for the reactive power injected by the inverter A  $(Q_A)$ , can be expressed as in equation 6.7, where  $Q_S$  and  $Q_B$  denote reactive power of the PMSM and the inverter B respectively.

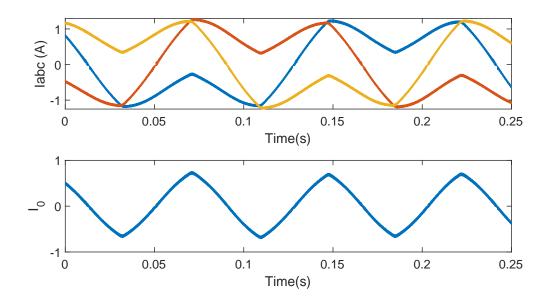

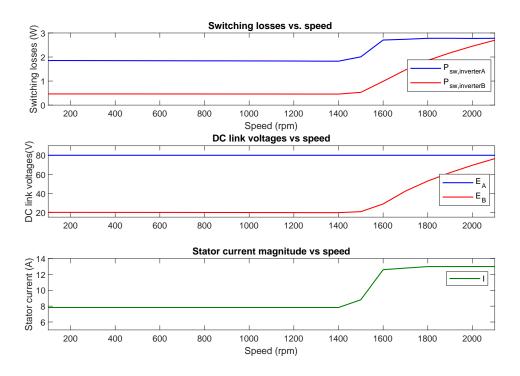

$$Q_A = \frac{3}{2} v_A (j\bar{i_s}) = Q_S + Q_B \tag{6.7}$$