# UNIVERSITY OF OVIEDO

# DESIGN AND DEVELOPMENT OF 20KW BIDIRECTIONAL DC-DC CONVERTER USING SILICON CARBIDE TECHNOLOGY

by

# **Abduselam Hamid Beshir**

(email: abduselam91@gmail.com)

Thesis submitted in partial fulfilment of the requirements for Erusmus Mundus joint Master's degree in sustainable transportation and Electrical power system

at

The University of Oviedo

Department of Electrical, Electronic, Computer and Systems Engineering

August, 2019

| Main Advisor: Fernando Briz              |                                 |

|------------------------------------------|---------------------------------|

| Full professor                           | Signature                       |

| Department of Electrical, Electronic, Co | omputer and Systems Engineering |

| University of Oviedo, Gijon, Spain       |                                 |

| Co – Advisor: Carlos Martinez de Guerenu |                                 |

| Director of R&D Department               | Signature                       |

| Zigor Corporation, Vitoria Gasteiz, Spa  | ain                             |

#### **ABSTRACT**

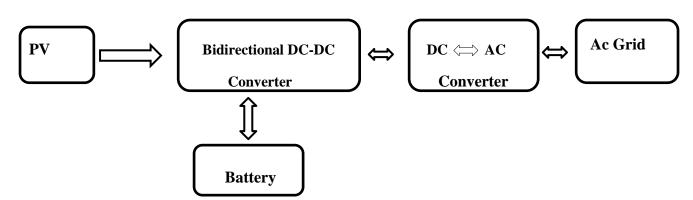

This Master's thesis presents the design and prototype development of a 20KW Bidirectional DC-DC converter using silicon Carbide MOSFETs. The first part of this thesis presents the theoretical background of SiC material and SiC MOSFETs. This is followed by general theory on Bidirectional DC-DC converters. Subsequently the step by step procedures and design consideration of Power stage, Driver circuit and the Control system of the Bidirectional DC-DC converter is discussed briefly. In power stage design, Silicon carbide MOSFETs from different manufacturers (WOLFSPEED and UNITED SILICON CARBIDE) are compared. Moreover the details of selection and sizing of SiC MOSFETs, capacitors, resistors, inductors and the heatsink is presented in detail. The gate driver circuit is appropriately designed so that the Bidirectional DC-DC converter can work for both UF3C120040K4S, United Silicon Carbide MOSFETs and C3M003090K, Wolfspeed Cree third generation SiC MOSFETs. In addition to this Average Current Control technique is used for controlling the inductor current. The schematics and PCB of the DC-DC converter has been made using Cadstar Software. Moreover the components are mounted properly and prototype is developed. The Bidirectional DC-DC converter is tested for operation. Firstly a laboratory circuit enabling double-pulse test is built and the switching behaviour of UF3C120040K4S and C3M003090K SiC MOSFETs are analysed. Next to this the Bidirectional DC-DC converter is tested for BOOST and BUCK operation. Finally results from software simulation and laboratory experiment are presented in detail.

# **ACKNOWLEDGMENT**

First I would like to express my sincere gratitude towards my main Supervisor Prof. Fernando Briz for his advice and guidance. Next I would like to use this opportunity to thank Mr. Carlos Martinez de Guerenu. It is really once a life time opportunity to work with him and I really appreciate his attitude, guidance and support. He has constantly encouraged and supported me from the beginning of the project to the end. His observations and comments helped me to establish the overall direction of the research and to move forward with investigation in depth. He helped me a lot and been a source of knowledge.

I would like to thank Jose Felix and Jose Antonio for their help on the Schematics and PCB design. I would like to take this opportunity also to thank all the R&D department members at Zigor Corporation Eneko, Jorge, Alvaro, Sebastian, Asier, Sergio, Feliciano, Igor and Giorgio for their love, support and encouragement.

Lastly I would like to thank all the administrative and technical staffs at Zigor Corporation for their support and guidance.

# **DEDICATION**

To

My beloved Wife Sumeya Mahmoud Teyib

And

My Grandmother **Temima Mehdi Helifa**

# CONTENTS

| ABSTRACT                                                              | i   |

|-----------------------------------------------------------------------|-----|

| ACKNOWLEDGMENT                                                        | ii  |

| DEDICATION                                                            | iii |

| ABBREVIATIONS                                                         | ix  |

| CHAPTER ONE                                                           | 1   |

| 1. INTRODUCTION                                                       | 1   |

| 1.1 Background                                                        | 1   |

| 1.2 Objectives and Deliverables                                       | 2   |

| 1.3 Structure of the Report                                           | 3   |

| CHAPTER 2                                                             | 4   |

| 2. STATE OF THE ART OF SIC MOSFETs AND BIDIRECTIONAL DC-DC CONVERTERS | 4   |

| 2.1 Silicon Carbide semiconductor                                     | 4   |

| 2.1.1 Material properties and advantages                              | 4   |

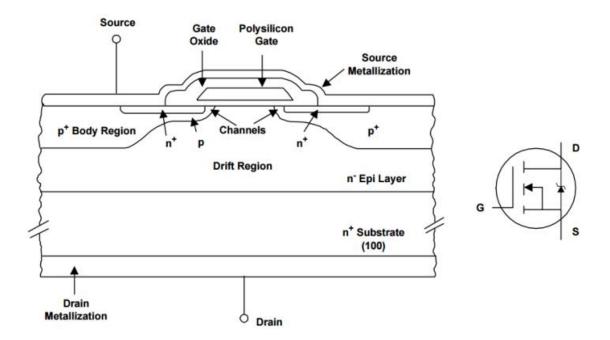

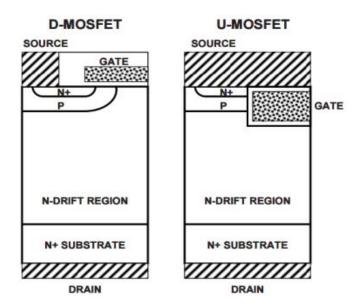

| 2.2 Basic Structure Of SiC MOSFETs                                    | 5   |

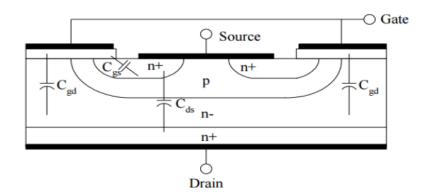

| 2.2.1 SiC MOSFET Parasitic Capacitance                                | 6   |

| 2.3 Characteristics of SiC MOSFETS                                    | 8   |

| 2.3.1 Gate driver voltage Vgs and Rdson                               | 8   |

| 2.3.2 Vds-Id characteristics                                          | 9   |

| 2.3.3 SiC MOSFET Switching Characteristics                            | 11  |

| 2.3.3.1Turn-On Switching Characteristics                              | 11  |

| 2.3.3.2 Turn-Off Switching Characteristics                            | 12  |

| 2.3.3.3 Switching and conduction loss of SiC MOSFET                   | 12  |

| 2.4. Bidirectional DC-DC converters                                   | 15  |

| 2.4.1 Non-isolated BDC                                                | 15  |

| 2.4.2 Isolated BDC (IBDC)                                             | 16  |

| 2.5 Summary                                                           | 18  |

| CHAPTER THREE                                                         | 19  |

| 3. CONVERTER DESIGN METHODOLOGY                                       | 19  |

| 3.1 Power Circuit Design Steps                                        | 19  |

| 3.2 Heat Sink Design                                                  | 20  |

| 3.3 Driver circuit design steps and considerations                    | 21  |

| 3.3.1 Wide range of Gate voltages                                     | 22  |

| 3.3.2 Output current Requirement                                                      | 23  |

|---------------------------------------------------------------------------------------|-----|

| 3.3.3 Input-Output Delay Time                                                         | 23  |

| 3.3.4 Other considerations                                                            | 23  |

| 3.4 Control system design                                                             | 24  |

| 3.4.1 Voltage mode control (VMC)                                                      | 24  |

| 3.4.2 Current mode control (CMC)                                                      | 24  |

| 3.4.2.1 Peak Current Mode Control                                                     | 25  |

| 3.4.2.2 Average Current Mode Control                                                  | 26  |

| 3.4.3 MOSFET Dead Time                                                                | 26  |

| 3.5 PCB design considerations                                                         | 27  |

| CHAPTER FOUR                                                                          | 29  |

| 4. CASE –STUDY                                                                        | 29  |

| 4.1 Power circuit Design                                                              | 29  |

| 4.1.1 Choosing SiC MOSFETs                                                            | 29  |

| 4.1.2. Selecting Switching frequency, the required inductor, Capacitors and Heat sink | .30 |

| 4.2 Driver circuit design                                                             | 33  |

| 4.3. Control circuit design                                                           | 35  |

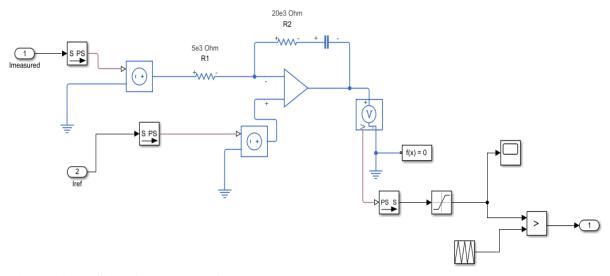

| 4.3.1 Current loop design                                                             | 35  |

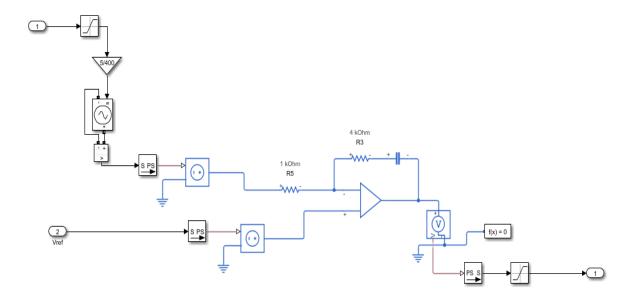

| 4.3.2 Voltage loop Design                                                             | 36  |

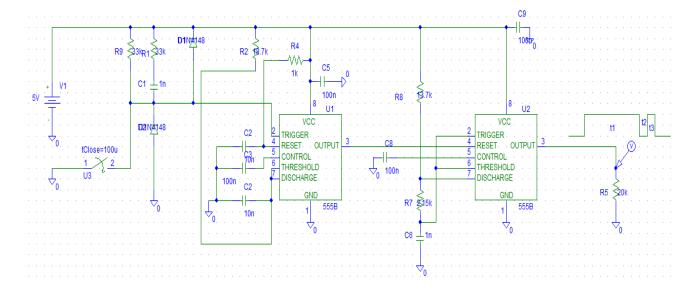

| 4.3.3 Dead time circuit                                                               | 37  |

| 4.4. PCB design                                                                       | 37  |

| 4.5 Double pulse test Set Up                                                          | 38  |

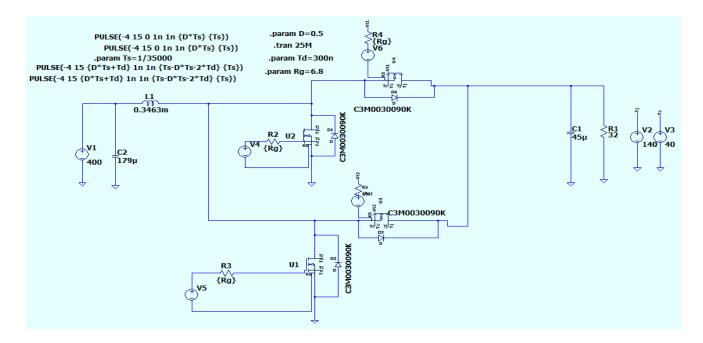

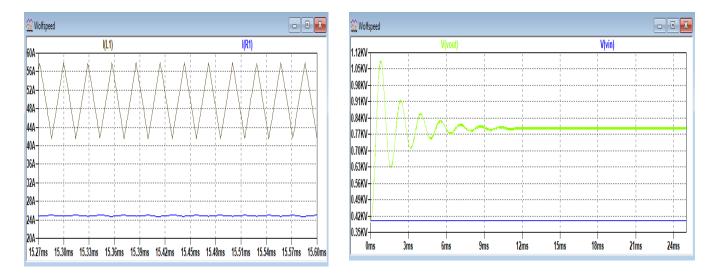

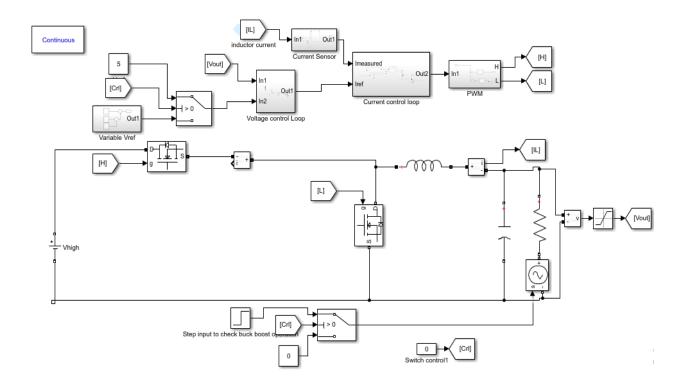

| 4.6. Software simulation                                                              | 43  |

| 4.7 Summary                                                                           | 48  |

| CHAPTER 5                                                                             | 49  |

| 5. RESULT AND DISCUSSION                                                              | 49  |

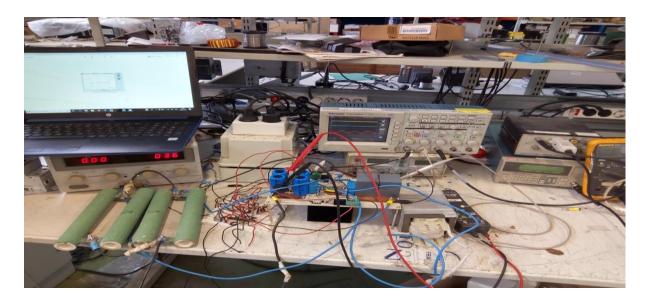

| 5.1 Measuring Instruments                                                             | 49  |

| 5.2 Power supplies                                                                    | 49  |

| 5.3 Testing the Gate driver Circuit                                                   | 50  |

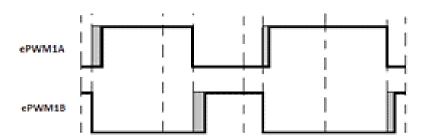

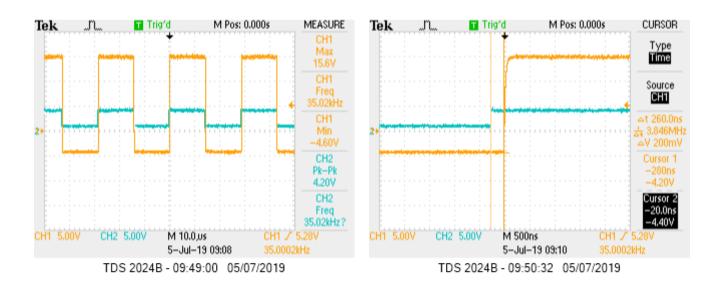

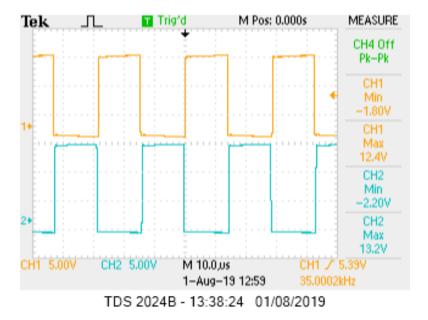

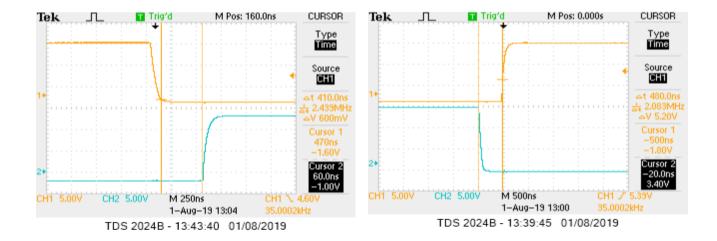

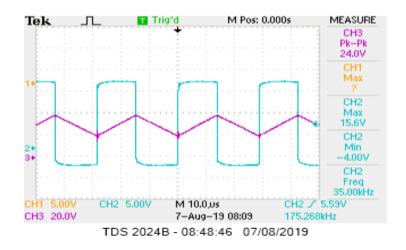

| 5.4 Testing the dead time Generating Circuit                                          | 51  |

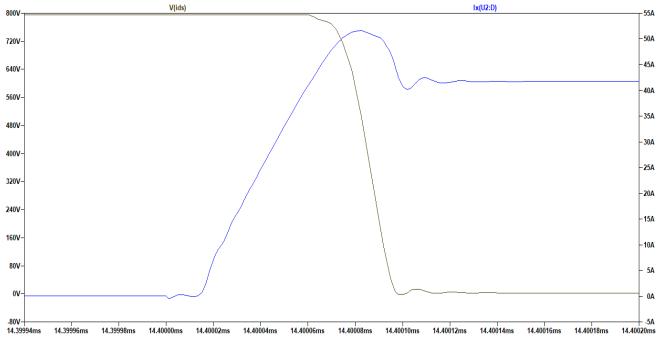

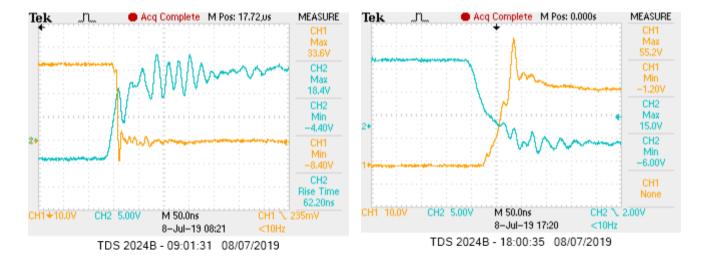

| 5.5 Double Pulse Test                                                                 | 53  |

| 5.6 Testing the operation of the DC-DC converter                                      | 57  |

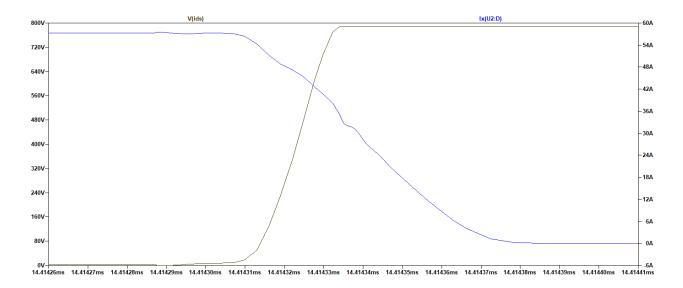

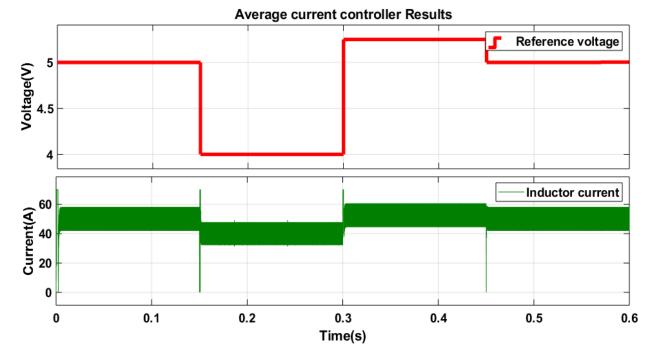

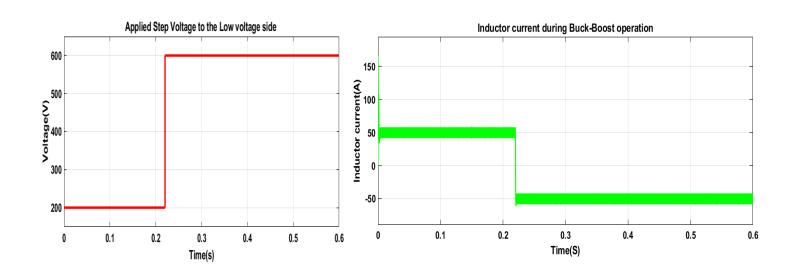

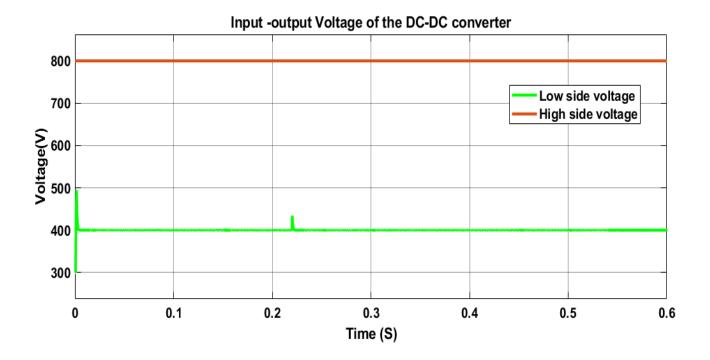

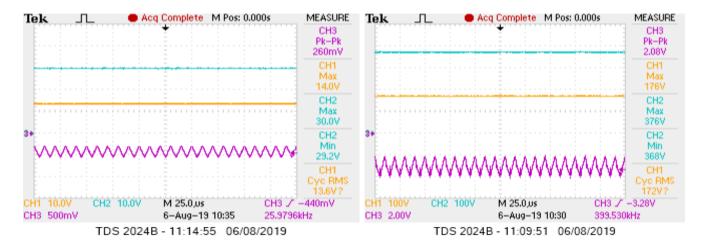

| 5.6.1 Boost Operation                                                                 | 57  |

|                                                                                       |     |

| 5.6.2 Buck Operation          | 58 |

|-------------------------------|----|

| CHAPTER 6                     | 60 |

| 6. CONCLUSION AND FUTURE WORK | 60 |

| 6.1 Conclusion                | 60 |

| 6.2 Future Work               | 60 |

| REFERENCES                    | 62 |

# LIST OF TABLES

| Table 2. 1 Main properties of Si and SiC[27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

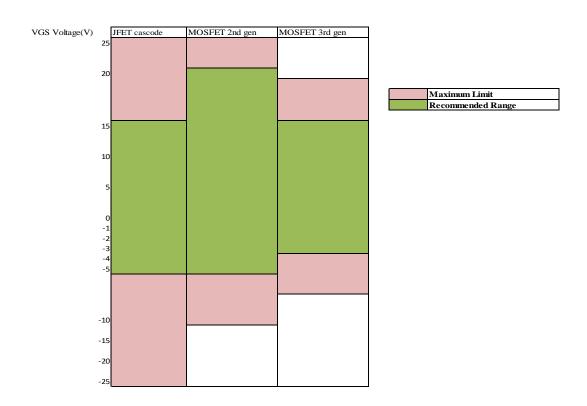

| Table 3. 1 Gate to source voltage limits for different SiC MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23     |

| Table 4.1 Comparison of switching energy loses for Different types of SiCMOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30     |

| Table 4. 2 Size of inductor for various frequencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30     |

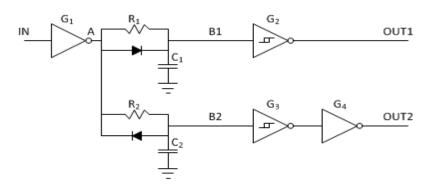

| Table 4.3 Double pulse generator circuit reference values of resistors and capacitors for required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | d time |

| values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

| Figure 2. 1 Basic structure of the n-channel DMOS MOSFET[27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| Figure 2. 2 Power MOSFET structures[27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| Figure 2.3 Intrinsic capacitance in the n-channel DMOS MOSFET [27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

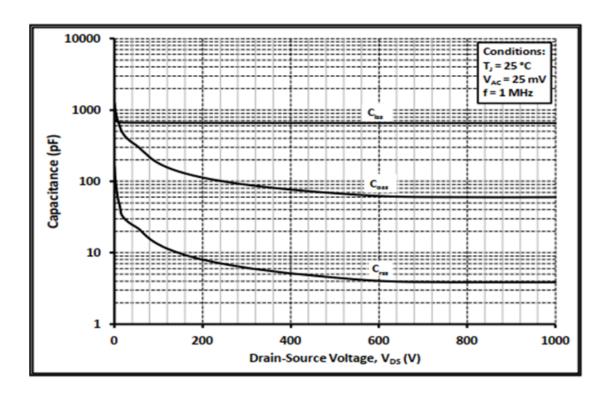

| Figure 2.4 Capacitance Vs Drain to source voltage Vds Cree C3M0065100K Silicon Carbide Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

| MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

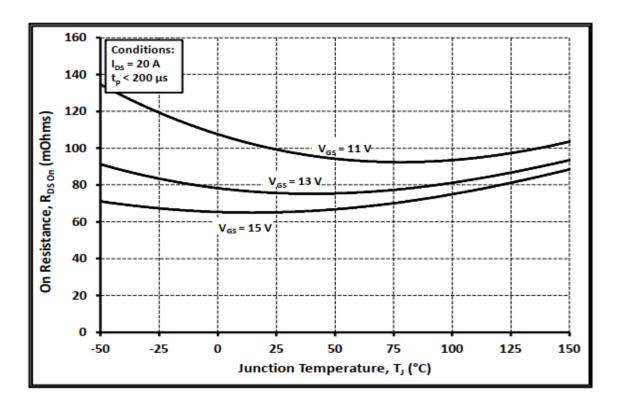

| Figure 2.5 on resistance Vs. Temperature for various Gate Voltage of Cree C3M0065100K Silico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| Carbide Power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

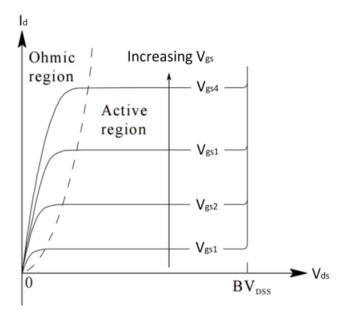

| Figure 2.6 I-V characteristics of SiC MOSFET [27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

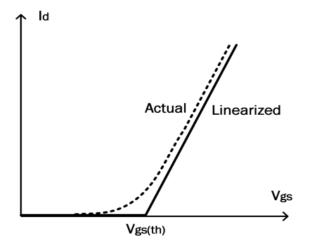

| Figure 2.7 Gate-to-Source voltage transfer characteristics[27]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

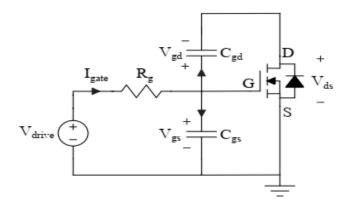

| Figure 2. 8 MOSFET gate charging and discharging equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

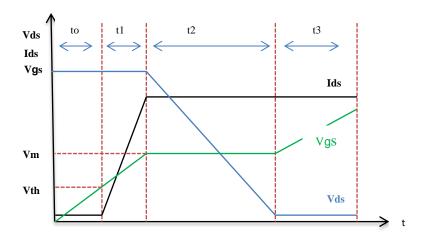

| Figure 2. 9 Turn -on switching characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

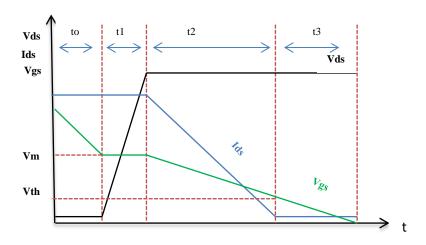

| Figure 2. 10 Turn –off switching characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

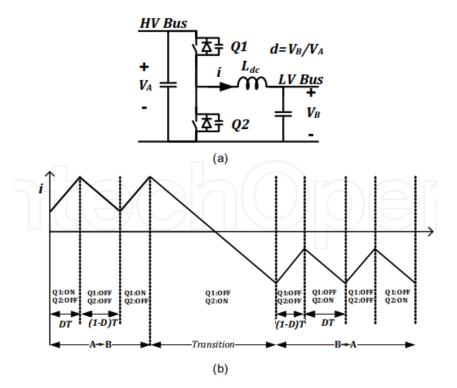

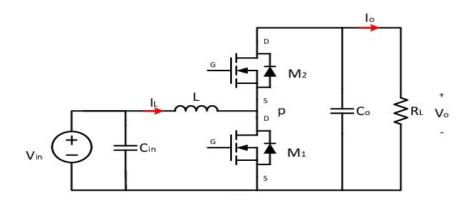

| Figure 2. 11 (a) Basic NBDC (b) operating waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

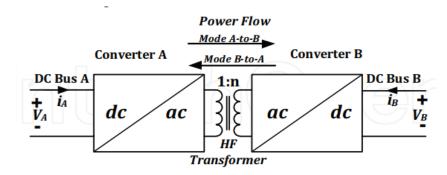

| Figure 2.12 Basic structure of IBDC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

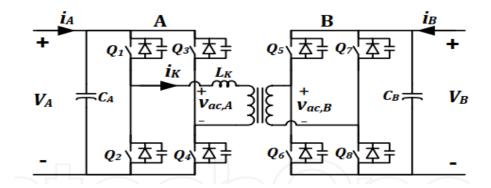

| Figure 2. 13 Dual Bridge Isolated Voltage Fed Bidirectional DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| Figure 3. 1 Bi directional Boost Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

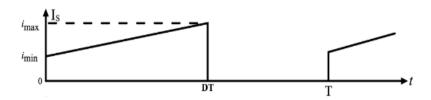

| Figure 3. 2 MOSFET current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

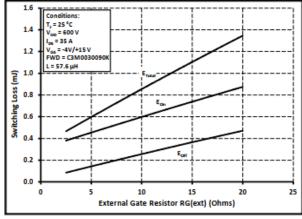

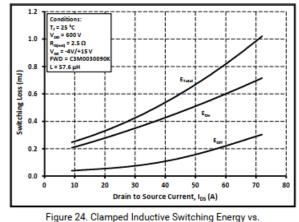

| Figure 3. 3 (a) switching energy vs.External gate resistor (b) switching energy vs drain current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

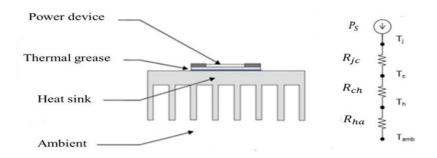

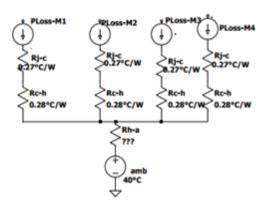

| Figure 3.4 Diagram of (a)cross-section of SiC device on heat sink and (b) thermal model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

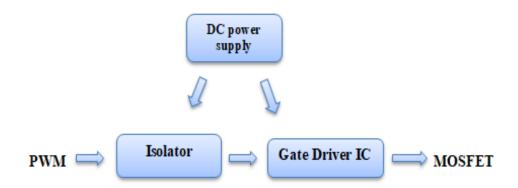

| Figure 3.5 Components of gate driver circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

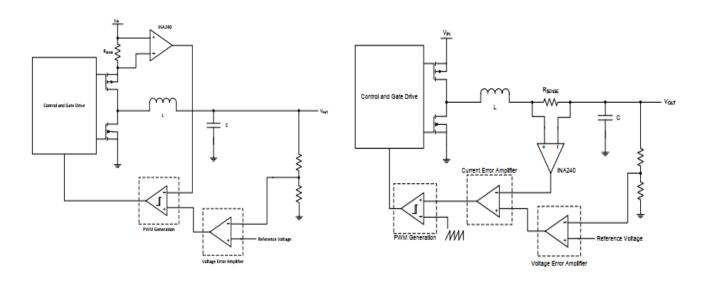

| Figure 3. 6 (a) Peak current control scheme (b) average current control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

| Figure 4.1 Designed inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| Figure 4.2 Heat sink thermal equivalent circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

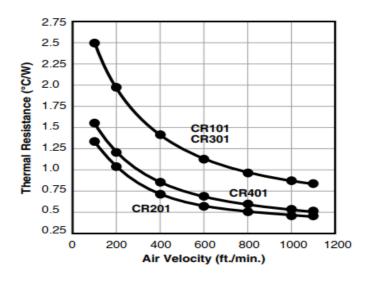

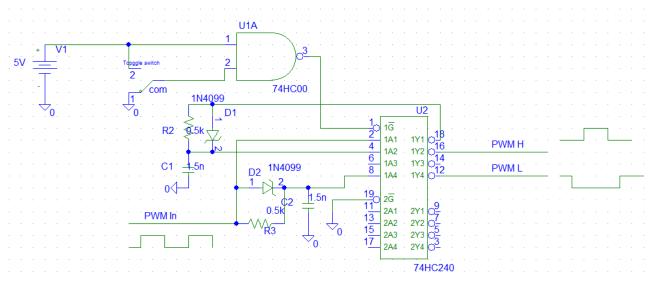

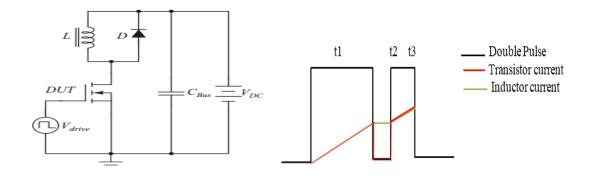

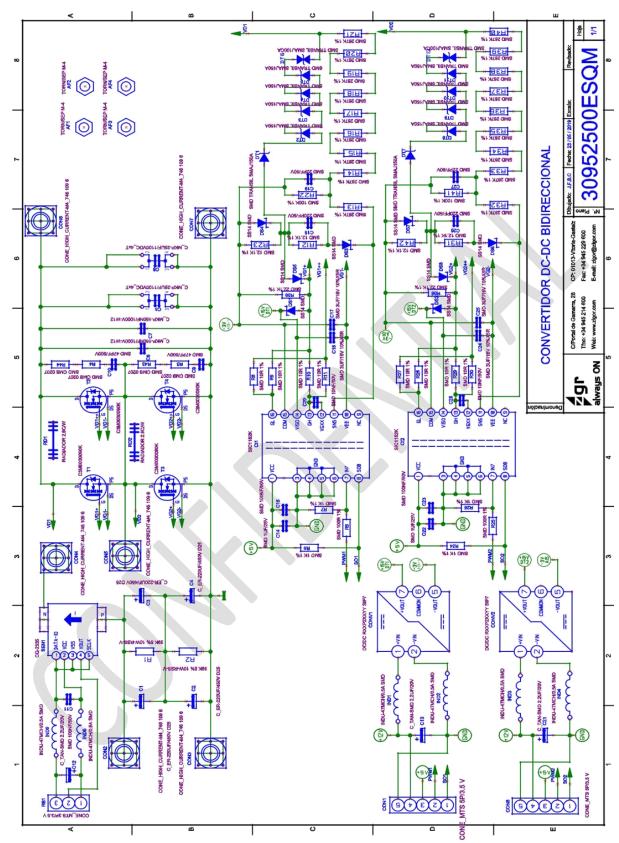

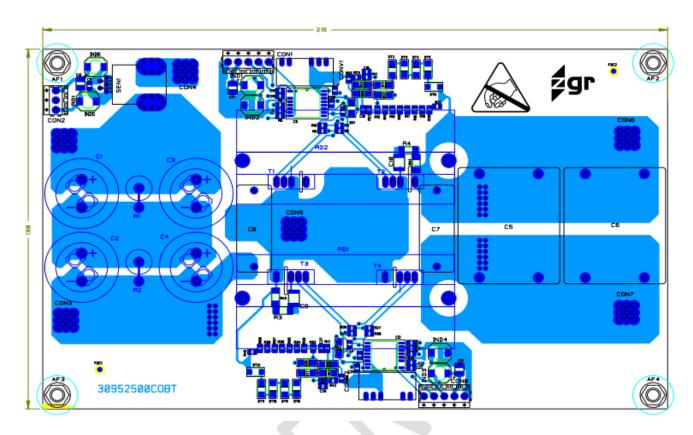

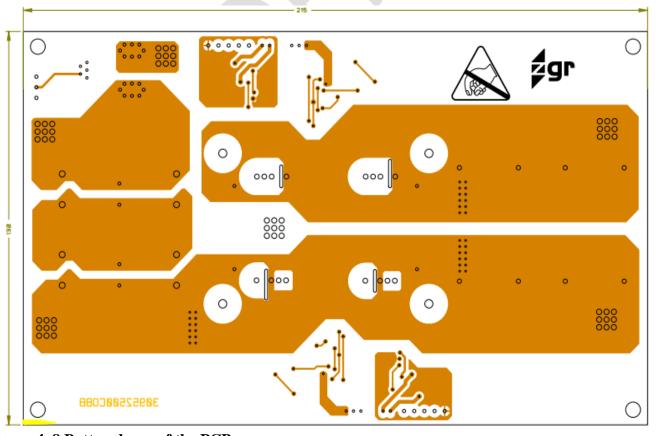

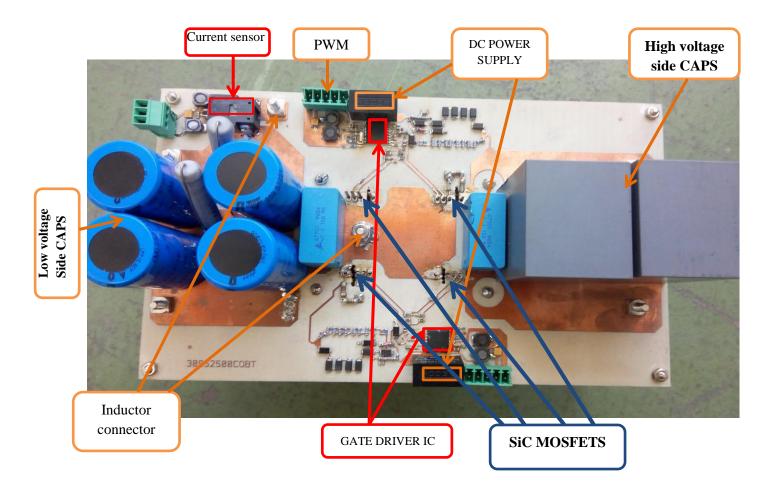

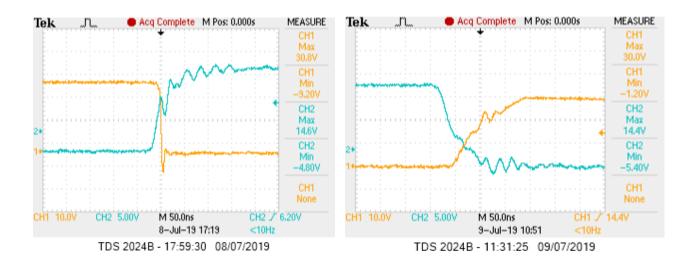

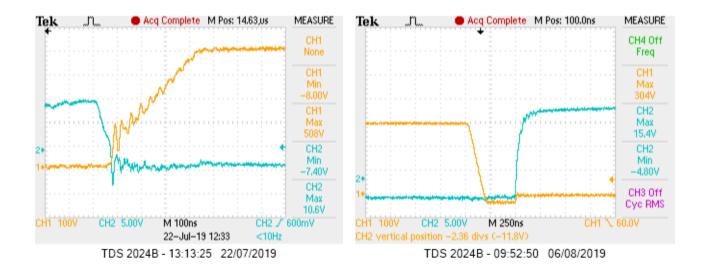

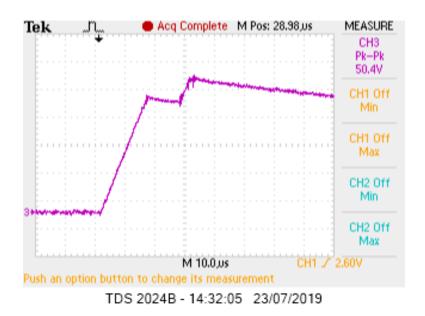

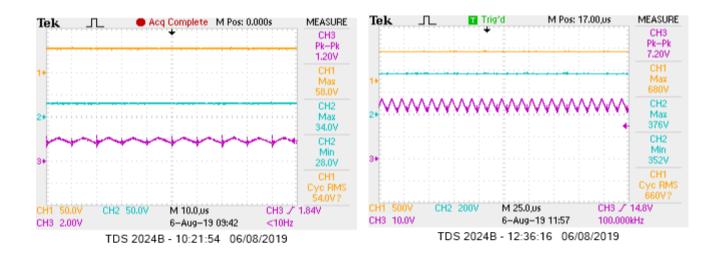

| Figure 4.3 Thermal Resistance Curve of CR Series Heat sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |