### UNIVERSITY OF OVIEDO Department of Electrical Engineering

Ph.D. Programme in Energy and Process Control

## Ph.D. THESIS DISSERTATION

## Topologies and Control Strategies of Multiport Modular Multilevel Converters

Mario López Medina

December 2018

#### UNIVERSIDAD DE OVIEDO

Departamento de Ingeniería Eléctrica, Electrónica, de Computadores y Sistemas

Programa de Doctorado en Energía y Control de Procesos

## TESIS DOCTORAL

## Topologías y Estrategias de Control de Convertidores Modulares Multinivel Multipuerto

Mario López Medina

Diciembre 2018

#### UNIVERSITY OF OVIEDO

Department of Electrical Engineering Ph.D. Programme in Energy and Process Control

### Ph.D. THESIS DISSERTATION

### Topologies and Control Strategies of Multiport Modular Multilevel Converters

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at the University of Oviedo

Mario López Medina

Supervisors: Dr. Fernando Briz Dr. Juan Manuel Guerrero

**Electrical Engineering Department**

University of Oviedo

Gijón, December 2018

## Acknowledgements

First of all, I would like to express my gratitude to my supervisor Prof. Fernando Briz for his continuous support and advice during the development of this thesis. Without his help, infinite patience and knowledge, this work would not have been possible.

I would like to address my thanks to the Power Electronics, Machines and Control group from the University of Nottingham and in particular to the head of group Prof. Jon Clare and my co-supervisor, Dr. Ralph Feldman, for giving me the opportunity to stay and work in their group. I would also like to thank other members of the group for their friendly welcome.

Furthermore, I wish to show my sincere thanks to all my friends and colleagues in the lab, Chema, Enrique, Mariam, Carlos, Alberto, for their continuous and unconditional support. They know this has not been an easy path and without their help, I would not be writing these words right now.

Finally, I would like to thank my parents and my close friends for their patience, encouragement and understanding. This work is somehow theirs as well.

## Abstract

Reducing the dependence on conventional fossil fuels has become a priority for industrialized countries due to environmental concerns, limited resources and the progressive increase of their cost. This scenario has pushed the penetration of renewable energies in the existing electric power system. However, massive integration of renewable energy into the existing and future grids poses major challenges, as a significant part of the installed capacity will be connected to the distribution levels. Innovative solutions based on high-power, high-voltage electronic power converters, like High Voltage Direct Current (HVDC), Flexible AC Transmission Systems (FACTS) and Solid State Transformers (SST) have the potential to cope with these challenges.

Multilevel converters are well suited for medium-high voltage and power ranges which are required for electronic power converters connected to medium voltage electrical grids. Among these, Modular Multilevel Converters (MMCs) appear as a promising topology for applications requiring a high voltage DC port. MMCs, which was first introduced one decade ago [47]-[49], realizes a bidirectional DC/AC power conversion. It shares those advantages intrinsic to multilevel converters, but adds some additional attractive features, such as modularity, scalability and distributed energy storage, therefore eliminating the need of a bulk DC capacitor.

This thesis covers both the MMC topology and Solid State Transformers mainly derived from MMC topology. Operational features such as modulation strategies, capacitor voltage balancing methods and control of the converter are covered. A thorough analysis and classification of existing circulating current control strategies is presented. Additionally, the MMC converter is also studied under abnormal operating conditions affecting to its voltage margins, such us transients in the DC or the AC ports voltages, or failures of one or more cells. Under these circumstances, the MMC can be forced to operate in the overmodulation region. Voltage limits and overmodulation techniques are discussed in this work. Conventional MMCs use cells consisting of a half-bridge and a capacitor. Control and modulation strategies developed for MMCs are aimed to balance the power between the AC and DC ports, which is needed to maintain the average voltage of the cells capacitors at its target value. It is possible however to transfer (absorb or deliver) power through the MMC cells. This enables new potential features, including distributed energy storage; integration of distributed energy resources (DER) at the cell level; and multiport multilevel power converters combining different low/high AC/DC ports, eventually leading to an MMC-based Solid State Transformer topology.

This work proposes the modification of conventional cells in the Modular Multilevel Converter to provide power transfer capability and thus, the transformation of this topology into the so-called MMC-based multiport power converter. Such multiport power converter can be asymmetric and symmetric, depending on the number and location of cells transferring power. Both options are covered in this thesis including their analysis, control strategies and limits of operation.

# Glossary

#### Acronyms

| $\mathbf{AC}$ | Alternating current               |

|---------------|-----------------------------------|

| ADC           | Analog-to-digital converter       |

| ARM           | Acorn RISC machine                |

| Btu           | British thermal unit              |

| CHB           | Cascaded H-bridge converter       |

| $\mathbf{CS}$ | Current sensor                    |

| DAB           | Dual active bridge                |

| DC            | Direct current                    |

| DER           | Distributed energy resources      |

| DSBC          | Double star bridge cells          |

| DSCC          | Double star chopper cells         |

| DSP           | Digital signal processor          |

| EMI           | Electromagnetic interference      |

| $\mathbf{EV}$ | Electric vehicle                  |

| FACTS         | Flexible AC transmission system   |

| FB            | Full bridge                       |

| $\mathbf{FC}$ | Flying capacitor converter        |

| FPGA          | Field-programmable gate array     |

| HB            | Half bridge                       |

| $\mathbf{HF}$ | High frequency                    |

| HV            | High voltage                      |

| HVAC          | High voltage alternating current  |

| HVDC          | High voltage direct current       |

| IGBT          | Insulated gate bipolar transistor |

| IPD           | In-phase disposition              |

|   | ٠ | ٠ | ٠ |

|---|---|---|---|

| V | 1 | 1 | 1 |

|   |   |   |   |

| I/O            | Input /Output                                     |

|----------------|---------------------------------------------------|

| I/O<br>LF      | Input/Output                                      |

| LF<br>LFT      | Low frequency                                     |

|                | Line frequency transformer                        |

|                | Low voltage                                       |

| LVAC           | Low voltage alternating current                   |

| LVDC           | Low voltage direct current                        |

| MMC            | Modular multilevel converter                      |

| M2C            | Modular multilevel converter                      |

| MMCC           | Modular multilevel cascade converter              |

| MOSFET         | Metal-oxide semiconductor field-effect transistor |

| $\mathbf{MV}$  | Medium voltage                                    |

| MVDC           | Medium voltage direct current                     |

| $\mathbf{NSF}$ | National science foundation                       |

| NPC            | Neutral point clamped converter                   |

| OF             | Optical fiber                                     |

| $\mathbf{PET}$ | Power electronic transformer                      |

| PHEV           | Plug-in hybrid electric vehicle                   |

| POD            | Phase-opposite disposition                        |

| $\mathbf{PWM}$ | Pulse width modulation                            |

| RISC           | Reduced instruction set computing                 |

| $\mathbf{RMS}$ | Root mean square                                  |

| SDBC           | Single delta bridge cells                         |

| $\mathbf{SiC}$ | Silicon carbide                                   |

| SoC            | System on a chip                                  |

| SSBC           | Single star bridge cells                          |

| $\mathbf{SST}$ | Solid state transformer                           |

| STATCOM        | Static synchronous compensator                    |

| $\mathbf{SVM}$ | Space vector modulation                           |

| THD            | Total harmonic distortion                         |

| UPFC           | Unified power flow controller                     |

| UPS            | Uninterruptible power supply                      |

| $\mathbf{VS}$  | Voltage sensor                                    |

| ZVS            | Zero voltage switching                            |

|                |                                                   |

#### Nomenclature

| $C_{cell}$   | Cell capacitance                                   |

|--------------|----------------------------------------------------|

| $cos\phi$    | Power factor                                       |

| $d_{xiT}$    | Top arm cell j $(j = 1 : N_{MMC})$ duty cycle      |

| U U          | in phase $x (x=u,v,w)$                             |

| $d_{xjB}$    | Bottom arm cell j $(j = 1 : N_{MMC})$ duty cycle   |

|              | in phase x $(x=u,v,w)$                             |

| d            | DAB phase shift in pu                              |

| k            | Number of voltage levels between two output phases |

| $i_{dc}$     | DC-port current                                    |

| $i_i$        | Input current in the DAB                           |

| $i_o$        | Output current in the DAB                          |

| $i_{LK}$     | Current through the DAB leakage inductance         |

| $i_{cu}$     | Circulating current flowing through phase u        |

| $i_{cv}$     | Circulating current flowing through phase v        |

| $i_{cw}$     | Circulating current flowing through phase w        |

| $i_{uT}$     | Top arm current in phase u                         |

| $i_{vT}$     | Top arm current in phase v                         |

| $i_{wT}$     | Top arm current in phase w                         |

| $i_{uB}$     | Bottom arm current in phase u                      |

| $i_{vB}$     | Bottom arm current in phase v                      |

| $i_{wB}$     | Bottom arm current in phase w                      |

| $i_u$        | AC-port phase u current                            |

| $i_v$        | AC-port phase v current                            |

| $i_w$        | AC-port phase w current                            |

| $i_{ac}$     | AC-port current complex vector                     |

| $i_{ac}^{*}$ | AC-port current complex vector conjugate           |

| $i_T$        | Top arm current complex vector                     |

| $i_B$        | Bottom arm current complex vector                  |

| $i_c$        | Circulating current complex vector                 |

| $i_{cDC}$    | DC component of circulating current complex vector |

| $i_d$        | d-axis component of AC port current vector         |

| $i_q$        | q-axis component of AC port current vector         |

| $i_{cell}$   | Current entering the cell from DAB                 |

| $L_{arm}$    | Arm inductance                                     |

| Relation between output and input voltage in DAB            |

|-------------------------------------------------------------|

| Number of faulty cells per arm in MMC                       |

| Number of cells transferring power per arm                  |

| Number of voltage levels in any phase of the converter with |

| respect to the middle point of the DC bus                   |

| Modulation index                                            |

| Middle point in the DC bus                                  |

| Number of submodules per phase in CHB                       |

| Number of submodules per arm in MMC                         |

| Transformer turns ratio                                     |

| Top arms power                                              |

| Bottom arms power                                           |

| DC-port active power                                        |

| AC-port active power                                        |

| Cells power in phase u                                      |

| Cells power in phase v                                      |

| Cells power in phase w                                      |

| Top arm cells power in phase u                              |

| Bottom arm cells power in phase u                           |

| Top arm cells power in phase v                              |

| Bottom arm cells power in phase v                           |

| Top arm cells power in phase w                              |

| Bottom arm cells power in phase w                           |

| Top arm cell j $(j = 1 : N_{MMC})$ active power             |

| Bottom arm cell j $(j = 1 : N_{MMC})$ active power          |

| Power from cell j $(j = 1 : N_{MMC})$ in top arm            |

| of phase x $(x=u,v,w)$                                      |

| Power from cell j $(j = 1 : N_{MMC})$ in bottom arm         |

| of phase x $(x=u,v,w)$                                      |

| DC power from all cells that transfer power in top arm      |

| DC power from conventional cells in top arm                 |

| DC power from all cells that transfer power in bottom arm   |

| DC power from conventional cells in bottom arm              |

| AC power from all cells that transfer power in top arm      |

| AC power from conventional cells in top arm                 |

| AC power from all cells that transfer power in bottom arm   |

|                                                             |

| $P_{ac2B}$       | AC power from conventional cells in bottom arm                       |

|------------------|----------------------------------------------------------------------|

| $P_{cell1T}$     | Power from all cells that transfer power in top arm                  |

| $P_{cell2T}$     | Power from conventional cells in top arm                             |

| $P_{cell1B}$     | Power from all cells that transfer power in bottom arm               |

| $P_{cell2B}$     | Power from conventional cells in bottom arm                          |

| $P_{cell}$       | Power transferred by a complex vector cell including                 |

|                  | top and bottom arms                                                  |

| $P_{cell-total}$ | Total power transferred by the cells                                 |

| $P_{DAB}$        | Power transferred by the DABs                                        |

| $P_{DABj}$       | Power transferred by an individual DAB                               |

| $Q_{ac}$         | AC-port reactive power                                               |

| $R_{arm}$        | Arm resistance                                                       |

| $R_x$            | Ratio between AC port and DC port voltage                            |

| $v_{cell}$       | Cell capacitor voltage                                               |

| $v_{celljxT}$    | Top arm cell j $(j = 1 : N_{MMC})$ capacitor                         |

|                  | voltage in phase x $(x=u,v,w)$                                       |

| $v_{celljxB}$    | Bottom arm cell j $(j = 1 : N_{MMC})$ capacitor                      |

|                  | voltage in phase x $(x=u,v,w)$                                       |

| $v_{celljx}$     | Cell j $(j = 1 : 2N_{MMC})$ capacitor                                |

|                  | voltage in phase x $(x=u,v,w)$                                       |

| $v_{dc}$         | DC-port voltage                                                      |

| $v_{LK}$         | Voltage drop in the DAB leakage inductance                           |

| $v_i$            | Input voltage in the DAB                                             |

| $v_o$            | Output voltage in the DAB                                            |

| $v_{uT}$         | Top arm cells voltage in phase u                                     |

| $v_{vT}$         | Top arm cells voltage in phase v                                     |

| $v_{wT}$         | Top arm cells voltage in phase w                                     |

| $v_{uB}$         | Bottom arm cells voltage in phase u                                  |

| $v_{vB}$         | Bottom arm cells voltage in phase v                                  |

| $v_{wB}$         | Bottom arm cells voltage in phase w                                  |

| $v_u$            | AC-port phase u voltage                                              |

| $v_v$            | AC-port phase v voltage                                              |

| $v_w$            | AC-port phase w voltage                                              |

| $v_{jxT}$        | Top arm cell j $(j = 1 : N_{MMC})$ voltage in phase x $(x=u,v,w)$    |

| $v_{jxB}$        | Bottom arm cell j $(j = 1 : N_{MMC})$ voltage in phase x $(x=u,v,w)$ |

| $v_n$            | Voltage applied to the neutral star point in CHB                     |

|                  |                                                                      |

| $v_{ac}$    | AC-port voltage complex vector                                    |

|-------------|-------------------------------------------------------------------|

| $v_T$       | Top arm complex vector cells voltage                              |

| $v_B$       | Bottom arm complex vector cells voltage                           |

| $v_{grid}$  | Grid voltage complex vector                                       |

| $v_L$       | Arm inductance voltage complex vector                             |

| $v_{Lx}$    | Arm inductance voltage in phase x $(x=u,v,w)$                     |

| $v_{jT}$    | Top arm cell j $(j = 1 : N_{MMC})$ voltage complex vector         |

| $v_{jB}$    | Bottom arm cell j $(j = 1 : N_{MMC})$ voltage complex vector      |

| $v_d$       | d-axis component of AC port voltage vector                        |

| $v_q$       | q-axis component of AC port voltage vector                        |

| $v_{dc1T}$  | DC voltage from all cells that transfer power in top arm          |

| $v_{dc2T}$  | DC voltage from conventional cells in top arm                     |

| $v_{dc1B}$  | DC voltage from all cells that transfer power in bottom arm       |

| $v_{dc2B}$  | DC voltage from conventional cells in bottom arm                  |

| $v_{ac1T}$  | AC complex voltage vector from all cells that transfer power      |

|             | in top arm                                                        |

| $v_{ac2T}$  | AC complex voltage vector from conventional cells in top arm      |

| $v_{ac1B}$  | AC complex voltage vector from all cells that transfer power      |

|             | in bottom arm                                                     |

| $v_{ac2B}$  | AC complex voltage vector from conventional cells                 |

|             | in bottom arm                                                     |

| $v_{acT}$   | AC complex voltage vector from all cells in top arm               |

| $v_{acB}$   | AC complex voltage vector from all cells in bottom arm            |

| $v_{dcT}$   | DC voltage from all cells in top arm                              |

| $v_{dcB}$   | DC voltage from all cells in bottom arm                           |

| $v_{acTd}$  | Real part of AC complex voltage vector from all cells             |

|             | in top arm                                                        |

| $v_{ac1Td}$ | Real part of AC complex voltage vector from all cells             |

|             | that transfer power in top arm                                    |

| $v_{ac2Td}$ | Real part of AC complex voltage vector from                       |

|             | conventional cells in top arm                                     |

| $v_{acTq}$  | Imaginary part of AC complex voltage vector from all cells        |

| 1           | in top arm                                                        |

| $v_{1T}$    | Complex cell voltage accounting for all cells that transfer power |

|             | in top arm                                                        |

| $v_{2T}$    | Complex cell voltage accounting for conventional cells in top arm |

|             |                                                                   |

| in top arm                                                                    |               |

|-------------------------------------------------------------------------------|---------------|

| $v_{2B}$ Complex cell voltage accounting for conventional cells               |               |

| in bottom arm                                                                 |               |

| $v_{acjxT}$ Top arm cell j $(j = 1 : N_{MMC})$ AC voltage                     |               |

| in phase $x (x=u,v,w)$                                                        |               |

| $v_{acjxB}$ Bottom arm cell j $(j = 1 : N_{MMC})$ AC voltage                  |               |

| in phase $x (x=u,v,w)$                                                        |               |

| $v_{jxT}$ Top arm cell j $(j = 1 : N_{MMC})$ voltage                          |               |

| in phase $x (x=u,v,w)$                                                        |               |

| $v_{jxB}$ Bottom arm cell j $(j = 1 : N_{MMC})$ voltage                       |               |

| in phase $x (x=u,v,w)$                                                        |               |

| $\Delta v_{dc}$ DC voltage imbalance                                          |               |

| $\Delta v_{ac}$ AC voltage vector imbalance                                   |               |

| $\Delta P_{cell}$ Variation in the power transferred by cells                 |               |

| $\Delta Re(v_{ac})$ Real part of AC voltage vector imbalance                  |               |

| $\Delta v_{dc1T}$ DC voltage imbalance from all cells that transfer power     |               |

| in top arm                                                                    |               |

| $\Delta Re(v_{ac1T})$ Real part of AC voltage vector imbalance from all cells |               |

| that transfer power in top arm                                                |               |

| $\varphi_{grid}$ Grid voltage vector angle                                    |               |

| $\varphi$ Angle between AC port voltage and current complex vector            | $\mathbf{rs}$ |

| $\omega_e$ Fundamental frequency                                              |               |

#### Superscripts

| $\overline{x}$ | DC component    |

|----------------|-----------------|

| $x^*$          | Commanded value |

xiv

## Contents

| 1 | Intr | troduction |            |                                                     |    |

|---|------|------------|------------|-----------------------------------------------------|----|

|   | 1.1  | Backg      | round      |                                                     | 1  |

|   | 1.2  | Frame      | work       |                                                     | 2  |

|   | 1.3  | Object     | tives      |                                                     | 2  |

|   | 1.4  | Docun      | nent struc | ture                                                | 3  |

| 2 | Mu   | ltilevel   | Power (    | Converters and Solid State Transformers             | 5  |

|   | 2.1  | The ne     | ew power-  | electronics-based energy network scenario           | 5  |

|   | 2.2  | Multil     | evel Conv  | erters                                              | 9  |

|   |      | 2.2.1      | Motivati   | on and Main Features of Multilevel Converters       | 10 |

|   |      | 2.2.2      | Review of  | of Multilevel Topologies                            | 11 |

|   |      |            | 2.2.2.1    | Neutral Point Clamped (NPC) Converter               | 12 |

|   |      |            | 2.2.2.2    | Capacitor-Clamped (Flying Capacitor) Con-<br>verter | 15 |

|   |      |            | 2.2.2.3    | Cascaded H-Bridge (CHB) Converter $\ldots$          | 18 |

|   |      | 2.2.3      | Fields of  | Application of Multilevel Converter                 | 20 |

|   | 2.3  | Solid S    | State Trar | nsformers                                           | 21 |

|   |      | 2.3.1      | SST Top    | oologies                                            | 25 |

|   |      |            | 2.3.1.1    | Three-stage SST                                     | 25 |

|   |     |                                     | 2.3.1.2                                | Two-stage SST                                                                                                          | 27 |  |  |

|---|-----|-------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|----|--|--|

|   |     |                                     | 2.3.1.3                                | One-Stage SST                                                                                                          | 28 |  |  |

|   |     | 2.3.2                               | The Dua                                | al Active Bridge (DAB)                                                                                                 | 29 |  |  |

|   |     |                                     | 2.3.2.1                                | Principles of operation                                                                                                | 29 |  |  |

|   |     |                                     | 2.3.2.2                                | Performance Considerations                                                                                             | 31 |  |  |

|   | 2.4 | Summ                                | ary                                    |                                                                                                                        | 34 |  |  |

| 3 | Mo  | dular I                             | Multilev                               | el Converters (MMC/M2C)                                                                                                | 35 |  |  |

|   | 3.1 | Introd                              | luction                                |                                                                                                                        | 35 |  |  |

|   | 3.2 | Princi                              | ples of Op                             | peration of the MMC                                                                                                    | 39 |  |  |

|   |     | 3.2.1                               | CHB vs.                                | . MMC                                                                                                                  | 41 |  |  |

|   | 3.3 | MMC                                 | MMC modeling and power balance         |                                                                                                                        |    |  |  |

|   |     | 3.3.1                               | The Circulating Current                |                                                                                                                        |    |  |  |

|   |     | 3.3.2                               | Passive                                | Elements Sizing                                                                                                        | 47 |  |  |

|   | 3.4 | Modu                                | ulation Strategies                     |                                                                                                                        |    |  |  |

|   | 3.5 | Capacitor Voltage Balancing Methods |                                        |                                                                                                                        |    |  |  |

|   |     | 3.5.1                               | 5.1 Sorting Algorithm                  |                                                                                                                        |    |  |  |

|   |     | 3.5.2                               | Individual Capacitor Voltage Balancing |                                                                                                                        |    |  |  |

|   | 3.6 | Contr                               | ol of the l                            | ММС                                                                                                                    | 52 |  |  |

|   |     | 3.6.1                               | Circulat                               | ing Current Control Strategies                                                                                         | 53 |  |  |

|   |     |                                     | 3.6.1.1                                | No circulating current control: Direct mod-<br>ulation                                                                 | 53 |  |  |

|   |     |                                     | 3.6.1.2                                | Suppression of the $2\omega_e$ component of the circulating current $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 54 |  |  |

|   |     |                                     | 3.6.1.3                                | Control of the DC component of the circulating current $i_{cDC}$                                                       | 54 |  |  |

|   |     |                                     | 3.6.1.4                                | Control of the DC and $2\omega_e$ components of the circulating current: $i_{cDC} + 2\omega_e$                         | 55 |  |  |

|   |                                                                     |                                                                | 3.6.1.5   | Control of the DC component and suppression of the $2\omega_e$ component of the circulating current | 55 |  |  |

|---|---------------------------------------------------------------------|----------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------|----|--|--|

|   |                                                                     |                                                                | 3.6.1.6   | Control of the DC and $\omega_e$ components of the circulating current: $i_{cDC} + \omega_e$        | 55 |  |  |

|   |                                                                     |                                                                | 3.6.1.7   | Circulating current control with high frequency circulating current injection (Motor drives) .      | 55 |  |  |

|   |                                                                     | 3.6.2                                                          | Overview  | v of outer control loops                                                                            | 58 |  |  |

|   | 3.7                                                                 | MMC                                                            | Operation | n Under Voltage Constraints                                                                         | 60 |  |  |

|   |                                                                     | 3.7.1                                                          | AC vs. I  | DC Voltage Ratio                                                                                    | 60 |  |  |

|   |                                                                     | 3.7.2                                                          | Voltage 2 | Limits of the MMC                                                                                   | 62 |  |  |

|   |                                                                     | 3.7.3                                                          | Overmoo   | lulation Strategies for MMCs                                                                        | 63 |  |  |

|   |                                                                     | 3.7.4                                                          | MMC O     | peration Under Voltage Constraints                                                                  | 65 |  |  |

|   |                                                                     | 3.7.5                                                          | Simulati  | on Results                                                                                          | 68 |  |  |

|   | 3.8                                                                 | .8 MMCs for Variable-Speed Drive Applications                  |           |                                                                                                     |    |  |  |

|   | 3.9                                                                 | Summ                                                           | ary       |                                                                                                     | 72 |  |  |

| 4 | 4 MMC-based Multiport Power Converter and Solid Sta<br>Transformers |                                                                |           |                                                                                                     |    |  |  |

|   | 4.1                                                                 | MMC                                                            | Using Ce  | lls with Power Transfer Capability                                                                  | 76 |  |  |

|   |                                                                     | 4.1.1                                                          | Modeling  | g and Power Balance                                                                                 | 76 |  |  |

|   | 4.2                                                                 | Asymmetric MMC-based Multiport Power Converter Topolo-<br>gies |           |                                                                                                     |    |  |  |

|   |                                                                     | 4.2.1                                                          | Types of  | asymmetries                                                                                         | 84 |  |  |

|   |                                                                     | 4.2.2                                                          | Power B   | alance Constraints                                                                                  | 85 |  |  |

|   |                                                                     | 4.2.3                                                          |           | f Operation of Cells with Power Transfer Ca-                                                        | 87 |  |  |

|   |                                                                     |                                                                | 4.2.3.1   | Submodules and MMC Voltage Limits                                                                   | 88 |  |  |

|     |       | 4.2.3.2  | Maximum Power Transfer Using AC VoltageImbalance89                                                          |

|-----|-------|----------|-------------------------------------------------------------------------------------------------------------|

|     |       | 4.2.3.3  | Maximum Power Transfer Using DC VoltageImbalance92                                                          |

|     | 4.2.4 |          | d Control Strategies Using Cells with Power<br>Capability                                                   |

|     |       | 4.2.4.1  | No explicit selection of $\Delta v_{dc}$ and $\Delta Re(v_{ac})$ . 96                                       |

|     |       | 4.2.4.2  | Explicit selection of $\Delta v_{dc}$ and $\Delta Re(v_{ac})$ 96                                            |

|     | 4.2.5 | Control  | Strategies: Simulation Results                                                                              |

| 4.3 |       |          | IC-based Multiport Power Converter Topolo-<br>ed SST                                                        |

|     | 4.3.1 | MMC B    | ased Multiport Power Converters 99                                                                          |

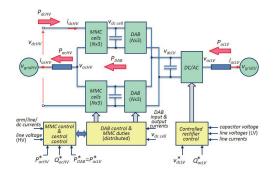

|     | 4.3.2 | Control  | Strategies for the Multiport Power Converter 102                                                            |

|     |       | 4.3.2.1  | Grid feeding configuration                                                                                  |

|     |       | 4.3.2.2  | Grid forming configuration                                                                                  |

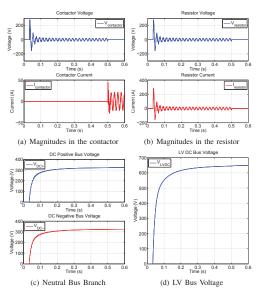

|     | 4.3.3 | Simulati | on Results $\ldots \ldots 105$ |

|     | 4.3.4 | Control  | System Implementation                                                                                       |

|     |       | 4.3.4.1  | Centralized Control                                                                                         |

|     |       | 4.3.4.2  | Distributed Control                                                                                         |

|     |       | 4.3.4.3  | Selection of Control Hardware and Commu-<br>nications                                                       |

| 4.4 | CHB   | vs. MMC  | -based Multiport Power Electronic Transformer113                                                            |

|     | 4.4.1 | CHB-ba   | sed Power Electronic Transformer 114                                                                        |

|     | 4.4.2 | MMC-b    | ased Power Electronic Transformer 115                                                                       |

|     | 4.4.3 | Cell & I | Devices Count and Ratings                                                                                   |

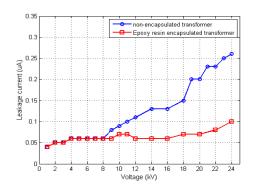

|     | 4.4.4 | High Fre | equency Transformer Design                                                                                  |

| 4.5 | Summ  | ary      |                                                                                                             |

| <b>5</b> | Con            | clusions and Future Work                | 125 |

|----------|----------------|-----------------------------------------|-----|

|          | 5.1            | Conclusions                             | 125 |

|          | 5.2            | Contributions                           | 126 |

|          | 5.3            | Future Work                             | 128 |

| 6        | Con            | nclusiones y Trabajo Futuro             | 131 |

|          | 6.1            | Conclusiones                            | 131 |

|          | 6.2            | Aportaciones                            | 132 |

|          | 6.3            | Trabajo Futuro                          | 134 |

| A        | Exp            | perimental Setups & Results             | 137 |

|          | A.1            | Introduction                            | 137 |

|          | A.2            | Down scaled Single-phase MMC            | 138 |

|          |                | A.2.1 Circulating current control tests | 139 |

|          | A.3            | Down scaled Three-phase MMC             | 140 |

|          | A.4            | Down scaled Single-phase MMC-based SST  | 140 |

|          |                | A.4.1 Asymmetric Operation              | 141 |

|          | A.5            | Down scaled Three-phase MMC-based SST   | 143 |

|          |                | A.5.1 Asymmetric Operation              | 143 |

|          | A.6            | Full-size CHB-based SST cell            | 144 |

|          |                | A.6.1 Cell commissioning                | 145 |

| в        | $\mathbf{Rel}$ | ated publications                       | 149 |

|          | B.1            | Summary of Publications                 | 149 |

| Bi       | bliog          | graphy                                  | 255 |

# List of Figures

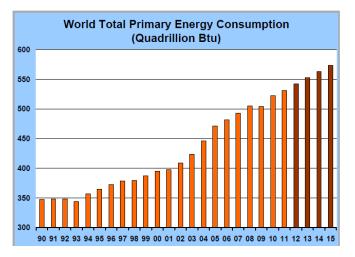

| 2.1  | World total energy consumption expressed in Quadrillion Btu along the period from 1990-2015 [3]                                                    | 6  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

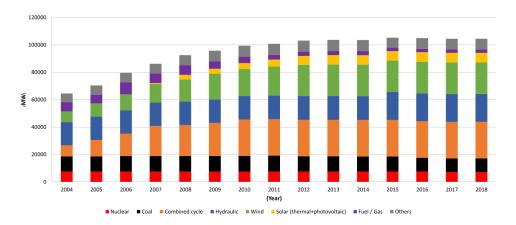

| 2.2  | Installed power capacity in Spain (MW) during the period 2004-2018 distributed between different energy sources $[4]$                              | 6  |

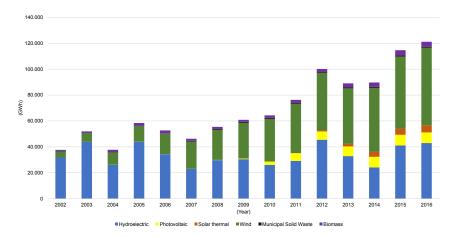

| 2.3  | Renewable energy generation capacity in Spain (GWh) dur-<br>ing the period 2002-2016 distributed between different energy<br>sources [5]           | 7  |

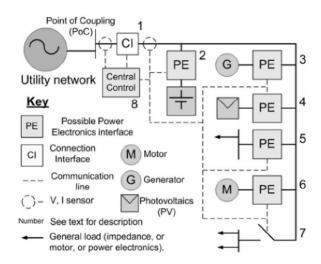

| 2.4  | Potential Microgrid System Technologies [10]                                                                                                       | 9  |

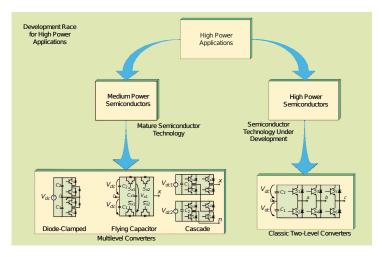

| 2.5  | Two-level power converters versus most common multilevel<br>power converters [11]                                                                  | 10 |

| 2.6  | Three-level Neutral Point Clamped (NPC) converter $\ . \ . \ .$                                                                                    | 12 |

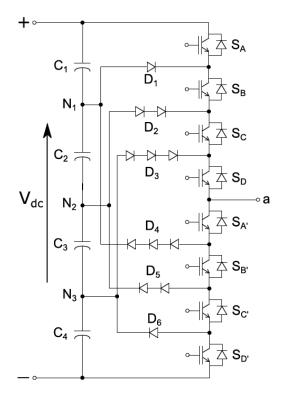

| 2.7  | Five-level Neutral Point Clamped (NPC) converter. Phase a.                                                                                         | 13 |

| 2.8  | Three-level Flying Capacitor Converter.                                                                                                            | 15 |

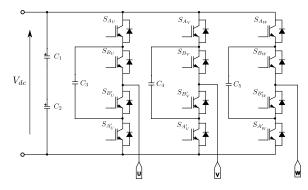

| 2.9  | Five-level Flying Capacitor Converter.                                                                                                             | 16 |

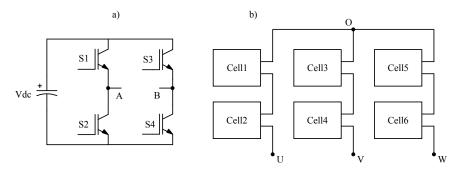

| 2.10 | a) Individual H-Bridge cell. b) 5-level Cascaded H-Bridge converter                                                                                | 18 |

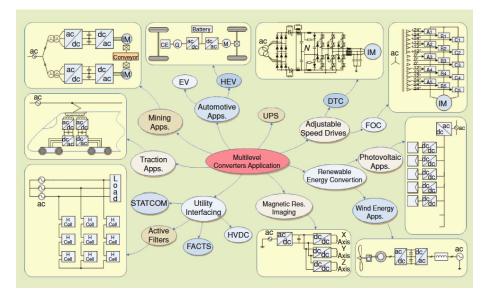

| 2.11 | Multilevel Converter-based applications overview $[11]$                                                                                            | 20 |

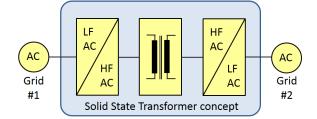

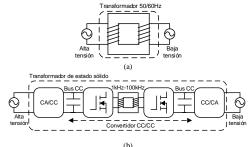

| 2.12 | SST concept [40] based on four quadrant switches able to control output voltage and/or input current amplitude while providing galvanic isolation. | 23 |

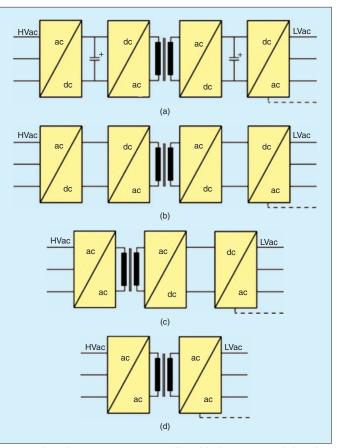

| 2.13 | Solid State Transformer concept. Basic power conversion representation.                                                                            | 23 |

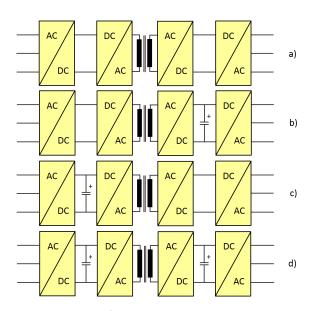

| 2.14 | Three-Stage SST. a) MV-side indirect matrix converter/LV-<br>side indirect matrix converter b) MV-side indirect matrix<br>converter/LV-side DC-link back-to-back converter c) MV-side<br>DC-link back-to-back converter/LV-side indirect matrix con-<br>verter d) MV-side DC-link back-to-back converter/LV-side<br>DC-link back-to-back converter | 26   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

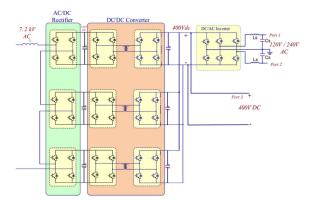

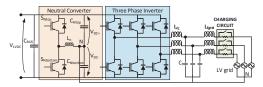

| 2.15 | Topology of the proposed FREEDM SST topology [31]                                                                                                                                                                                                                                                                                                  | 27   |

| 2.16 | Two-Stage SST. a) MV-side direct matrix converter/LV-side<br>indirect matrix converter b) MV-side direct matrix converter/LV-<br>side DC-link back-to-back converter c) MV-side indirect ma-<br>trix converter/LV-side direct matrix converter d) MV-side<br>DC-link back-to-back converter/LV-side direct matrix con-<br>verter                   | - 28 |

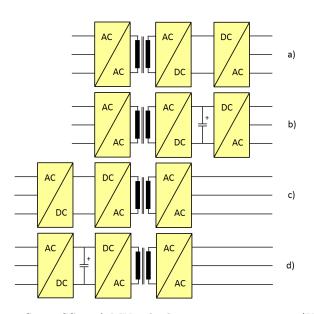

| 2.17 | One-Stage SST. MV-side direct matrix converter/LV-side direct matrix converter                                                                                                                                                                                                                                                                     | 28   |

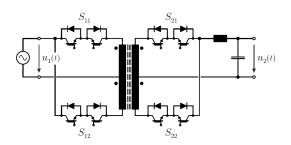

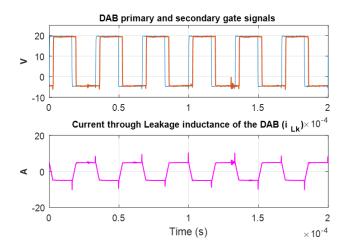

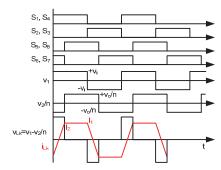

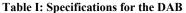

| 2.18 | Schematic representation of DAB converter                                                                                                                                                                                                                                                                                                          | 29   |

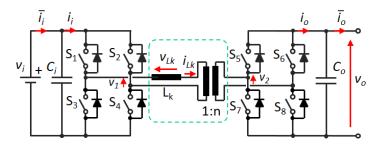

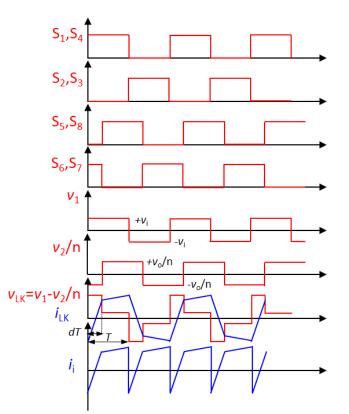

| 2.19 | Waveforms of the DAB converter                                                                                                                                                                                                                                                                                                                     | 30   |

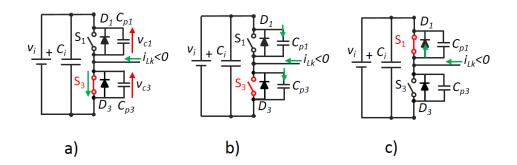

| 2.20 | ZVS operation. Charging and discharging of the parasitic capacitors $C_{p1}, C_{p3}$ in one branch of the DAB during the switching process. a) $S_1$ is opened and $S_3$ is closed b) Dead time: both $S_1$ and $S_3$ are opened c) $S_1$ is closed and $S_3$ is opened.                                                                           | 32   |

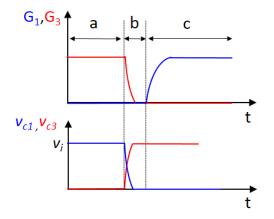

| 2.21 | ZVS operation. Gate signals $(G_1,G_3)$ and voltage at the par-<br>asitic capacitor $(v_{c1},v_{c3})$ in one branch of the DAB during<br>the switching process. a,b,c represent periods of time with<br>the circuit representation showed in Fig.2.20                                                                                              | 32   |

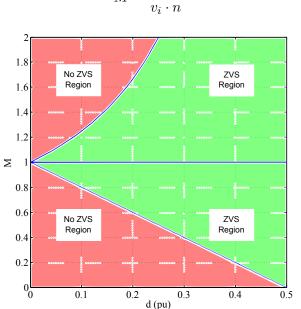

| 2.22 | Limits of operation of the DAB in ZVS conditions as a func-<br>tion of the phase shift $d$ and the ratio between output and<br>input voltages $M. \ldots \ldots$                                                                                                                    | 33   |

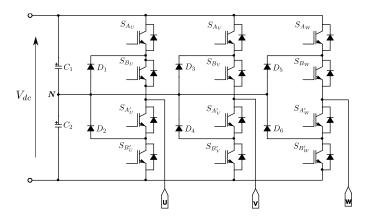

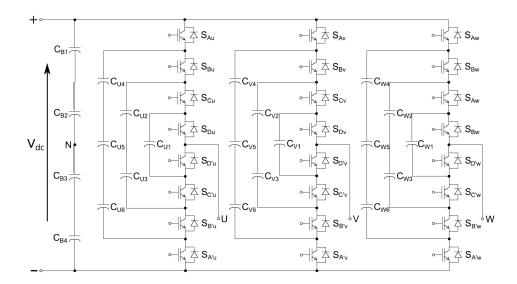

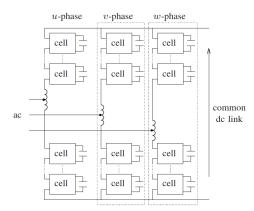

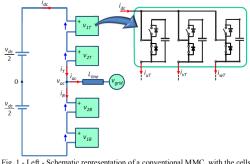

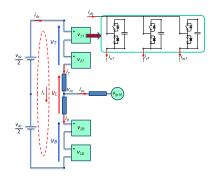

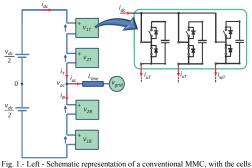

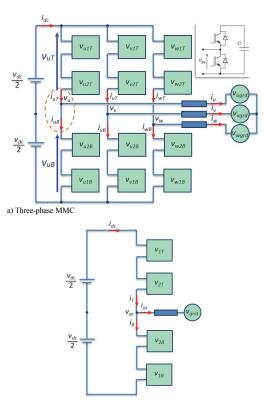

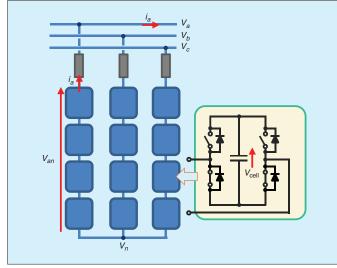

| 3.1  | Circuit configuration of a three-phase MMC.                                                                                                                                                                                                                                                                                                        | 36   |

| 3.2  | Submodule circuit configurations: a) Full bridge (Bridge cell)<br>b) Half bridge (Chopper cell)                                                                                                                                                                                                                                                    | 36   |

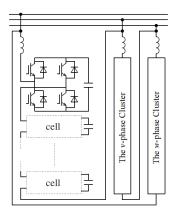

| 3.3  | Circuit configuration of MMCC-SDBC [54]                                                                                                                                                                                                                                                                                                            | 38   |

| 3.4  | Circuit configuration of MMCC using coupled arm inductors [54].                                                                                                                                                                                                                                                                                    | 38   |

| 3.5  | Schematic representation of a three-phase grid-connected MMC.<br>Arm inductors are not shown for the sake of simplicity (see<br>Fig. 3.1 for reference)                                                                                                                                                                                                                                                | 40 |

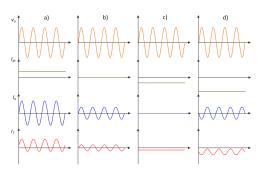

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

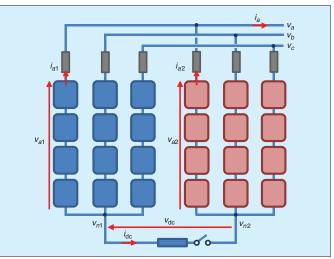

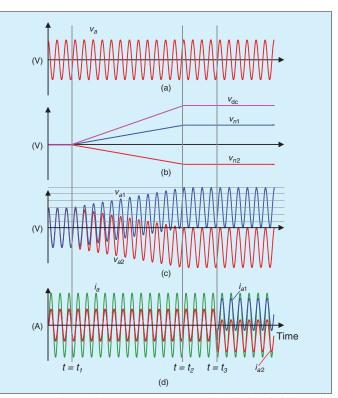

| 3.6  | a- Two CHB converters parallel connected. Their neutral star-connection points are linked in order to generate a DC voltage. b- From top to bottom: Voltage applied to the neutral points $v_{n1}, v_{n2}$ and DC link voltage $v_{dc}$ ; Voltage generated by the cells of both converters $v_{a1}, v_{a2}$ ; Output phase "a" grid current $i_a$ and arm currents $i_{a1}, i_{a2}, \ldots, \ldots$ . | 41 |

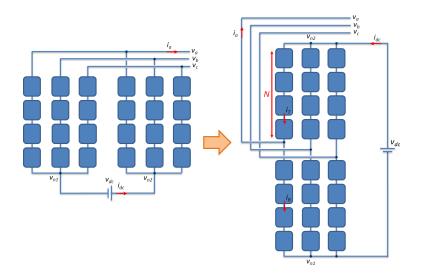

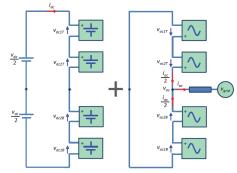

| 3.7  | Transformation of two CHB converters parallel connected into<br>an MMC. MMC is now able to generate a DC link                                                                                                                                                                                                                                                                                          | 42 |

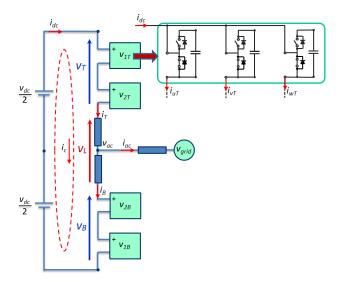

| 3.8  | Left- <i>Complex vector</i> equivalent circuit of a three-phase MMC.<br>Each <i>complex vector cell</i> corresponds to three conventional half-bridge cells.                                                                                                                                                                                                                                           | 43 |

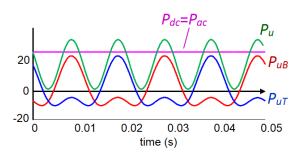

| 3.9  | MMC powers wave shape representation. DC power $P_{dc}$ , AC power $P_{ac}$ , power generated by the top cells $P_{uT}$ , power generated by the bottom cells $P_{uB}$ and total power in the leg $P_u$ . It has been particularized for phase $u$ .                                                                                                                                                   | 46 |

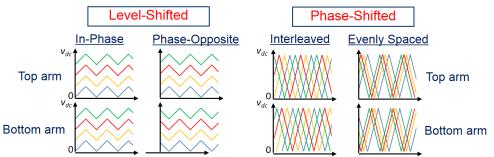

| 3.10 | Modulation strategies. Left- Level-shifted. Right- Phase-<br>shifted                                                                                                                                                                                                                                                                                                                                   | 49 |

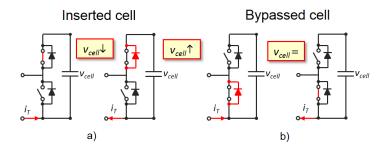

| 3.11 | Submodule capacitor voltage balancing actions                                                                                                                                                                                                                                                                                                                                                          | 50 |

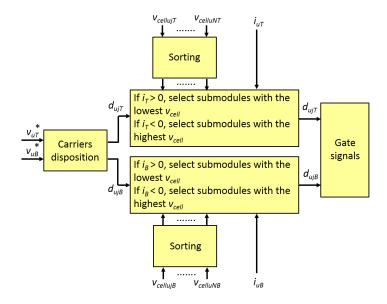

| 3.12 | Block diagram including sorting algorithm approach                                                                                                                                                                                                                                                                                                                                                     | 51 |

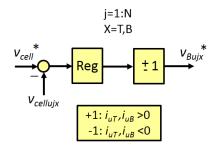

| 3.13 | Individual capacitor voltage balancing                                                                                                                                                                                                                                                                                                                                                                 | 52 |

| 3.14 | Circulating current control loop (per phase). k stands for $u,v$ or w.                                                                                                                                                                                                                                                                                                                                 | 54 |

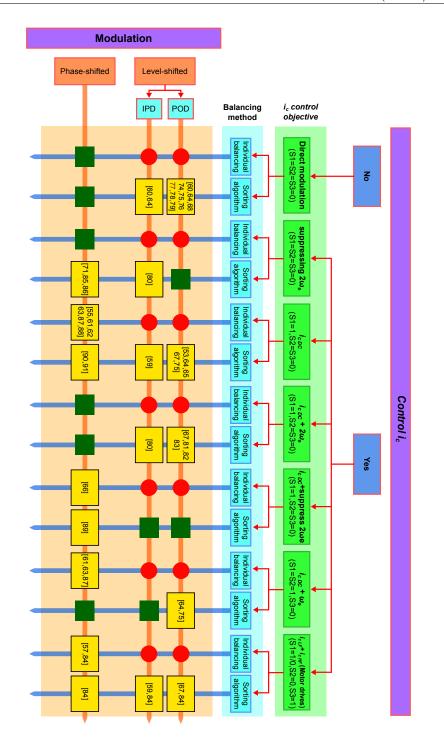

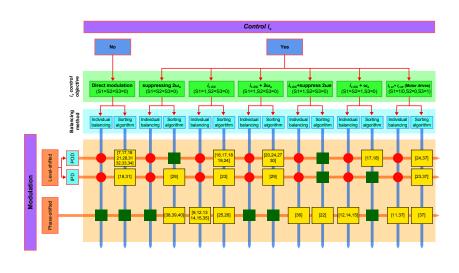

| 3.15 | Classification of circulating current control and modulation<br>methods for MMCs. References using <i>Phase-shifted</i> modula-<br>tion in this figure implement <i>Interleaved carriers</i> (See Table<br>3.2)                                                                                                                                                                                        | 56 |

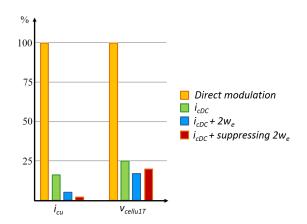

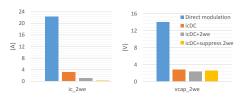

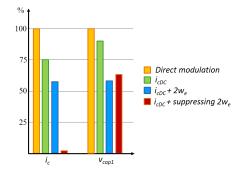

| 3.16 | Simulation results. Magnitude of the $2\omega_e$ component of circulating current $i_{cu}$ and a capacitor voltage $v_{cellu1T}$ , for four different control strategies. Level-shifted POD modulation was used. The magnitudes are expressed in % of the worst case, which corresponds to direct modulation.                                                                                          | 57 |

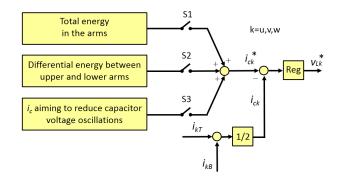

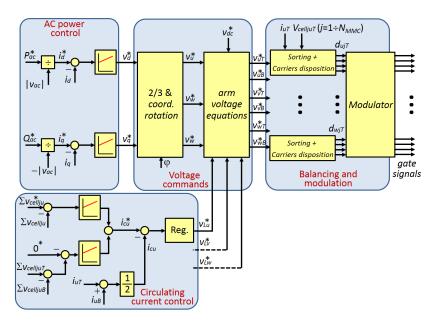

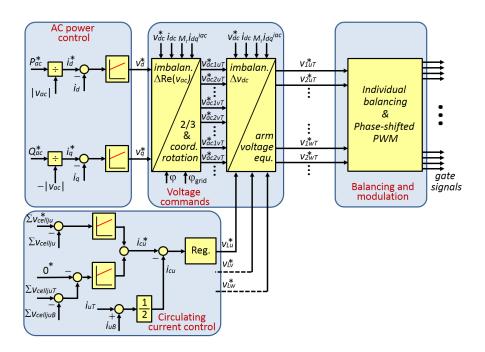

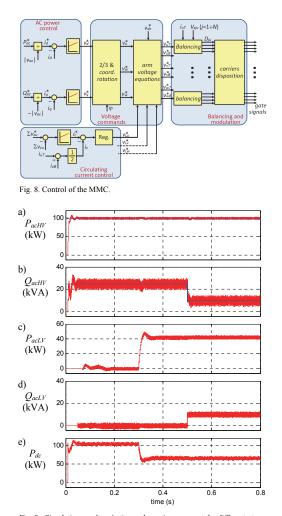

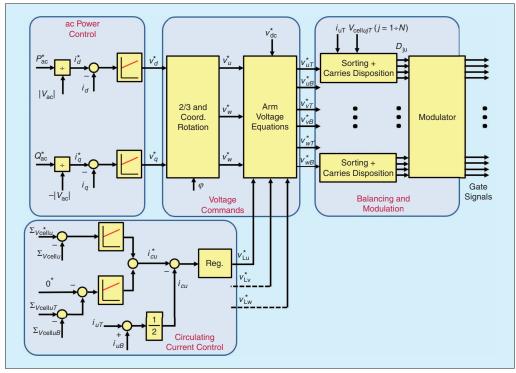

| 3.17 | MMC overall control scheme based on sorting algorithm                                                                                                                                                                                                                                                                                                                                                  | 58 |

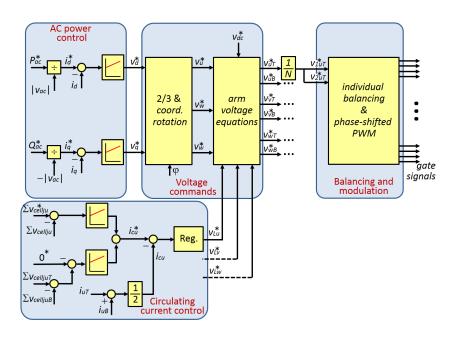

| 3.18 | MMC overall control scheme based on individual capacitor voltage balancing.                                                                                                                                                                                                            | 59 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

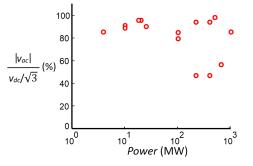

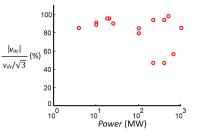

| 3.19 | AC-to-DC voltage ratio $R$ vs. power of already installed (or under development) MMC.                                                                                                                                                                                                  | 61 |

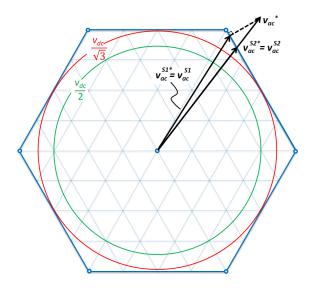

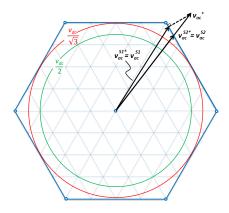

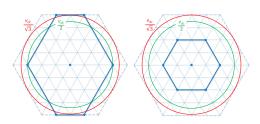

| 3.20 | Voltage limits and overmodulation strategies for a grid-connected MMC with 4 cells per arm. Outer and inner circles correspond to the cases with and without zero sequence voltage (triplen harmonics) injection respectively.                                                         | 62 |

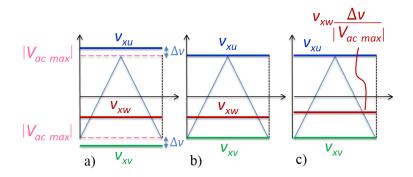

| 3.21 | a) zero sequence voltage injection. Unlimited voltage vector;<br>b) Minimum error $(v_{ac}^{S1}$ in Fig. 3.20); c) Minimum phase<br>error $(v_{ac}^{S2}$ in Fig. 3.20)                                                                                                                 | 64 |

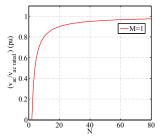

| 3.22 | Reduction of the AC port voltage limit vs. number of cells per arm $(N_{MMC})$ in the event of one $(M_f = 1)$ faulty cell                                                                                                                                                             | 66 |

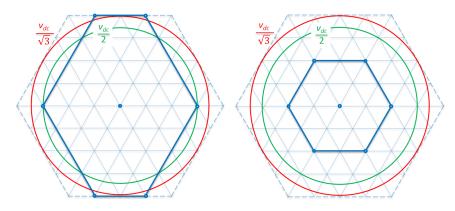

| 3.23 | Overmodulation limits in the case of a faulty cell. Left- Asymmetric legs: $N_u = 3$ , $N_v = N_w = 4$ in the top and bottom arms of one leg respectively. Right- Symmetric arms and legs: $N_u = N_v = N_w = 3$ .                                                                     | 67 |

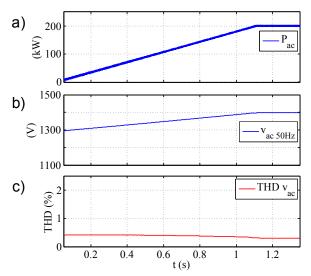

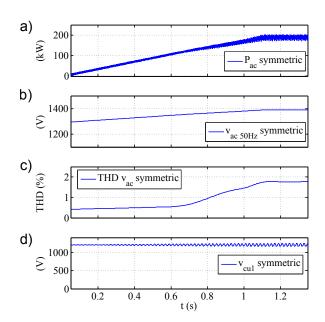

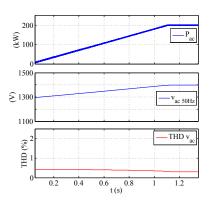

| 3.24 | MMC in normal operation, i.e. without going into overmod-<br>ulation. From top to bottom: a) AC active power, b) funda-<br>mental component of AC voltage; c) THD of AC voltage                                                                                                        | 68 |

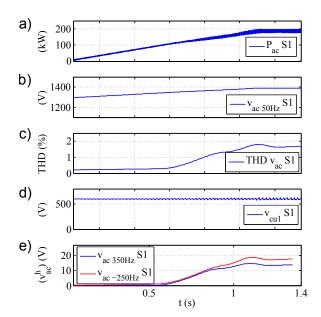

| 3.25 | Simulation results. <i>Minimum error</i> (S1) overmodulation method<br>From top to bottom: a) AC active power, b) fundamental<br>component of AC voltage, c) THD of AC voltage, d) voltage<br>of one cell capacitor, e) 350Hz and -250Hz components of AC<br>voltage vector.           | 69 |

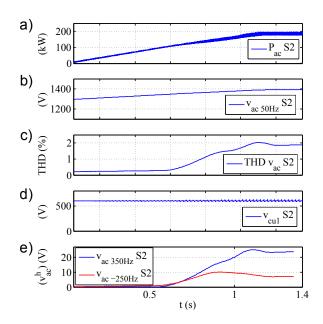

| 3.26 | Simulation results. <i>Minimum phase error</i> (S2) overmodula-<br>tion method. From top to bottom: a) AC active power, b)<br>fundamental component of AC voltage, c) THD of AC volt-<br>age, d) voltage of one cell capacitor, e) 350Hz and -250Hz<br>components of AC voltage vector | 70 |

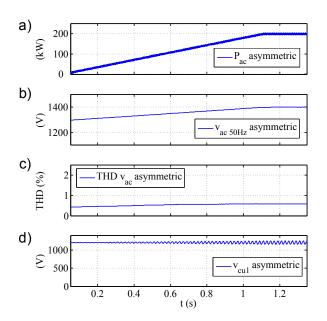

| 3.27 | Simulation results showing the effects of a faulty cell using <i>Minimum error</i> overmodulation, for the case of <i>asymmetric</i> operation of the MMC                                                                                                                              | 70 |

| 3.28 | Simulation results showing the effects of a faulty cell using <i>Minimum error</i> overmodulation, for the case of <i>symmetric</i> operation of the MMC                                                                                                                               | 71 |

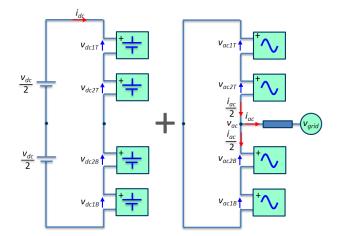

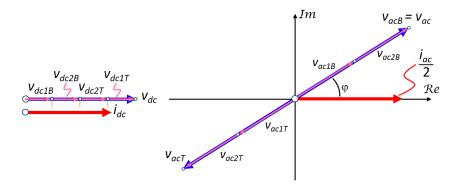

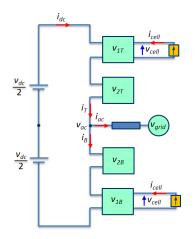

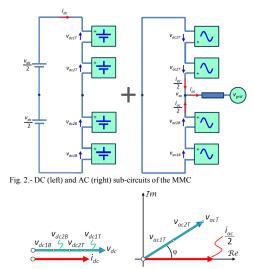

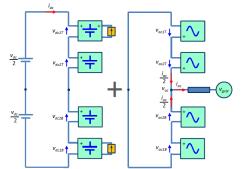

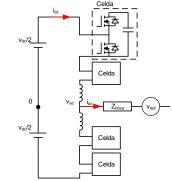

| 4.1                                             | DC (left) nad AC (right) subcircuits of the MMC 77                                                                                                                                                                                                                                                                                  |   |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 4.2                                             | DC (left) and AC (right) voltages and currents                                                                                                                                                                                                                                                                                      |   |

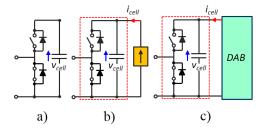

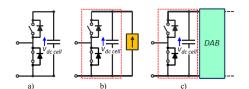

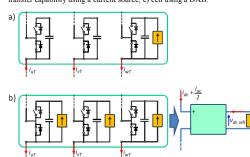

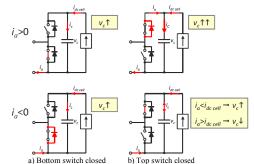

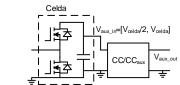

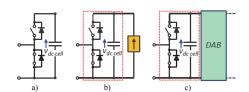

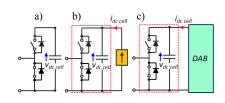

| 4.3                                             | a) Conventional half-bridge cell with a capacitor in the DC link; b) cell including a current source; c) cell using a DAB 79                                                                                                                                                                                                        |   |

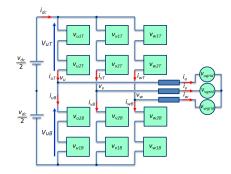

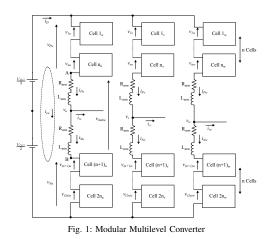

| 4.4                                             | MMC including cells with power transfer capability in all the three phases. Same number of cells in top and bottom arms transfer power                                                                                                                                                                                              |   |

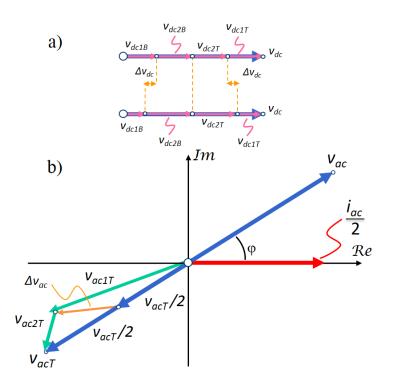

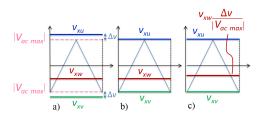

| 4.5                                             | Voltage imbalance for $P_{ac} > 0$ . a- DC cell voltage imbalance.<br>b- AC cell voltage imbalance                                                                                                                                                                                                                                  |   |

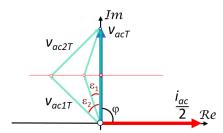

| 4.6                                             | Strategies for the selection of the cell AC voltage imbalance.<br>a- Same AC voltage magnitude b- Same angle with respect to<br>the AC current c- Same imaginary component $(\text{Im}(v_{ac1T})=\text{Im}(v_{ac2T}))$<br>In all the three cases the real component of AC voltage is<br>changed                                     | • |

| 4.7                                             | a) Cell power $P_{cell}$ ; b) DC port power $P_{dc}$ ; c) AC port power $P_{ac}$ ; as a function of $\Delta v_{dc}$ and $\Delta Re(v_{ac})$ , for constant AC power 83                                                                                                                                                              |   |

|                                                 |                                                                                                                                                                                                                                                                                                                                     |   |

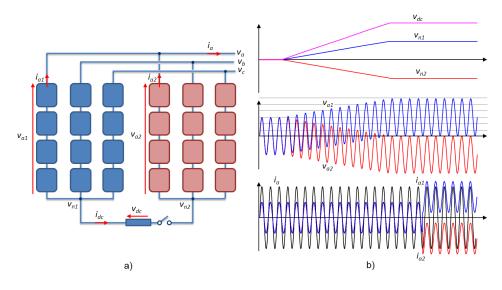

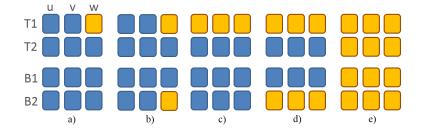

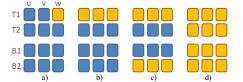

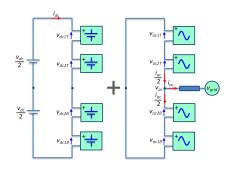

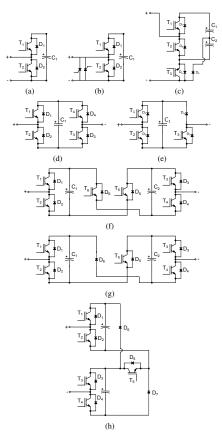

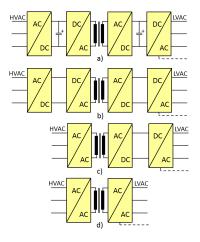

| 4.8                                             | MMC configurations including cells with power transfer ca-<br>pability. Cells in light color transfer power, cells in dark color<br>do not. a) asymmetric phases and arms; b) symmetric arms,<br>asymmetric phases; c) asymmetric top and bottom arms; d)<br>symmetric top and bottom arms, asymmetric cells; e) fully<br>symmetric |   |

| <ul><li>4.8</li><li>4.9</li></ul>               | MMC configurations including cells with power transfer ca-<br>pability. Cells in light color transfer power, cells in dark color<br>do not. a) asymmetric phases and arms; b) symmetric arms,<br>asymmetric phases; c) asymmetric top and bottom arms; d)<br>symmetric top and bottom arms, asymmetric cells; e) fully              |   |

| 4.9<br>4.10                                     | MMC configurations including cells with power transfer ca-<br>pability. Cells in light color transfer power, cells in dark color<br>do not. a) asymmetric phases and arms; b) symmetric arms,<br>asymmetric phases; c) asymmetric top and bottom arms; d)<br>symmetric top and bottom arms, asymmetric cells; e) fully<br>symmetric |   |

| 4.9<br>4.10                                     | MMC configurations including cells with power transfer capability. Cells in light color transfer power, cells in dark color<br>do not. a) asymmetric phases and arms; b) symmetric arms,<br>asymmetric phases; c) asymmetric top and bottom arms; d)<br>symmetric top and bottom arms, asymmetric cells; e) fully<br>symmetric      |   |

| <ul><li>4.9</li><li>4.10</li><li>4.11</li></ul> | MMC configurations including cells with power transfer ca-<br>pability. Cells in light color transfer power, cells in dark color<br>do not. a) asymmetric phases and arms; b) symmetric arms,<br>asymmetric phases; c) asymmetric top and bottom arms; d)<br>symmetric top and bottom arms, asymmetric cells; e) fully<br>symmetric |   |

| 4.13 | Maximum power transferred by the cells for a) $M_t = 1$ , b)<br>$M_t = 2$ and c) $M_t = 3$ ( $N_{MMC} = 4$ ), as a function of the<br>apparent power and load angle, for the case of DC (left) and<br>AC (right) voltage imbalances. $R_{thi} = 0.8$ (fixed) 95                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

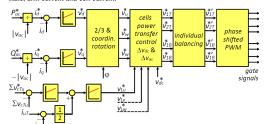

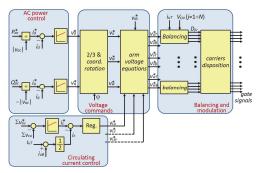

| 4.14 | Explicit selection of AC and/or DC cell voltage imbalances.<br>Proposed MMC control                                                                                                                                                                                                                                                                                                                             |

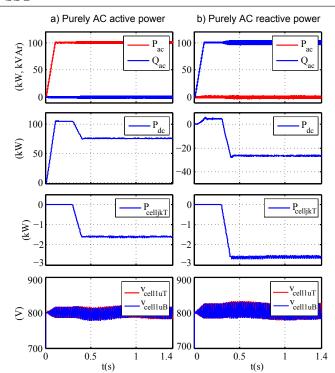

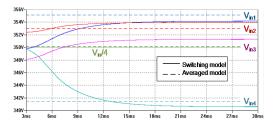

| 4.15 | Simulation results. MMC with four cells per arm $(N_{MMC} = 4)$ . From top to bottom: AC active and reactive powers, DC port power, power injected by one cell, capacitor voltages for cells #1T and #1B of phase $u$ . a) $P_{ac} = 100$ kW, $Q_{ac} = 0$ kVA, $M_t = 3$ , $M_t \cdot P_{cell} = -28.8$ kW; b) $P_{ac} = 0$ kW, $Q_{ac} = 100$ kVAr, $M_t = 2$ , $M_t \cdot P_{cell} = -31.2$ kW. (k=u,v,w) 99 |

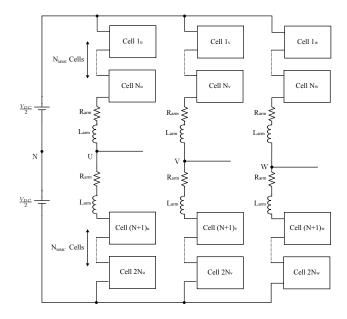

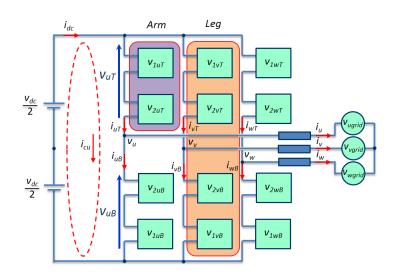

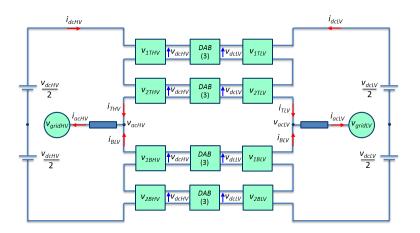

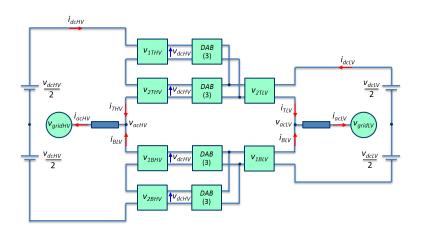

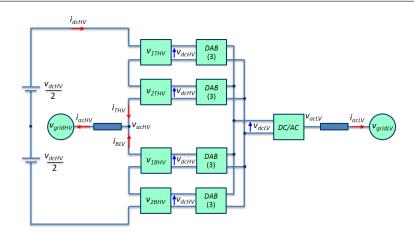

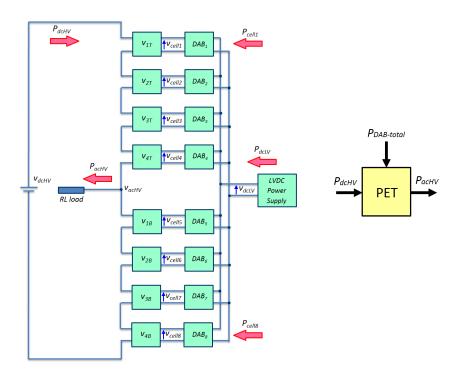

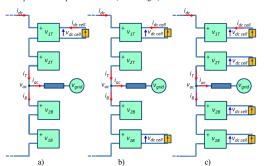

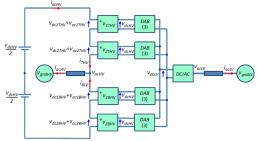

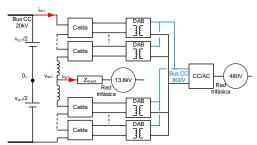

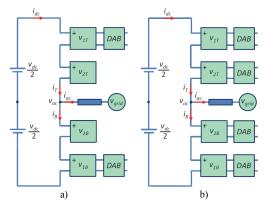

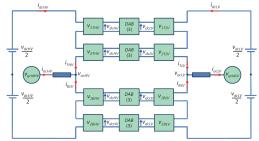

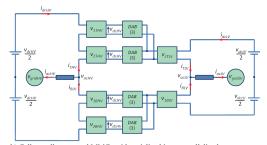

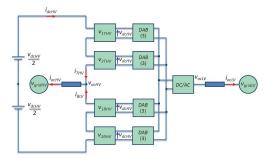

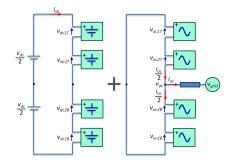

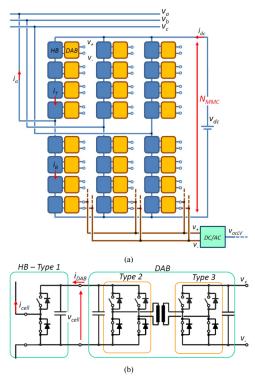

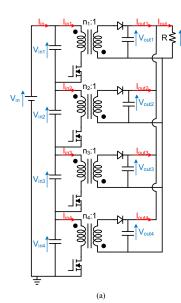

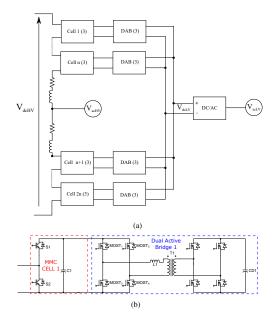

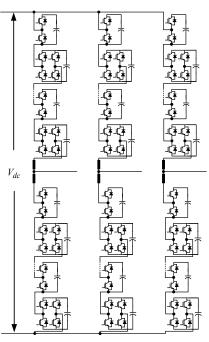

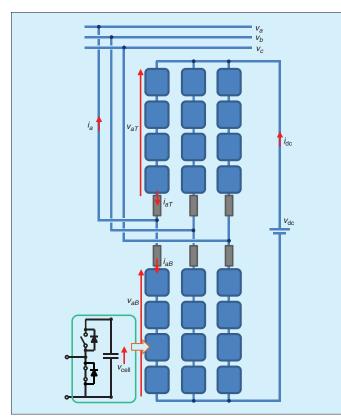

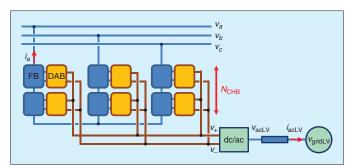

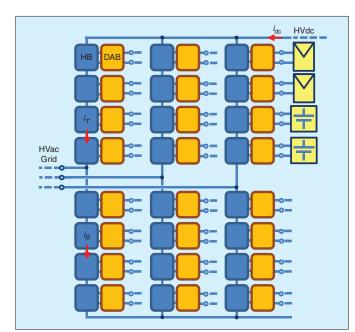

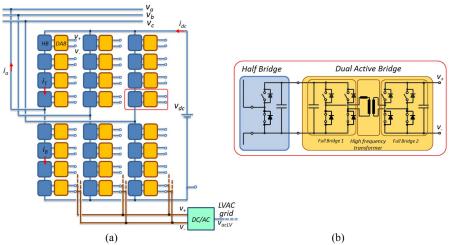

| 4.16 | MMC-based multiport power converter. Cell-to-cell connected<br>MMCs with symmetric primary and secondary (serialized input-<br>serialized output)                                                                                                                                                                                                                                                               |

| 4.17 | MMC-based multiport power converter. Cell-to-cell connected<br>MMCs with serialized input-parallelized output 100                                                                                                                                                                                                                                                                                               |

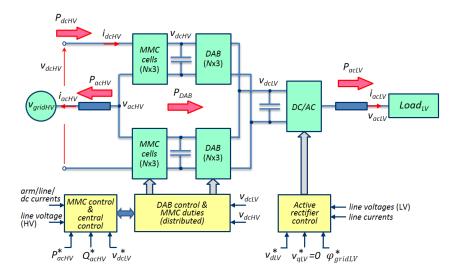

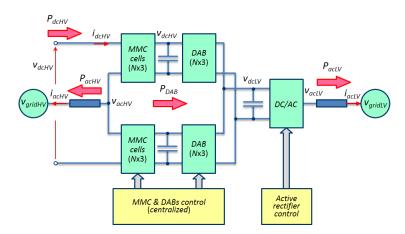

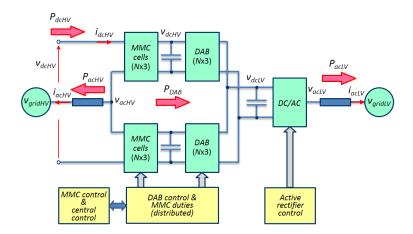

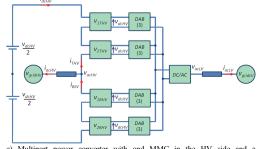

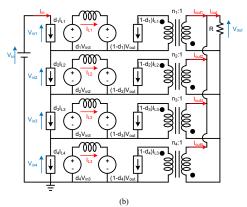

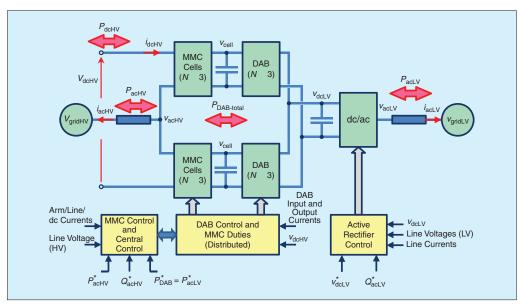

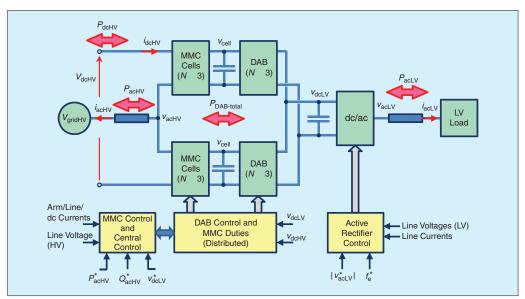

| 4.18 | Multiport power converter with and MMC in the HV side and a conventional AC/DC power converter in the LV side 101                                                                                                                                                                                                                                                                                               |

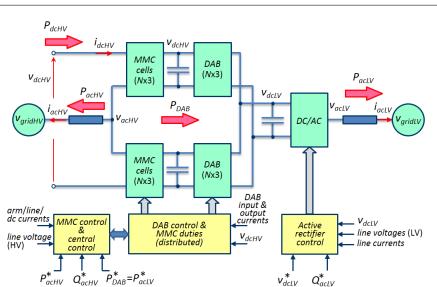

| 4.19 | Schematic representation of <i>grid feeding</i> control structure of<br>a MMC-based multiport power converter. Variables with su-<br>perscript" * " indicate commanded values                                                                                                                                                                                                                                   |

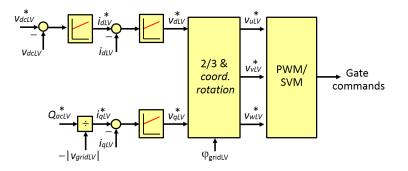

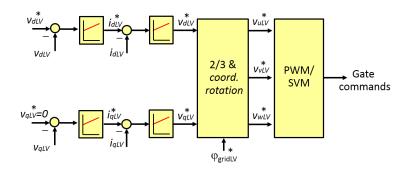

| 4.20 | Control scheme of the active rectifier for the case of a <i>grid</i><br><i>feeding</i> configuration of the MMC-based multiport power con-<br>verter                                                                                                                                                                                                                                                            |

| 4.21 | Schematic representation of <i>grid forming</i> control structure<br>of a MMC-based multiport power converter. Variables with<br>superscript " * " indicate commanded values 104                                                                                                                                                                                                                                |

| 4.22 | Control scheme of the active rectifier for the <i>grid forming</i> control structure of a MMC-based multiport power converter. 105                                                                                                                                                                                                                                                                              |

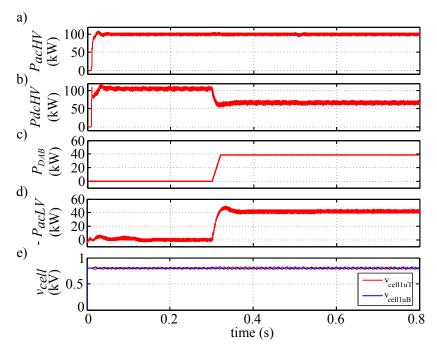

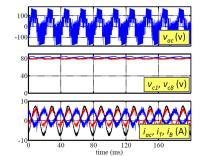

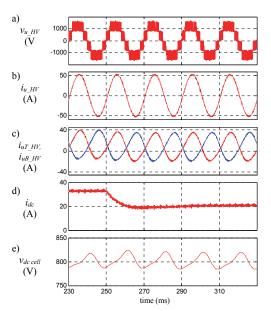

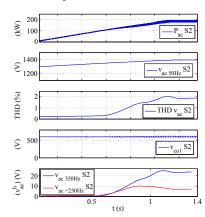

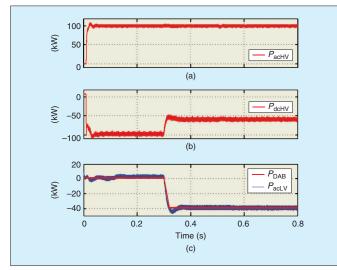

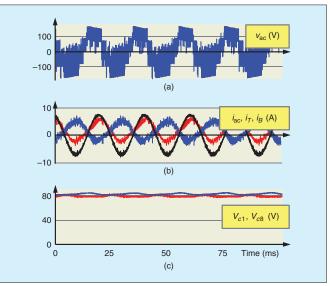

| 4.23 | Simulation results. <i>Grid feeding</i> control structure in MMC-<br>based multiport power converter. a) Active power in the<br>HVAC port. b) Power in the DC port. c) Total power in-<br>jected by the DABs. d) Active power in the LVAC port. e)<br>Capacitor voltage of a cell in the top and bottom arms 106                                                                                                |

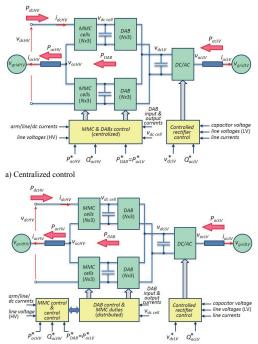

| 4.24 | Implementation of the <i>centralized control</i>                                                                                                                                                                    | 107  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.25 | Implementation of the <i>distributed control.</i>                                                                                                                                                                   | 108  |

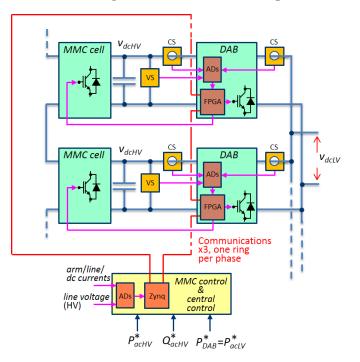

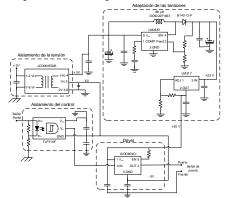

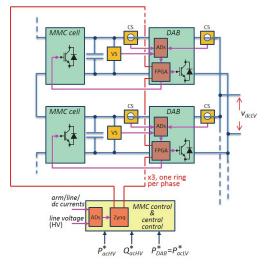

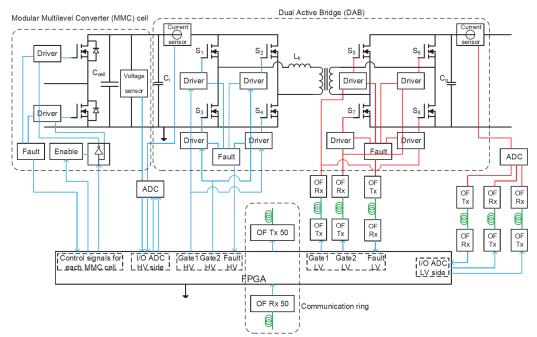

| 4.26 | Detailed overview of the distributed control under <i>Grid feed-</i><br><i>ing</i> strategy. VS and CS stand for voltage sensor and current<br>sensor respectively                                                  | 110  |

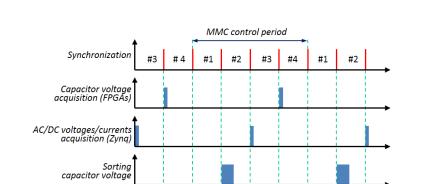

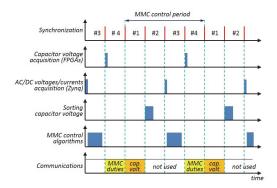

| 4.27 | Timing diagram showing the different tasks needed for the MMC-based multiport converter <i>distributed control</i> system, including communications                                                                 | 112  |

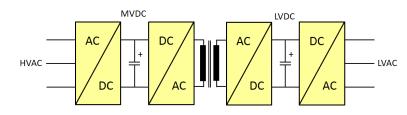

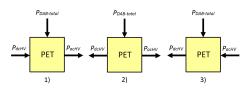

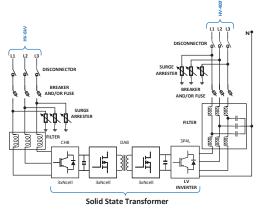

| 4.28 | Three-stage SST/PET topology.                                                                                                                                                                                       | 113  |

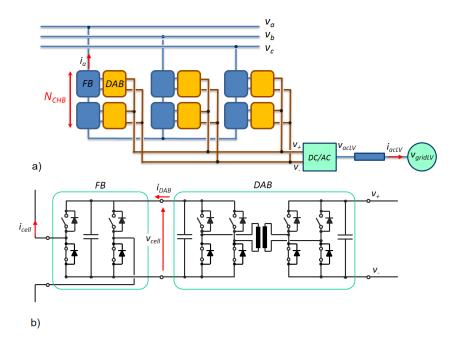

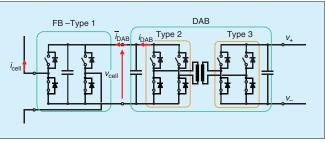

| 4.29 | a) 3-phase CHB-based PET. b) Submodule including the full-bridge (FB) and the Dual Active Bridge (DAB) converter                                                                                                    | 114  |

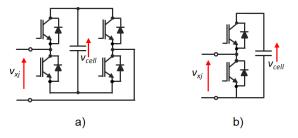

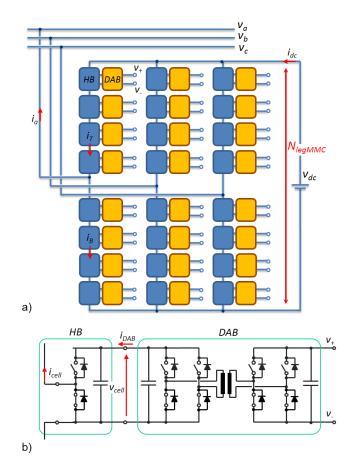

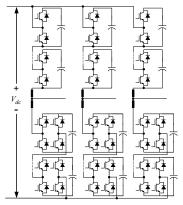

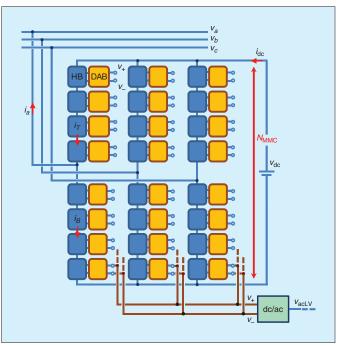

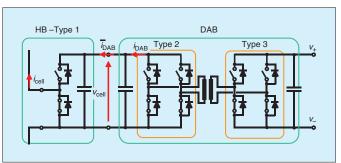

| 4.30 | a) 3-phase MMC-based PET. LV-side outputs of the DAB $(V_+, V)$ are connected as in Fig. 4.29 (not shown for the shake of clarity). b) Submodule including the half-bridge (HB) and the DAB converter               | 115  |

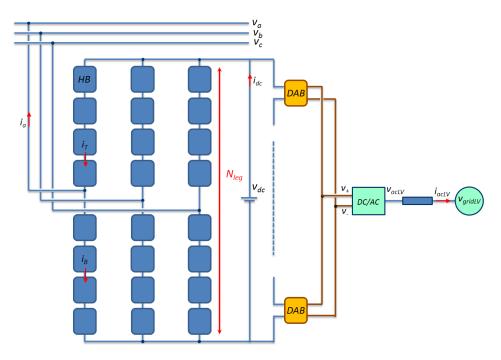

| 4.31 | 3-phase MMC-based PET with the DABs connected to the HV-DC link.                                                                                                                                                    | 116  |

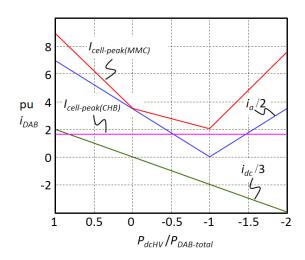

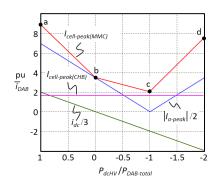

| 4.32 | MMC-based and CHB-based PETs devices peak current as a function of $P_{dcHV}/P_{DAB-total}$ , with $P_{DAB-total}$ equal to its rated value. Currents are shown in pu of the DAB average current.                   | 120  |

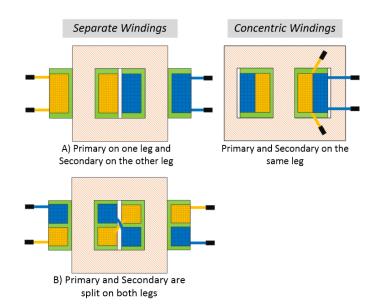

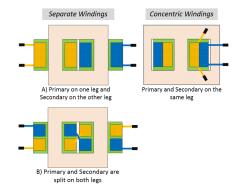

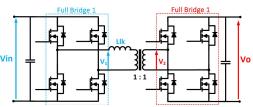

| 4.33 | HF transformer coil arrangements. Left- Separate windings,<br>Right-Concentric windings                                                                                                                             | 121  |

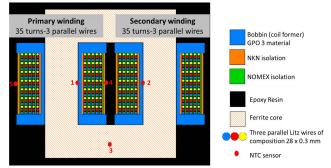

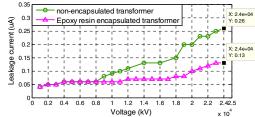

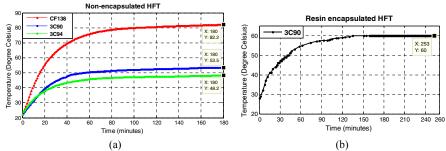

| 4.34 | Schematic representation of HF transformer for the base case [108]                                                                                                                                                  | 122  |

| A.1  | MMC half bridge cell.                                                                                                                                                                                               | 138  |

| A.2  | Eight cells, single-phase MMC prototype                                                                                                                                                                             | 138  |

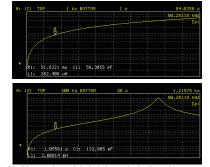

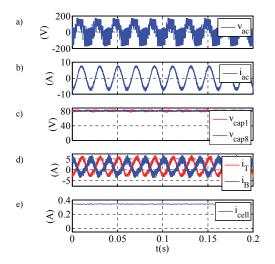

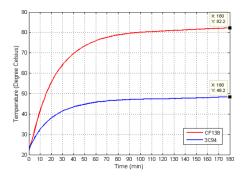

| A.3  | Magnitude of the $2\omega_e$ component of circulating current $i_c$ and<br>a capacitor voltage $v_{cap1}$ , for four different control strategies.<br>The magnitudes are in % of the worst case (direct modulation) | .139 |

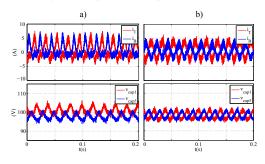

| A.4  | Top, bottom arm currents $i_T, i_B$ and capacitor voltages from<br>top and bottom arms $v_{cap1}, v_{cap5}$ under two different control<br>strategies. a) Direct modulation. b) $i_{cDC} + 2\omega_e$               | 140  |

| A.5  | Eight cells, three-phase MMC prototype. Cells (left) and backplane (right)                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

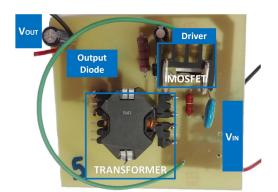

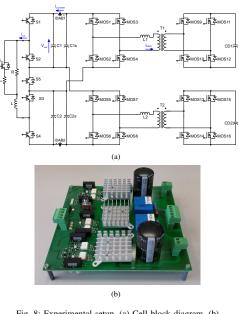

| A.6  | Dual Active Bridge (DAB) converter                                                                                                                                                                                            |

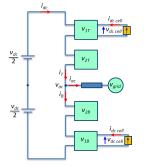

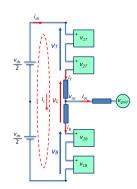

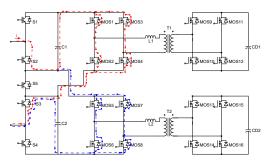

| A.7  | Left- Schematic representation of one phase of the MMC-<br>based multiport power converter developed as experimental<br>setup. Right- Power flow directions in the converter 142                                              |

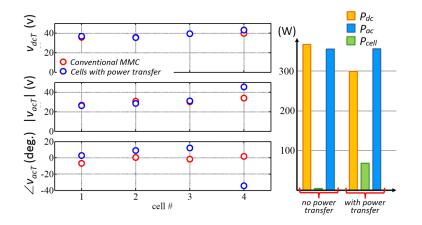

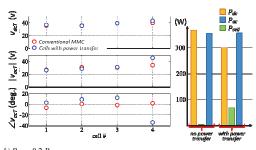

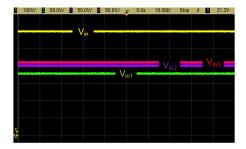

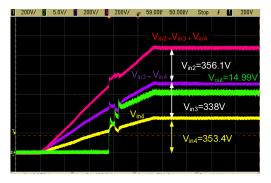

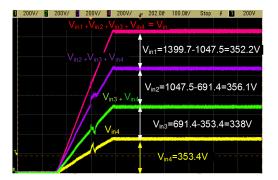

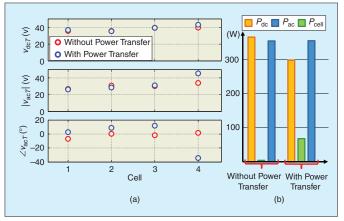

| A.8  | Left- DC and AC component of cell voltages for cells #1 to<br>#4 when $P_{DAB-total} = 0$ and $P_{cell1} + P_{cell8} = P_{DAB-total} = 0.2P_{acHV}$ . Right- DC, AC and cell powers without/with cell<br>power transfer       |

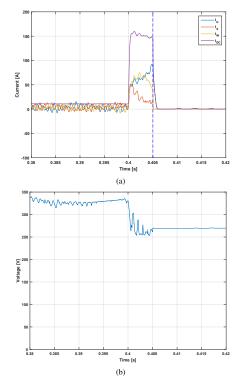

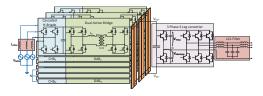

| A.9  | Top- MMC-based Multiport Power Converter experimental<br>prototype. Bottom- Individual cell: MMC half bridge + DAB. 144                                                                                                       |

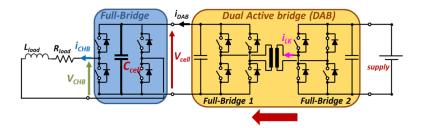

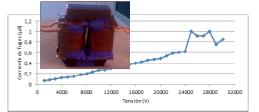

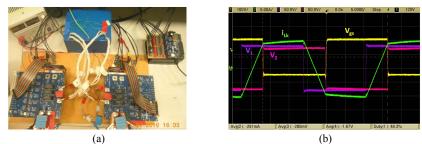

| A.10 | Left- CHB-based PET cell consisting of Full-bridge + DAB.<br>Right- CHB-based PET experimental setup                                                                                                                          |

| A.11 | Cell connections for the experimental verification. Power is<br>transferred from the DAB to the CHB cell (i.e. from LV to<br>HV port). An RL load is connected to the output of the CHB<br>full bridge to dissipate the power |

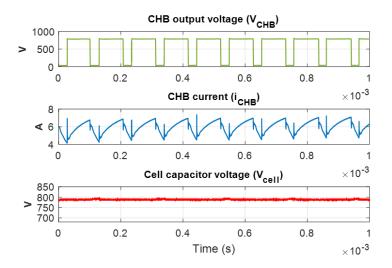

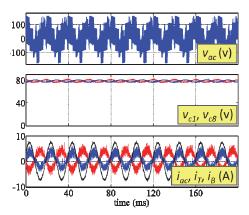

| A.12 | CHB full-bridge current and voltage waveform. The DAB controls iDAB to a target valued received from the central control. CHB full-bridge controls $V_{cell}$ to its target value of 800 V                                    |

| A.13 | DAB waveforms during experimental test                                                                                                                                                                                        |

## List of Tables

| 2.1 | Switching states 3-level NPC converter                                                                                       |

|-----|------------------------------------------------------------------------------------------------------------------------------|

| 2.2 | Switching states 5-level NPC converter                                                                                       |

| 2.3 | Switching states 3-level Flying Capacitor Converter 15                                                                       |

| 2.4 | Switching states 5-level FC converter                                                                                        |

| 2.5 | Switching states 5-level CHB converter. Phase u 19                                                                           |

| 3.1 | Arm inductances and cell capacitances reported in the liter-<br>ature                                                        |

| 3.2 | Modulation strategies and carriers disposition                                                                               |

| 4.1 | Types of asymmetry and effects on the AC port depending<br>on the applied cell voltage imbalance                             |

| 4.2 | Power Transfer Modes (Topology in Fig. 4.8-d)                                                                                |

| 4.3 | DC voltage imbalance                                                                                                         |

| 4.4 | Simulation results. AC voltage imbalance                                                                                     |

| 4.5 | Centralized vs. Distributed Control: Input-Output require-<br>ments of the central control. <i>Grid feeding</i> strategy 109 |

| 4.6 | AC and DC ports voltage                                                                                                      |

| 4.7 | Sizing analysis for three different PET topologies $\ldots \ldots \ldots 118$                                                |

| 4.8 | High-frequency transformer theoretical design parameters $[108]123$                                                          |

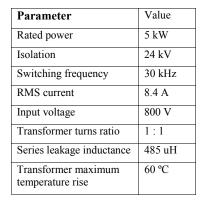

| A.1 | Experimental setups summary      |

|-----|----------------------------------|

| A.2 | MMC experimental setup           |

| A.3 | DAB experimental setup           |

| A.4 | CHB-based PET experimental setup |

## Chapter 1

## Introduction

#### 1.1 Background

The current energy scenario is suffering from a deep change. Reducing the dependence on conventional fossil fuels has become a priority for industrialized countries due to environmental concerns, limited resources and the progressive increase of their cost. This scenario has lead the governments to assign large resources in the seek for cleaner and cheaper energy sources as well as the maximum efficiency in every energy conversion process.

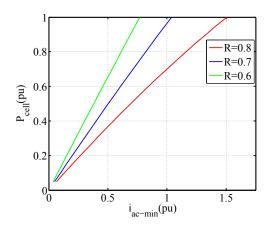

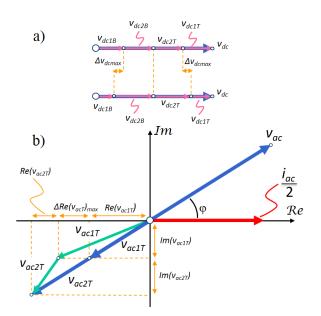

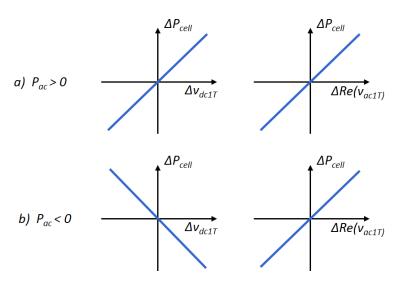

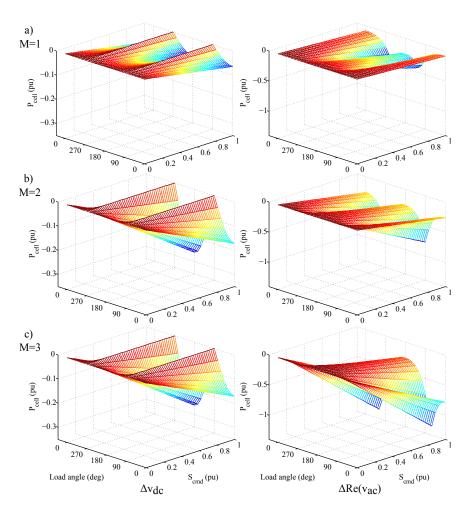

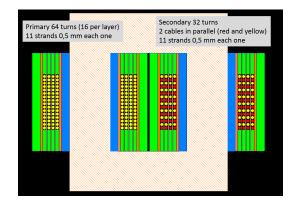

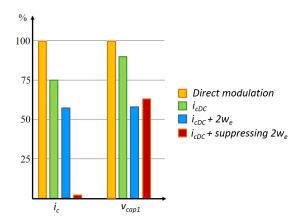

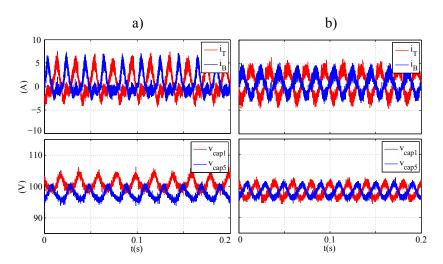

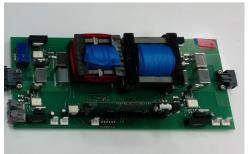

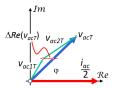

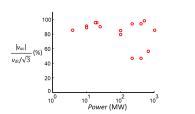

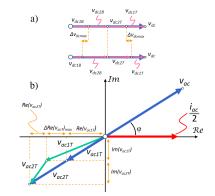

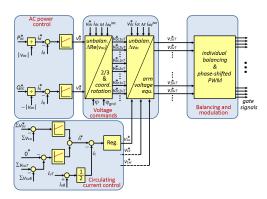

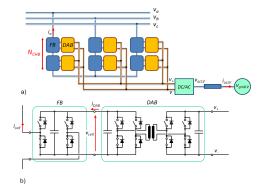

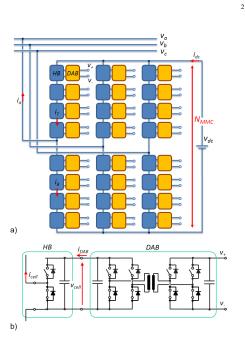

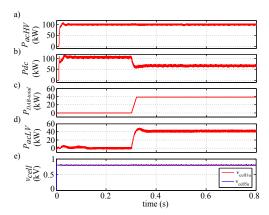

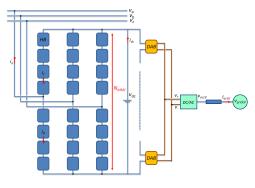

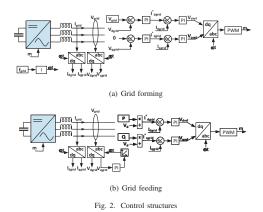

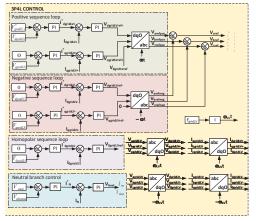

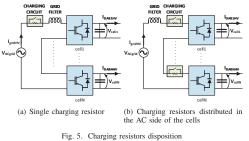

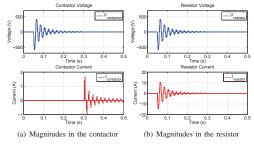

The increasing penetration of renewable energies, as well as more demanding requirements in terms of efficiency and reliability in the electrical network leads to a big challenge, as a significant part of the installed capacity will be connected to the distribution levels in the near future.