#### School of Industrial Engineering

Department of Electrical Engineering, Electronics, Computers, and Systems

PhD Thesis:

## Bringing Automated Formal Verification to PLC Program Development

A Thesis submitted by Borja Fernández Adiego for the degree of Doctor of Philosophy in the University of Oviedo

Supervised by: Dr. Víctor Manuel González Suárez Dr. Enrique Blanco Viñuela

A mis abuelos Alberto y Fernando.

"Yes, there are two paths you can go by, but in the long run, there's still time to change the road you're on." Led Zeppelin, Stairway to Heaven (1971)

## Summary

Automation is the field of engineering that deals with the development of control systems for operating systems such as industrial processes, railways, machinery or aircraft without human intervention. In most of the cases, a failure in these control systems can cause a disaster in terms of economic losses, environmental damages or human losses.

For that reason, providing safe, reliable and robust control systems is a first priority goal for control engineers. Ideally, control engineers should be able to guarantee that both software and hardware fulfill the design requirements. This is an enormous challenge in which industry and academia have been working and making progresses in the last decades.

This thesis focuses on one particular type of control systems that operates industrial processes, the PLC (Programmable Logic Controller) - based control systems. Moreover it targets one of the main challenges for these systems, guaranteeing that PLC programs are compliant with their specifications.

Traditionally in industry, PLC programs are checked using testing techniques. Testing consists in checking the requirements on the real system. Although these testing techniques have achieved good results in different kind of systems, they have some well-known drawbacks such as the difficulty to check safety and liveness properties (e.g. ensuring a forbidden output value combination should never occur).

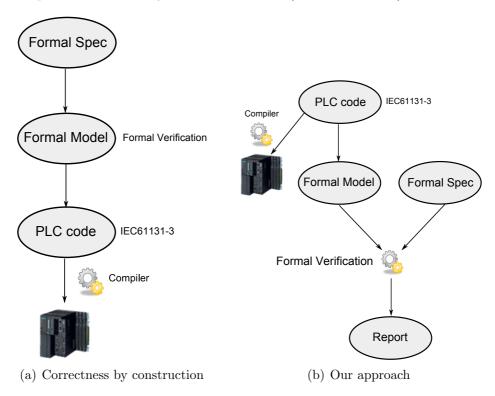

This thesis proposes an alternative for checking PLC programs. A methodology based on formal verification techniques, which can complement the testing techniques to guarantee that a PLC program is compliant with the specifications.

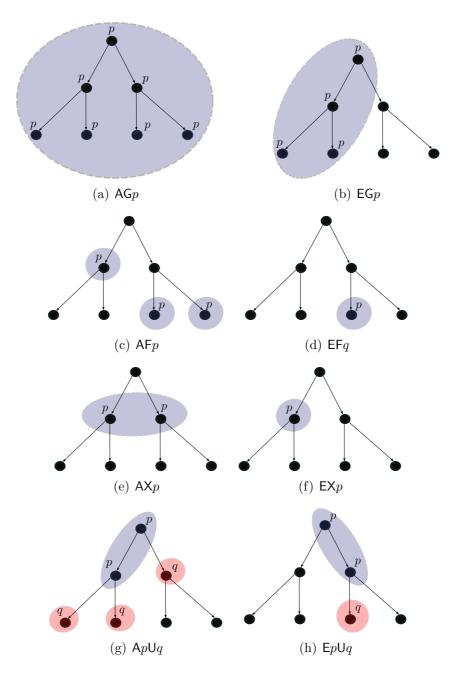

Formal verification is a technique meant to prove the correctness of a system by using formal methods. One of the most popular formal verification techniques is model checking, which consist in checking a formalized requirement in a formal model of the system. Comparing model checking with testing, model checking explores all the possible combinations of the state space in the formal model to guarantee that the formal requirement is satisfied.

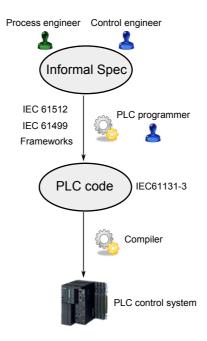

Formal verification and in particular model checking appears to be a very appropriate technique for this goal. However, the industrial automation community has not adopted yet this approach to verify PLC code, even if some standards, like the IEC 61508 (2010), highly recommend the use of formal methods for Safety Instrumented Systems. This is due to following challenges for control engineers: (1) the difficulty of building formal models representing real-life PLC programs, (2) the difficulty of using specification formalisms to express the requirements and finally, (3) when creating formal models out of real-life software, the number of combinations can be huge and model checking tools may not be able to handle the state space, thus cannot evaluate the given requirement.

This research deals with these three main challenges and tries to fill the gap between the industrial automation and the formal verification communities.

The thesis proposes a general methodology for applying automated formal verification to PLC programs and any complexity related to formal methods is hidden from control engineers.

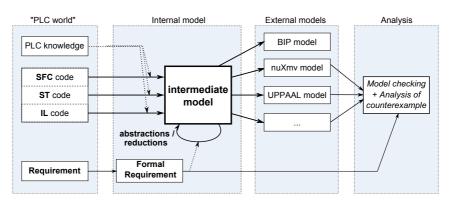

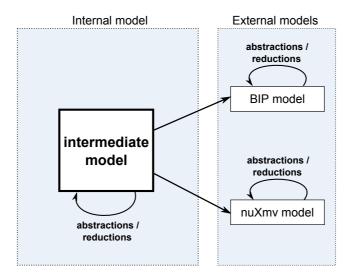

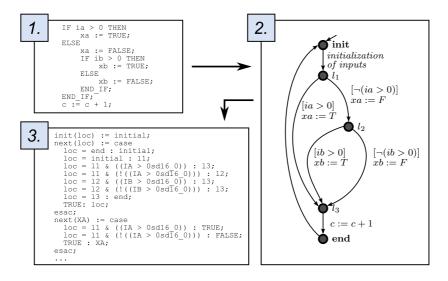

In this methodology, formal models are built automatically out of the PLC programs. The model transformations are divided in two parts: PLC programs, from the IEC 61131 (2013) standard, are translated to an Intermediate Model (IM), which is the central piece of this methodology. The IM is then transformed to the input modeling languages of different verification tools (e.g. nuXmv, UPPAAL or BIP). This modeling strategy simplifies the model transformations and makes the integration of new verification tools easier.

Regarding the requirements formalization, this methodology provides a solution that allows control engineers to express the requirements in a simple and natural language based on patterns with welldefined semantics. Then, these requirements are translated to temporal logic formalisms as they are the most common formalisms used by the verification tools.

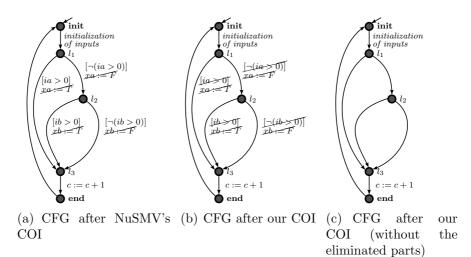

Regarding the state space explosion problem, this methodology provides a set of reduction and abstraction techniques that are applied to the IM. These techniques are a fundamental part of the methodology, as they make the verification of real-life PLC programs, which usually have huge state spaces, possible.

The methodology has been applied to real-life PLC programs developed at CERN. These experimental results have demonstrated the usability of this methodology by control engineers with no experience in formal methods.

## Resumen

Automatización industrial es el campo de la ingeniería que se dedica al desarrollo de sistemas de control para operar sistemas como procesos industriales, trenes, maquinaria o aviones sin intervención humana. En la mayoría de los casos, un fallo en estos sistemas de control puede provocar un desastre en términos de pérdidas económicas, daños medioambientales o pérdidas humanas.

Por esa razón, proporcionar sistemas de control seguros, fiables y robustos es un objetivo de primera prioridad para los ingenieros de control. Idealmente, ingenieros de control deberían de ser capaces de garantizar que tanto el hardware como el software satisfacen los requisitos del diseño. Esto es un gran reto en el cual industria y academia han estado trabajando y haciendo progresos en las últimas décadas.

Esta tesis se centra en un tipo particular de sistemas de control que opera procesos industriales, los sistemas de control basados en PLCs (Programmable Logic Controller) y tiene como meta uno de los principales retos para estos sistemas, garantizar los programas del PLC respetan las especificaciones de diseño.

Tradicionalmente en industria, los programas de PLCs son comprobados utilizando técnicas de testeo. Testear un sistema consiste en comprobar los requisitos del diseño en el sistema real. Aunque estas técnicas han logrado buenos resultados en diferentes tipos de sistemas, tiene algunas limitaciones bien conocidas, como son la dificultad de testear propiedades de seguridad o "liveness" (por ejemplo asegurar que un valor prohibido de una variable de salida nunca ocurra en el sistema).

Esta tesis propone una alternativa para chequear programas de los PLCs. Una metodología basada en técnicas de verificación formal, las cuales pueden complementar las técnicas de testeo para garantizar que el programa del PLC respeta sus especificaciones. Verificación formal es una técnica que tiene por objetivo probar que un sistema está correctamente diseñado o implementado utilizando métodos formales. Una de las técnicas de verificación formal más populares es "model checking", la cual consiste en comprobar que un requisito formalizado es respetado en un modelo formal del sistema real. Comparando model checking con las técnicas de testeo, model checking explora todas las posibles combinaciones en el modelo formal para garantizar que el modelo respeta el requisito formalizado.

Técnicas de verificación formal y en particular model checking, parecen ser técnicas muy apropiadas para el objetivo de esta tesis. Sin embargo, la comunidad de automatización industrial no ha adoptado aún estas técnicas para verificar el código de los PLCs, incluso si estándares como el IEC 61508 (2010) recomiendan el uso de métodos formales para sistemas de seguridad. Esto es debido a tres factores fundamentales: (1) la dificultad de construir los modelos formales que representan programas de PLC, (2) la dificultad de usar los formalismos para especificar los requisitos del sistemas y finalmente, (3) cuando se crea un modelo formal de un software real, el número de combinaciones posibles a explorar puede ser enorme y las herramientas que implementan model checking pueden no ser capaces de explorar el espacio de estados, por lo tanto no pueden evaluar los requisitos dados.

Este trabajo de investigación se centra en estos tres aspectos e intenta cubrir la grieta que existe en las comunidades científicas de automatización industrial y verificación formal.

La tesis propone una metodología para aplicar automáticamente (sin intervención humana) técnicas de verificación formal a programas PLC y toda complejidad relacionada con métodos formales está oculta para los ingenieros de control.

En esta metodología, modelos formales son generados a partir de los programas PLC. La transformación de modelos está dividida en dos partes: los programas PLC, definidos en el estándar IEC 61131 (2013), son traducidos a un modelo intermedio, referenciado como IM en todo el documento por sus siglas en Inglés (Intermediate model). Este modelo intermedio es la pieza central de esta metodología. Más tarde, el IM es transformado en los modelos necesarios para las diferentes herramientas de verificación (por ejemplo, nuXmv, UPPAAL o BIP). Esta estrategia de modelado simplifica las transformaciones entre modelos y hace mucho más sencilla la integración de nuevas herramientas de verificación.

En cuanto la formalización de los requisitos que el programa debe cumplir, esta metodología proporciona una solución que permite a los ingenieros de control expresar los requisitos con un lenguaje natural y sencillo basado en el uso de patrones con una semántica bien definida. Más tarde, estos requisitos son traducidos a lógica temporal, ya es que el formalismo más utilizado por las herramientas de verificación formal.

En cuanto al problema de la explosión del espacio de estados, esta metodología proporciona un conjunto de técnicas de reducción y de abstracción de modelos, las cuales son aplicadas al IM. Estas técnicas son una pieza fundamental de la metodología, ya que hace posible la verificación formal de programas PLC que controlan sistemas industriales reales, los cuales normalmente tiene un espacio de estados enorme.

La metodología ha sido empleada en programas PLC reales desarrollados en el CERN. Los resultados experimentales han demostrado la utilidad de esta metodología, usada por ingenieros de control sin experiencia en métodos formales.

## Contents

| Su       | ımma  | ary           |                                      | $\mathbf{v}$ |

|----------|-------|---------------|--------------------------------------|--------------|

| Re       | esum  | $\mathbf{en}$ |                                      | ix           |

| Ac       | cknov | wledge        | ments                                | xvii         |

| 1        | Intr  | oducti        | on                                   | 1            |

|          | 1.1   | Contex        | xt                                   | . 3          |

|          | 1.2   | Motiva        | ation and objectives                 | . 5          |

|          | 1.3   | Contri        | butions of this thesis               | . 6          |

|          | 1.4   | Public        | ations linked to this thesis         | . 8          |

|          | 1.5   | Docum         | nent structure                       | . 10         |

| <b>2</b> | Bac   | kgrour        | nd and related work                  | 13           |

|          | 2.1   | Introd        | uction                               | . 13         |

|          | 2.2   | PLC-b         | based control systems                | . 14         |

|          |       | 2.2.1         | Control system classification        |              |

|          |       | 2.2.2         | Standards                            | . 17         |

|          |       | 2.2.3         | Frameworks                           | . 19         |

|          |       | 2.2.4         | PLC hardware                         | . 23         |

|          |       | 2.2.5         | PLC software                         | . 25         |

|          | 2.3   | Forma         | l methods and formal verification    | . 32         |

|          |       | 2.3.1         | Formal methods                       | . 32         |

|          |       | 2.3.2         | Formal verification                  | . 35         |

|          |       | 2.3.3         | Model checking                       | . 37         |

|          |       | 2.3.4         | Verification tools                   | . 44         |

|          | 2.4   | Relate        | d work                               | . 45         |

|          |       | 2.4.1         | Testing-based techniques             | . 46         |

|          |       | 2.4.2         | Formal verification based techniques | . 47         |

#### Contents

|   | 2.5  | Summary of the chapter                                            | 56  |

|---|------|-------------------------------------------------------------------|-----|

| 3 | App  | proach                                                            | 59  |

|   | 3.1  | Introduction                                                      | 59  |

|   | 3.2  | General overview of the approach                                  | 62  |

|   | 3.3  | Intermediate model                                                | 70  |

|   |      | 3.3.1 Intermediate model syntax                                   | 70  |

|   |      | 3.3.2 Intermediate model semantics                                | 71  |

|   | 3.4  | Formal specifications                                             | 73  |

|   |      | 3.4.1 Patterns                                                    | 75  |

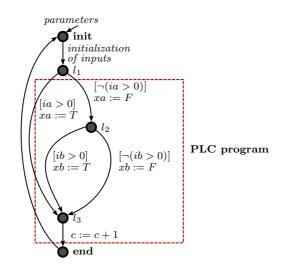

|   | 3.5  | PLC hardware modeling                                             | 79  |

|   |      | 3.5.1 PLC inputs                                                  | 80  |

|   |      | 3.5.2 Safety and Standard PLCs                                    | 82  |

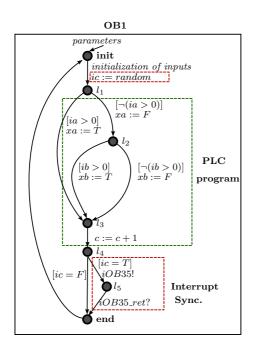

|   |      | 3.5.3 Interrupts and restarts in PLCs                             | 82  |

|   | 3.6  | PLC code – $IM$ transformation                                    | 83  |

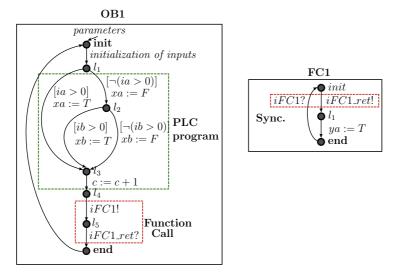

|   |      | 3.6.1 General PLC – IM transformation                             | 84  |

|   |      | 3.6.2 ST – IM transformation $\ldots \ldots \ldots \ldots \ldots$ | 89  |

|   |      | 3.6.3 SFC – IM transformation                                     | 93  |

|   | 3.7  | Reduction techniques                                              | 94  |

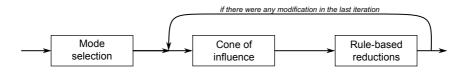

|   |      | 3.7.1 Cone of influence                                           | 98  |

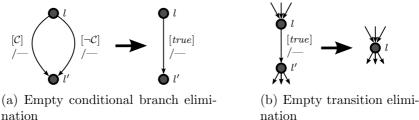

|   |      | 3.7.2 Rule-based reductions                                       | 104 |

|   |      |                                                                   | 107 |

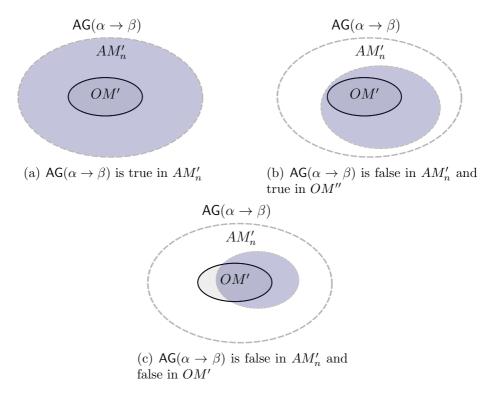

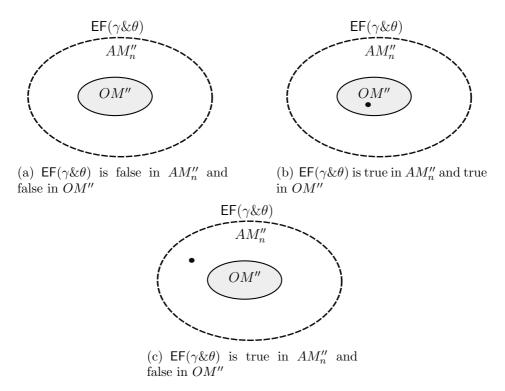

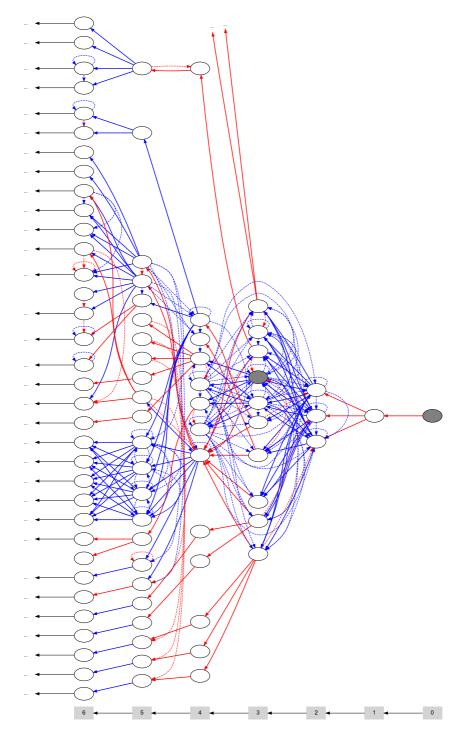

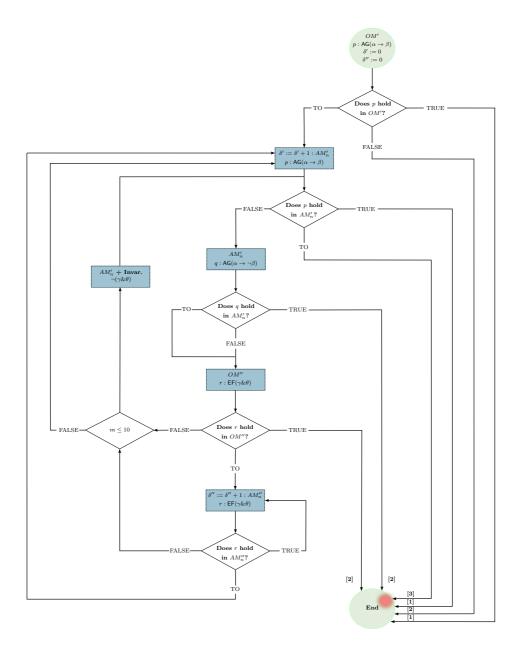

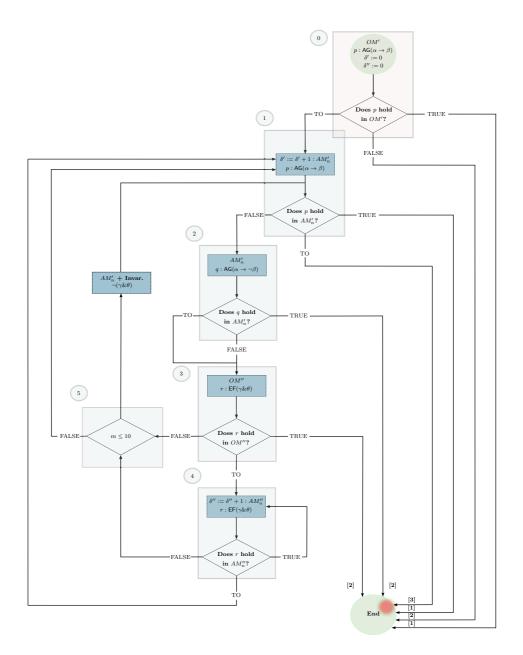

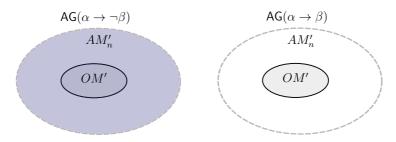

|   |      | 3.7.4 Iterative variable abstraction                              | 108 |

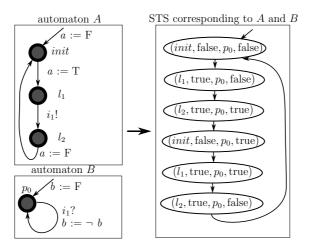

|   | 3.8  | IM– verification tools transformation                             | 130 |

|   |      | 3.8.1 IM–nuXmv transformation                                     | 130 |

|   |      | 3.8.2 IM–UPPAAL transformation                                    | 137 |

|   |      | 3.8.3 IM–BIP transformation                                       | 148 |

|   | 3.9  | Modeling timing aspects of PLCs                                   | 160 |

|   |      | 3.9.1 Realistic approach                                          | 161 |

|   |      | 3.9.2 Abstract approach                                           | 169 |

|   |      | 3.9.3 Refinement between the two approaches                       | 172 |

|   | 3.10 | Process modeling                                                  | 174 |

|   | 3.11 | Verification and counterexample analysis                          | 177 |

|   |      | 3.11.1 Counterexample analysis                                    | 178 |

|   | 3.12 | Methodology CASE tool                                             | 181 |

|   | 3.13 | Summary of the chapter                                            | 182 |

|   |      |                                                                   |     |

xiv

#### Contents

| 4        | Case | e studies and measurements 18                                                                                                         | 85  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | 4.1  | Introduction                                                                                                                          | 85  |

|          | 4.2  | UNICOS framework                                                                                                                      | 86  |

|          | 4.3  | UNICOS baseline object case study                                                                                                     | .91 |

|          |      | 4.3.1 Object description and specification 1                                                                                          | .91 |

|          |      | 4.3.2 Experimental results regarding model generation 1                                                                               | 92  |

|          |      | 4.3.3 Experimental results regarding verification of                                                                                  |     |

|          |      | complex properties                                                                                                                    | 99  |

|          |      | 4.3.4 Experimental results regarding verification of                                                                                  |     |

|          |      | time properties $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$                                                           | 201 |

|          |      | 4.3.5 Counterexample analysis $\ldots \ldots \ldots \ldots 2$                                                                         | 205 |

|          | 4.4  | Full UNICOS application case study 2                                                                                                  | 208 |

|          |      | 4.4.1 Process description and specification 2                                                                                         | 208 |

|          |      | 4.4.2 Experimental results regarding verification of                                                                                  |     |

|          |      | safety properties $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$                                                                | 209 |

|          | 4.5  | Summary of the chapter                                                                                                                | 217 |

| <b>5</b> | Eval | luation and analysis 2                                                                                                                | 19  |

|          | 5.1  | Introduction                                                                                                                          | 219 |

|          | 5.2  | Evaluation of requirements formalization                                                                                              | 220 |

|          | 5.3  | Evaluation of PLC hardware and process modeling 2                                                                                     | 222 |

|          | 5.4  | Evaluation of the PLC program – IM transformation $\therefore 2$                                                                      | 224 |

|          |      | 5.4.1 Evaluation of the time-related transformation                                                                                   |     |

|          |      | rules $\ldots$ $\ldots$ $2$                                                                                                           | 226 |

|          | 5.5  | Evaluation of the reduction techniques                                                                                                | 227 |

|          |      | 5.5.1 Property preserving reduction techniques 2                                                                                      | 228 |

|          |      | 5.5.2 State space $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$                                                  | 228 |

|          |      | 5.5.3 Verification run-time $\ldots \ldots \ldots \ldots \ldots \ldots 2$                                                             | 229 |

|          |      |                                                                                                                                       | 230 |

|          | 5.6  | Evaluation of the IM – verification tools transformation 2                                                                            | 232 |

|          | 5.7  |                                                                                                                                       | 234 |

|          | 5.8  | Correctness of our approach                                                                                                           | 235 |

|          | 5.9  | Summary of the chapter                                                                                                                | 236 |

| 6        | Con  | clusions and future work 23                                                                                                           | 39  |

|          | 6.1  | Discussion                                                                                                                            | 239 |

|          | 6.2  | Contributions                                                                                                                         | 241 |

|          |      | $6.2.1 Methodology \dots \dots$ | 241 |

|               |                          | 6.2.2   | IM syntax and semantics                                  | 241  |

|---------------|--------------------------|---------|----------------------------------------------------------|------|

|               |                          | 6.2.3   | <i>PLC code - IM</i> transformation rules                | 242  |

|               |                          | 6.2.4   | <i>IM- input verification tools</i> transformation rules | 242  |

|               |                          | 6.2.5   | Reduction techniques                                     | 242  |

|               |                          | 6.2.6   | Modeling the timing aspects of PLCs                      | 243  |

|               |                          | 6.2.7   | PLC behavior analysis                                    | 243  |

|               |                          | 6.2.8   | Applicability on CERN control systems                    | 244  |

|               | 6.3                      | Future  | e work                                                   | 245  |

| 7             | Cor                      | nclusio | nes y trabajo futuro                                     | 249  |

|               | 7.1                      | Discus  | sión                                                     | 249  |

|               | 7.2                      | Contri  | ibuciones                                                | 251  |

|               |                          | 7.2.1   | Metodología                                              | 251  |

|               |                          | 7.2.2   | Sintaxis y semántica del IM                              | 252  |

|               |                          | 7.2.3   | Reglas de transformación $c \acute{o} digo \ PLC$ - $IM$ | 252  |

|               |                          | 7.2.4   | Reglas de transformación IM- modelo para las             |      |

|               |                          |         | herramientas de verificación                             | 252  |

|               |                          | 7.2.5   | Técnicas de reducción                                    | 253  |

|               |                          | 7.2.6   | Modelado de los aspectos temporales de los PLC           | s253 |

|               |                          | 7.2.7   | Análisis del funcionamiento de un PLC                    | 254  |

|               |                          | 7.2.8   | Aplicación en sistemas de control desarrollados          |      |

|               |                          |         | en el CERN                                               | 254  |

|               | 7.3                      | Future  | e work                                                   | 256  |

| $\mathbf{A}$  | PLO                      | C prog  | rams                                                     | 259  |

| в             | nuX                      | Kmv m   | odels                                                    | 277  |

| $\mathbf{Li}$ | st of                    | Acron   | iyms                                                     | 325  |

| $\mathbf{Li}$ | ${ m st} { m d}\epsilon$ | e Figur | es                                                       | 329  |

| $\mathbf{Li}$ | st of                    | Table   | 8                                                        | 333  |

|               |                          |         |                                                          |      |

| $\mathbf{Li}$ | st of                    | Listin  | gs                                                       | 335  |

| Bi            | bliog                    | graphy  |                                                          | 337  |

# Acknowledgements

This part of the thesis is certainly the most important one for me, as it allows me to thank and express my appreciation to some of the people who have helped me during the years of my PhD candidature.

I would like to start with my supervisors Enrique Blanco Vinũela and Víctor Manuel González Suárez, who gave me the opportunity to work with them during all these years. I am extremely grateful for their wise advice in the scientific and technological aspects of this research.

To all my colleagues from the EN-ICE group at CERN and specially to Philippe Gayet, who gave me the opportunity to be part of this group.

To my colleague Daniel Darvas, who worked with me in this project for the past one and a half years, for his high quality work and the constructive discussions. I am very pleased that Daniel will continue and complement this research during his PhD candidature.

To my colleague Jean-Charles Tournier for his support on the initial idea of this thesis and for the interesting brainstorming and discussions during the last three years.

To my colleague Luis Gómez Palacín, for his help and good advices during the last two years at CERN.

To my colleague Iván Prieto Barreiro, from whom I have learned a lot about different programming languages and with whom I had the pleasure to work closely during my first two years at CERN

To all my colleagues from the PLC section at CERN, from whom I have learned a lot during all these years and for the great moments I have shared with them in coffee breaks, dinners, etc.

To Effhymia Laderi from CERN and Gemma Hernández Redondo from the Oviedo University for their patience and help on adminis-

#### trative matters.

To all the members of the RiSD laboratory directed by Prof. Joseph Sifakis at the EPFL University in Lausanne (Switzerland), especially to Simon Bliudze from whom I have learned a lot about formal methods and formal verification.

To András Vörös and Tamás Bartha from the BUTE University in Budapest (Hungary), for the interesting discussions about formal verification applied to safety critical systems.

To Jan Olaf from the RMIT University in Melbourne (Australia), for the interesting discussions about formal semantics and formal verification applied to PLC programs.

Thanks to these five years at CERN, I have met a lot of people from all over the world who are today an important part of my life. Some of these people are Borja, Guillermo, Piotr, David, Pablo, Miguel, Marc, Edu, Cris, Alberto and my friends from the basketball team.

I cannot forget my friends Kostis and Benja with whom I have shared so many great trips and moments.

Me gustaría agradecer a mi profesor y amigo Pepe, por sus consejos para mis estudios universitarios y mi carrera profesional.

A toda mi familia, por su apoyo, cariño y toda la confianza que siempre depositaron en mí. Desde los más jóvenes, Jimena, Jorge, María, Pablo y Alberto, pasando por mi hermano Adrián, hasta mis abuelos Cuca, Fernando, Mari y Alberto y mi bisabuela Abi.

A mis amigos y compañeros de universidad, entre ellos Samu, Edu, Ablanedo y Manu, con los que he compartido grandes momentos.

A mis amigos de La Bañeza, David, Edu, Javi, Ruben, Saúl e Iván, por todos los momentos compartidos, por las risas juntos y porque cualquier problema o mal rato se olvida cuando paso tiempo con ellos. A Jenny, por su cariño y paciencia conmigo, por todo su apoyo y ayuda en momentos que no fueron muy fáciles para mí.

A mis padres, a los cuales les debo todo. Cualquier persona que les hubiera tenido como padres hubiera conseguido lo mismo o mucho más de lo que yo he conseguido. Mi mayor motivación en mi carrera profesional es hacerles sentir orgullosos, para agredecerles todo su cariño y apoyo incondicional.

# Chapter 1 Introduction

In the nineteenth century, the industrial revolution provoked very significant economic and social changes in the human society. From this event until now, the development of new machines and technologies have an enormous impact on our lives. Industrial automation was created to free humans from tedious monitoring tasks in industrial processes. Since 1910, when Henry Ford automated his automobile assembly plant, industrial automation has been evolving and becoming an essential element in the development of any industry. The transformation of automation technologies, from the first electro-pneumatic devices to the complex programmable controllers existing today, shows the evolution of this industry, led by a high demand of complex and flexible control devices from other industries.

New progresses in control theory and in control technologies, such as distributed systems, have transformed industrial automation into a relevant area of research with an countless number of practical applications in any aspect of our lives.

"Overall, with more than two centuries' development and evolution, industrial control and automation technologies have so advanced that they benefit us in all aspects of our life and in all kinds of production systems; they are closely integrated with computer hardware and software, network devices and communication technologies; they are faithfully based on modern results in the mathematical and physical sciences." (Zhang (2010)).

Nowadays, one of the main needs in industrial automation is the ability of designing safe, reliable and robust control systems which are compliant with their specifications. Model-based design and verification of controllers (hardware and software) are some of the research trends in automation nowadays. Software failures in control systems can provoke enormous damages to human beings, to the environment and cause an enormous economic breakdown. One of many unfortunate examples is the software error which provoked the accident of Ariane 5 space rocket from the European Space Agency. The Ariane 5 software was previously tested.

The formal verification community provides solutions to guarantee that a system is compliant with the system specifications, using strong mathematical bases.

This thesis fills the gap between these two communities, industrial automation and formal verification, to make progress in the development of safer, more reliable and more robust control systems, by guaranteeing that the control software is compliant with the specifications. This thesis focuses on PLC (Programmable Logic Controller) – based control systems, as PLCs are the most common control devices used in industry.

It is important to mention that in the automation industry the so-called "Safety Instrumented Systems" (SIS), defined by the IEC 61511 (2003), are systems designed to protect people, environment and industrial installations. With the evolution of technologies these systems are mostly based on programmable controllers, such as PLCs. This thesis concentrates on the software of PLC control systems independently of its purpose. Obviously guaranteeing that the PLC program of a SIS is compliant with the specification is essential and highly recommended by the standards (for example, the IEC 61508) (2010) standard) but this is also desirable in any PLC control system that monitors and regulates an industrial installation. This is because as a software bug can provoke significant damages or the cost of fixing this bug is bigger than the cost of using formal methods. Moreover, nowadays industry demands high availability of industrial control systems to maximize the uptime of the controlled process, even if a bug in the code would not provoke a damage on the installation, it could imply to stop the installation with the corresponding economic losses.

This chapter is divided in the following sections:

1. Section 1.1 presents the general context of this thesis.

- 2. Section 1.2 gives an overview of the motivation for this research.

- 3. Section 1.3 enumerates the contributions of this thesis.

- 4. Section 1.4 lists the scientific publications that are the result of this research.

- 5. Finally, Section 1.5 introduces the structure of this thesis.

#### 1.1 Context

This PhD has been developed under the doctoral student program at CERN (European Organization for Nuclear Research) in collaboration with the University of Oviedo (Spain).

CERN is the biggest particle physics laboratory in the world, located at the border between France and Switzerland. CERN has four main goals:

- 1. Push forward the frontiers of knowledge in particle physics.

- 2. Develop new technologies for accelerators and detectors. Many of these technique can also be applied to other industries. The transfer of knowledge and technology is also an important goal of CERN.

- 3. Train the scientists and the engineers of tomorrow.

- 4. Unite people from different countries and cultures.

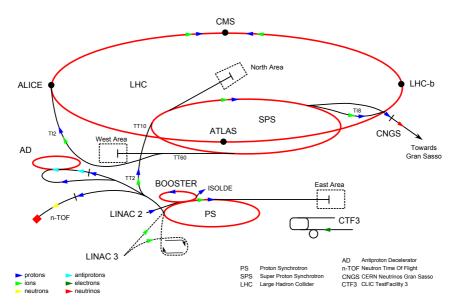

CERN has a particle accelerator complex to perform the experiments and some of these particle accelerator are: PS (Proton Synchrotron), SPS (Super Proton Synchrotron), LINACs (LINear ACcelerators) and LHC (Large Hadron Collider) (See Fig. 1.1). The LHC is the biggest particle accelerator in the world with 27 km of circumference. The goal is this machine is to recreate the conditions existing immediately after the big bang. To do that, the LHC accelerates heavy particles (e.g. protons) to a speed close to the speed of light and make them collide. These collisions, at a very high energy (14 TeV), provide a very valuable insight of the particles by observing their outcome: energies, trajectories and eventually, new particles creation. Some of them are well-known by the physicists but some others are just part of theories and it has never been proved their existence. The LHC has the goal of proving or disproving these theories, helping in the understanding of the universe. To detect these new particles the LHC has four main particle detectors (ATLAS, CMS, ALICE and LHCb).

Figure 1.1: CERN accelerator complex from http://en.wikipedia. org/wiki/CERN

Producing these high energy collisions, requires some auxiliary industrial processes (e.g. cryogenics and vacuum systems) to provide the optimized conditions for the particle accelerators and detectors. Moreover, these industrial processes have to be operated automatically, therefore they need industrial control systems. At CERN, this research was done at the ICE (Industrial Controls & Engineering) group inside the EN (Engineering) department, which develops solutions and provides support in the domain of large and medium scale industrial control systems as well as the accelerator systems.

At the Oviedo University, the thesis is supported by the ISA (System Engineering and Automation) area inside the DIEECS (Electric, Electronics, Computers and Systems Engineering) department. ISA focuses its research in the different areas of the automation field.

#### **1.2** Motivation and objectives

Nowadays any industrial installation has to be controlled and operated automatically, looking for these three main objectives:

- 1. Increasing the quality and efficiency of the process.

- 2. Enforcing the safety by reducing human interaction with the industrial process.

- 3. Reducing the costs by optimizing the energy consumption of the installation.

It is obvious that having a control system that contains flaws may cause damages and economic losses to the installation itself, but it also can affect the environment and people. Having a safe, robust and bugfree control system is a common "desire" of designers and developers involved in the project. However, producing a control system that is fully compliant with the project specifications is a very challenging task. The automation industry lacks of modern software engineering best practices to guarantee it and this research is focused on this topic.

Some standards address this problem, specially standards focused on functional safety, like the IEC 61508 (2010). This standard proposes some guidelines for the development of safety systems and their verification (more details about the standard can be found in Chapter 2).

Certainly, the most challenging task is to guarantee that the control system software is compliant with the specification. In industry, many techniques have been applied to achieve this goal, like manual and automated testing or applying simulation. However these techniques have several drawbacks, like the difficulty of checking liveness properties (e.g. "after a manual request from the operator, the valve vwill eventually be closed") or the difficulty of checking all the possible combinations of the state space in a safety property (e.g. "if valve vis closed, then valve w can never be closed at the same time").

The IEC 61508 standard recommends the use of formal methods to guarantee that the software is compliant with the specifications, specially for systems with a high Safety Integrity Level  $(SIL)^1$ , see

<sup>&</sup>lt;sup>1</sup>SIL is an integrity characteristic to measure the risk-reduction provided by a safety function in a safety instrumented system.

Table 1.1. This table appears in "Part 3: Software requirements (Table A.2, page 37)" of the IEC 61508 (2010) standard.

Table 1.1: Software design and development: software architecture design (see Table 7.4.3 from the IEC 61508 (2010) standard)

| Technique/Measure      | Ref          | SIL1 | SIL2 | SIL3          | SIL4          |

|------------------------|--------------|------|------|---------------|---------------|

| 7b Semi-formal methods | Table<br>B.7 | R    | R    | HR            | HR            |

| 7c Formal methods      | C.2.4        | _    | R    | R             | HR            |

| 8 Computer-aided       |              |      |      |               |               |

| specification tools    | B.2.4        | R    | R    | $\mathbf{HR}$ | $\mathbf{HR}$ |

| NR: Not Recommended    | 1.           |      |      |               |               |

R: Recommended.

HR: Highly Recommended.

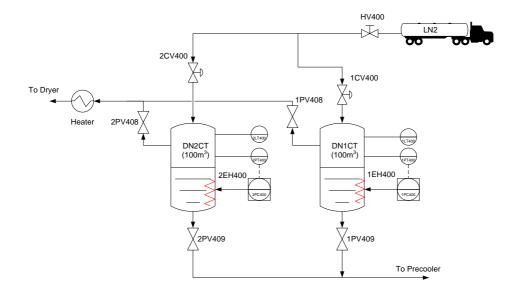

Programmable Logic Controllers are the most widely used control devices in industry for automation purposes. At CERN, many industrial installation such as the LHC cryogenic system, cooling & ventilation systems, LHC vacuum systems, etc. are controlled by PLCs (e.g. Willeman et al. (2011)). These systems are developed using the so-called UNICOS framework described in Blanco Viñuela et al. (2011).

The fundamental goal of this thesis is to provide a methodology guaranties that any PLC program is compliant with the project specifications. This methodology is based on applying automated formal verification to PLC programs, hiding the complexity from the control engineers.

#### **1.3** Contributions of this thesis

To the best of the author's knowledge, this thesis presents several contributions on the field of formal verification of PLC programs, as follows:

1. The internal behavior (informal semantics) of a PLC is described in this thesis. This description is focused on Siemens PLCs as it is one of the two PLC suppliers at CERN. This analysis, which is presented in Chapter 2, is essential to justify the decisions and the modeling strategy.

- 2. This thesis presents a general methodology for applying automated formal verification to PLC programs. The methodology is based on an Intermediate Model (IM) and PLC programs written in any PLC language from the IEC 61131 (2013) standard can be expressed in this IM. This IM can be transformed to the input modeling languages of many verification tools. In Chapter 3, the methodology is presented in Section 3.2.

- 3. The syntax and formal semantics of the IM are described. In Chapter 3, the IM is presented in Section 3.3.

- 4. As the ST and SFC languages are the most relevant languages in CERN PLC control systems, the formal transformation rules from ST and SFC to the IM are described. The rules are presented in Chapter 3, Section 3.6.

- 5. The methodology is supported by a CASE tool, which is able to generate formal models from ST and SFC PLC programming languages passing through the IM. Currently the tool generates models for the following verification tools: nuXmv Cavada et al. (2014), UPPAAL Amnell et al. (2001) and BIP Basu et al. (2011). The rules are presented in Chapter 3, Section 3.8.

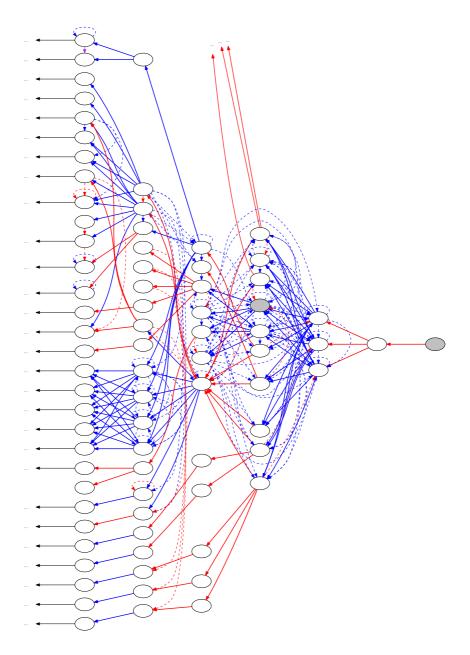

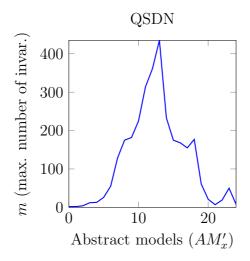

- 6. The generated models of real-life PLC programs have usually a huge state space, which cannot be verified by any of the verification tools. Reduction and abstraction techniques are applied to the intermediate model making verification of these programs feasible (including novel and existing algorithms adapted to this methodology, achieving better results than existing solutions).

- 7. Modeling time and real time systems increases the complexity of the model and the state space. The strategy of modeling the timing aspects of PLC programs is presented. These particular rules are presented in Chapter 3, Section 3.9.

8. The methodology has been applied to real-life systems at CERN, showing the feasibility and applicability of the methodology. The experimental results are presented in Chapter 4.

## 1.4 Publications linked to this thesis

The following articles were published during the development of this thesis:

- Fernández Adiego, B., Blanco Viñuela, E., and Merezhin, A. (2013a). Testing & verification of PLC code for process control. In *Proc. of 13th ICALEPCS*. This paper describes two different approaches to verify PLC programs: testing and formal verification.

- Fernández Adiego, B., Blanco Viñuela, E., Tournier, J.-C., González Suárez, V. M., and Bliudze, S. (2013b). Model-based automated testing of critical PLC programs. In 11th IEEE Int. Conf. on Industrial Informatics, pages 722–727. This paper describes a first approach of modeling UNICOS control systems in order to apply automated model-based testing.

- 3. Darvas, D., Fernández Adiego, B., and Blanco Viñuela, E. (2013). Transforming PLC programs into formal models for verification purposes. Internal Note CERN-ACC-NOTE-2013-0040, CERN. This technical report describes the first version of some of the transformation rules from PLC code to the NuSMV modeling language.

- 4. Fernández Adiego, B., Darvas, D., Tournier, J.-C., Blanco Viñuela, E., and González Suárez, V. M. (2014c). Bringing automated model checking to PLC program development – A CERN case study. In Proc. of the 12th IFAC–IEEE International Workshop on Discrete Event Systems. This paper presents a case study of applying the proposed methodology to a PLC control system developed at CERN.

- Darvas, D., Fernández Adiego, B., Vörös, A., Bartha, T., Blanco Viñuela, E., and González Suárez, V. M. (2014). Formal verification of complex properties on PLC programs. In

Ábrahám, E. and Palamidessi, C., editors, *Formal Techniques* for Distributed Objects, Components, and Systems, volume 8461 of Lecture Notes in Computer Science, pages 284–299. Springer. This paper describes the property preserving reduction techniques applied in the methodology.

- 6. Fernández Adiego, B., Darvas, D., Blanco Viñuela, E., Tournier, J.-C., González Suárez, V. M., and Blech, J. O. (2014a). Modelling and formal verification of timing aspects in large PLC programs. In *Proc. of IFAC World Congress*. This paper describes the modeling strategy of the timing aspect of PLCs.

- 7. Fernández Adiego, B., Darvas, D., Tournier, J.-C., Blanco Viñuela, E., Blech, J. O., and González Suárez, V. M. (2014b). Automated generation of formal models from ST control programs for verification purposes. Internal Note CERN-ACC-NOTE-2014-0037, CERN. This paper describes the transformation rules from ST PLC code into the modeling languages of verification tools through an intermediate model.

Before focusing my research on the formal verification of PLC programs, I studied the most relevant control system frameworks which have been applied mainly in scientific installations. In addition, the real-life PLC programs, presented in experimental results of this thesis, have been developed at CERN using the UNICOS framework. Three papers, in which I have participated, have been published about the UNICOS framework:

- Fernández Adiego, B., Blanco Viñuela, E., and Barreiro, P. (2011). UNICOS CPC6: Automated code generation for process control applications. In *Proc. of 12th ICALEPCS*. This paper describes the architecture of the automatic generation tool for UNICOS control systems.

- 2. Copy, B., Blanco Viñuela, E., Fernández Adiego, B., Nogueira Fernandes, R., and Barreiro, P. (2011). Model oriented application generation for industrial control systems. In *Proc. of* 12th ICALEPCS. This paper presents the UNICOS metamodel used as definition of the UNICOS library meant to represent control system instrumentation as UNICOS objects.

Blanco Viñuela, E., Merezhin, A., Bradu, B., Fernández Adiego, B., Willeman, D., Rochez, J., Beckers, J., Ortola Vidal, J., Durand, P., and Izquierdo Rosas, S. (2011). UNICOS evolution: CPC version 6. In *Proc. of 12th ICALEPCS*. This paper describes the new features of the CPC package from the UNICOS framework.

#### **1.5** Document structure

This thesis is organized as follows:

- **Chapter 1:** this first chapter describes the context of this thesis, presents the motivation and objectives and gives a general overview of the contributions. It also lists the publications produced out of this research.

- Chapter 2: this chapter gives an overview of the two different "worlds" linked to this research, industrial automation and formal verification. Initially, it introduces the chapter explaining the link between both fields. Then, it describes the main features related to PLC-based control systems needed to explain the proposed modeling strategy. Lately, an overview of main concepts of formal verification is introduced. Finally, the related work of formal verification applied to PLC-based control systems is presented.

- Chapter 3: this chapter presents the core of this thesis. The proposed methodology is introduced and lately the details of the different steps of the methodology are presented: formalization of requirements, system modeling, reduction techniques, verification strategy and analysis of verification results.

- Chapter 4: this chapter presents the experimental results obtained by applying the methodology on real-life CERN control systems. These systems are developed using the UNICOS framework. This framework is introduced in this chapter and the two selected systems are presented.

- Chapter 5: this chapter presents an evaluation and analysis of the obtained results.

- **Chapter 6:** this chapter concludes the thesis, summarizing the contributions and results and presenting the future work of this research.

- **Appendix A:** this appendix presents one of the real-life PLC programs, which have been verified applying the proposed methodology

- **Appendix B:** this appendix presents some of the generated nuXmv models out of the real-life PLC programs.

- Lists The thesis finishes with the list of acronyms, figures, tables and bibliography.

## Chapter 2

# Background and related work

### 2.1 Introduction

This chapter gives an overview of the relevant concepts of the two fields of study involved in this research: industrial automation and formal verification. The automation concepts are either fundamental to understand the proposed methodology for applying formal verification to PLC programs (e.g. description of hardware and software in PLCs) or relevant in the design of reliable control systems (e.g. standards or frameworks).

Automation, in general, is the use of control systems for operating different equipments such as processes in factories, aircraft, machinery, etc. reducing human intervention. Many different devices are used as control systems depending on the equipment to be controlled (e.g. digital or analog devices) and the needs of control (e.g. speed, PID regulation). Some of the most common devices are: FPGAs (Field-Programmable Gate Array), industrial PCs and PLCs. PLC is the most popular control device for industrial processes such as cooling and ventilation, oil or chemical processes. PLCs are appropriate devices for processes with both digital and analog instrumentation (e.g. digital and analog valves, temperature sensors, digital pumps, etc.) and with strong requirements in reliability under harsh environment. Section 2.2 describes the main characteristics and concepts of PLC-based control systems that have been taken into account in this research.

Formal verification is a technique meant to prove the correctness of a system by using formal methods of mathematics. Formal verification and formal methods are also introduced in this chapter. In the last two decades, these techniques have been applied successfully in many different industries such as aircraft, space shuttle, and railway systems. The related work section presents a brief overview of the applicability of these techniques in other areas. However, despite PLCs are the most common control device for safety and for standard control systems, formal verification is not really applied in this industry yet. Section 2.4 presents a detailed overview of the different techniques designed to check PLC programs and the differences with this thesis approach.

#### 2.2 PLC-based control systems

The first PLC was born in 1968, when *GM Hydramatic* asked for an alternative to replace all the hard-wired relay systems by a programmable alternative. The company *Bedford Associates* came with the wining proposal and the first PLC was created. This first prototype was called *084*. *Bedford Associates* started a new company dedicated to develop, manufacture, sell, and service this new product: *Modicon*, which is currently property of *Schneider Electrics* (Schneider Electrics automation website (2014)). One of the person who worked on that project was Dick Morley, who is considered to be the "father" of the PLC.

The PLC is the most widely-used programmable electronic device designed for controlling industrial processes. Even if other kind of controllers, such as industrial PCs, are more powerful, sophisticated and offer more alternatives in terms of programming capacities, PLCs remain the most popular control device due to its reliability and robustness in industrial environments.

A PLC mainly consists of a processing unit and peripheries to connect with sensors and actuators of the process or with other electronic devices.

This thesis is based on *Siemens* PLCs (Siemens automation website (2014)), as they are widely used at CERN. Although some minor differences exist with the models produced by other manufacturers, they all have a common PLC architecture described in the IEC 61131 (2013) standard.

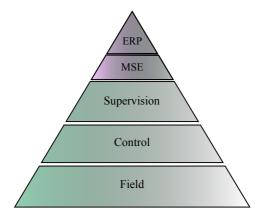

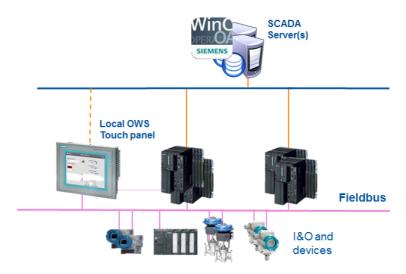

Industrial control systems are traditionally divided in three main layers:

- 1. Supervision: this layer provides the interface with the process operator. The tool is usually called SCADA (Supervisory Control and Data Acquisition). It is in charge of showing the process variables to the operator, storing their values in databases and giving access to the operator to send manual orders to the control layer.

- 2. Control: this layer is composed of the control devices (e.g. PLCs) which contain the logic to automatize the process.

- 3. Field: this layer is in contact with the process to be controlled. It is composed of sensors, which take the information from the process, and actuators, which execute the orders given by the control layer.

Note that modern control systems include more parts (layers or sub-layers) to this traditional architecture. For example MES (Manufacturing Execution System) or ERP (Enterprise Resource Planning). Fig. 2.1 shows a common representation of the control system layers.

Figure 2.1: Control system layers

#### 2.2.1 Control system classification

Independently of the use of PLCs or other control device, industrial control systems can have many different classifications based on the characteristics of the control layer: type of control applied to the process, controllers architecture, its purpose, etc.

Regarding the *control applied to the process*, an industrial control system can be classified as:

- Open-loop control system: it is a control system that only uses the current state of the input values and the program of the controller. It does not use feedback to guarantee if the output has the intended value due to the input request.

- Closed-loop control system: it is a control system that uses the current state of the input values, the program of the controller and some information from the output of the system that is returned back to the input and computed by the control program.

Regarding the *controllers architecture*, an industrial control system can be classified as:

- Centralized control system: it is a control system managed by a single controller, which contains the whole control logic.

- Distributed control system (DCS): it is a control system which is managed by more than one controller. In these systems the logic is split into different controllers. The controllers use field buses for the communication between them. The IEC 61499 (2013) standard proposes a methodology to design distributed systems based on function blocks (this concept is introduced in Section 2.2.5).

Please note that very often in industry the term DCS may refer to a distributed system in terms of the supervision layer, where different servers store the information from the industrial process in a database (usually a distributed database). Both architectures can be combined in the same control system.

Both centralized and distributed control systems can have a decentralized periphery, which uses field buses to communicate with the controllers. Some of the most common field buses are Modbus (Modbus website (2014)), Profibus and Profinet (Profibus - Profinet website (2014)).

Regarding the purpose, an industrial control system can be classified as:

- Standard control system: it is a control system dedicated to control and monitor the industrial process.

- Safety control system: it is a control system dedicated to protect people, environment and installations. They are defined by the IEC 61508 (2010) standard as SISs and their goal is to provide *Functional Safety*, which increases the reliability of the global system.

#### 2.2.2 Standards

When developing industrial control systems, the developer should follow a set of rules to guarantee certain common requirements, such as safety, maintainability or quality of control code. These rules, presented as guidelines, are given by the standards. There are several international organizations in charge of producing standards. The two more relevant organizations for the standardization in the automation discipline are:

- IEC (International Electrotechnical Commission): it is the world's leading organization that prepares and publishes international standards for all electrical, electronic and related technologies (International Electrotechnical Commission website (2014)).

- ISA (International Society of Automation): is a leading, global, nonprofit organization that prepares and publishes international standards for automation (International Society of Automation website (2014)).

Other organizations, like ISO (International Organization for Standardization website (2014)) or CENELEC (European Committee for Electrotechnical Standardization website (2014)) in Europe, are also relevant in the automation community.

Below a summary of the most relevant standards in the development or industrial control systems is presented:

- 1. IEC 61131 (2013) standard: it is a general standard for programmable controllers. It is divided into eight parts and it describes the main features of programmable controllers, such as equipment requirements, programming languages, guidelines for the application and implementations of these languages, etc. It is important to emphasize that PLC programming languages from different vendors have been developed or adapted, following the recommendations of this standard, although there are some minor differences between them. Five languages are defined by this standard, three graphical languages and two textual languages: Ladder diagram (LD), Function block diagram (FBD), Sequential function chart (SFC), Structured text (ST) and Instruction list (IL).

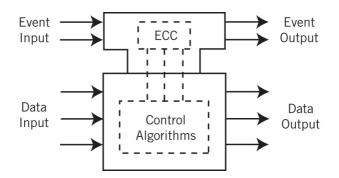

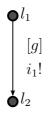

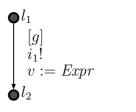

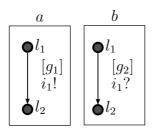

- 2. IEC 61499 (2013) standard: this standard extends the concept of function block (FB) defined in the IEC 61131 standard. The extension has the goal of improving this concept using objectoriented features. It also describes a methodology to design the control software based on these FBs. Fig. 2.2 shows the representation of the proposed FB by this standard. This FB is composed of the ECC (Execution Control Chart) and the control algorithms. The execution of these algorithms is triggered by the ECC, which is an event-driven state machine similar to the well-known Harel Statecharts.

- 3. ISA 88 (2010) standard: this standard focuses on the batch process control. It provides a methodology to design control systems for this particular case of processes, with the goal of optimizing the production in a flexible way. It is divided into four parts and it describes the applied models and terminology, the data structures, gives some recipe models and provides examples of use.

- 4. IEC 61512 (2009) standard: as the previous standard, it focuses on the batch process control. It is an extended version of the ISA 88. It proposes the creation of a hierarchy of modules to model and control the batch processes.

- 5. IEC 61508 (2010) standard: it is the standard focused on the *Functional Safety* of Electrical/Electronic/Programmable Elec-

tronic Safety-related Systems (E/E/PE, or E/E/PES). The goal of this standard is to become the reference standard in terms of functional safety to all kind of industries. It provides guidelines for all the needed steps for the development of a SIS. These steps correspond to the so-called *Safety Life Cycle*, from risk analysis to the decommissioning of the SIS.

- 6. IEC 61511 (2003) standard: it is a standard about Functional Safety as well, but focused on the industrial process. It provides the definition of safety concepts such as SIS (Safety Instrumented System), SIF (Safety Instrumented Function) and SIL (Safety Integrity Level). SIL is used to categorize the level of safety of a system and it ranges from 1 (for the lowest safety level in this category) to 4 (for the highest safety level in this category).

- 7. IEC 62061 (2012) standard: it is a specific implementation of the IEC 61508 standard for machinery as its title revels: "Safety of machinery: Functional safety of electrical, electronic and programmable electronic control systems".

Figure 2.2: IEC 61499 FB representation

## 2.2.3 Frameworks

On the top of the standards, several companies and organizations have developed some "frameworks", with the goal of homogenizing and standardizing the control systems even more. Many control system frameworks can be found in the literature, mostly the ones developed by research organizations (e.g. CERN, ESRF, etc.) and universities as private companies usually do not publish this knowledge. These frameworks standardize many different aspects of the control systems such as communication protocols, data storage, control code, SCADA visualization, etc. Some of the advantages for using these frameworks are:

- It reduces the development time, as they usually provide some tools dedicated to solve repetitive tasks, for example code generation tools.

- It improves and simplifies the maintenance of the control systems due to the standardization.

- It reduces the chances of having software errors when the framework provides a solution to standardize the control code, due to the reusability of software blocks (e.g. FBs).

As this thesis has been developed at CERN, some of the most relevant control system frameworks applied to big scientific installations are presented in this section. These frameworks are: EPICS, TANGO, FESA and UNICOS.

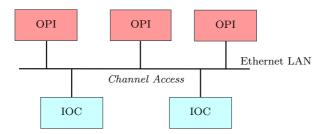

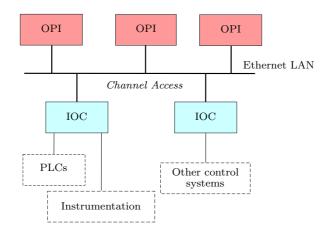

## 2.2.3.1 EPICS

EPICS (Experimental Physics and Industrial Controls) is a control system framework co-developed by the "Accelerator technology" control group at Los Alamos (Accelerator and Operations Technology website (2014)) and by the "Advanced Photon Source" control group at the Argonne National Laboratory (Advanced Photon Source website (2014)) in USA. This framework was born to provide a solution for control and supervision in big scientific installations, as the control needs of these installation were not available in industry. EPICS provides a standard solution for the communication between the control and supervision layers in distributed systems. Fig. 2.3 shows the EPICS architecture, which is based on a *Client – Server* model. The communication is based on the "Channel Access" protocol. The first documentation about its architecture can be found in Dalesio et al. (1991). It also provides a set of tools for the control systems developers. They are called the EPICS subsystems (alarm manager, display manager, etc.) and the *OPI* (Operator Interface) consists in workstations where the EPICS subsystems are executed. The *IOC* (Input-Output Controllers) supports real time databases. The hardware is based on VME/VXI systems using VxWorks or RTEMS operating systems.

Figure 2.3: EPICS architecture

In addition EPICS uses a distributed database providing local control for each IOC. It provides data acquisition, data conversion, alarm detection and control closed loops. It provides a timing system for the events synchronization along the network. As it is shown in Fig. 2.4, different control devices can be connected to the IOCs, e.g. PLCs, FPGAs, etc.

Figure 2.4: EPICS control system example

EPICS is used in more than 100 different projects all over the world, mainly in big scientific installations (e.g. DESY website

(2014)). More information about EPICS can be found on the EPICS website (2014).

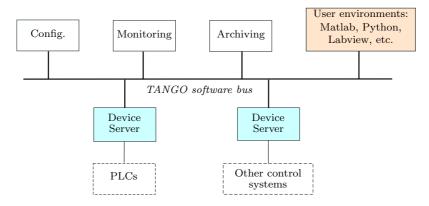

#### 2.2.3.2 TANGO

TANGO is the European alternative to EPICS. It was developed initially by the control group of ESRF (ESRF website (2014)), and currently more research centers collaborate on the development (e.g. ALBA website (2014)). Nowadays these institutes constitute the TANGO consortium (TANGO website (2014)), which provides a standard solution for the communication between the different elements of the system as it is shown in Fig. 2.5. It was designed for distributed control systems and it uses the object oriented paradigm based on CORBA (CORBA website (2014)). It provides a set of tools for the development of "device servers". These elements provide access to all the elements of the control system. Thanks to the consortium, it is possible to develop "devices servers" and "clients" in different languages, like C++, Java or Python. In addition, TANGO provides several APIs (Application Programming Interface) for the development of these elements. Hardware can range from simple digital input/outputs up to sophisticated detector systems or entire plant control systems. More information about TANGO can be found in Chaize et al. (1999).

Figure 2.5: TANGO architecture

#### 2.2.3.3 FESA

FESA (Front-End Software Architecture) is an object oriented framework, developed at CERN by the BE/CO group CERN BE/CO group website (2014). It generates automatically code for the control layer, which is based on industrial PCs called FECs (Front End Computers). It provides a set of tools for design, development and test of real time software. At the SCADA level, Java applications have been developed to monitor the information from the FECs. At the control level, the so-called FESA classes represent real devices from the instrumentation of the control system. It also provides a *Timing system* for the synchronization along the network. The LHC control system at CERN is mainly based on FESA. Other scientific institutes started to use FESA, for example, GSI (GSI website (2014)). More information about FESA can be found in Peryt and Martín Marquez (2009).

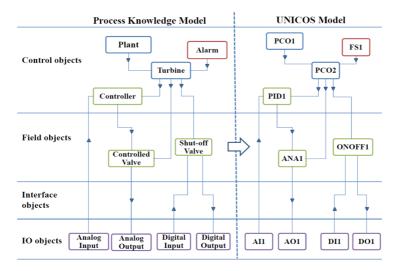

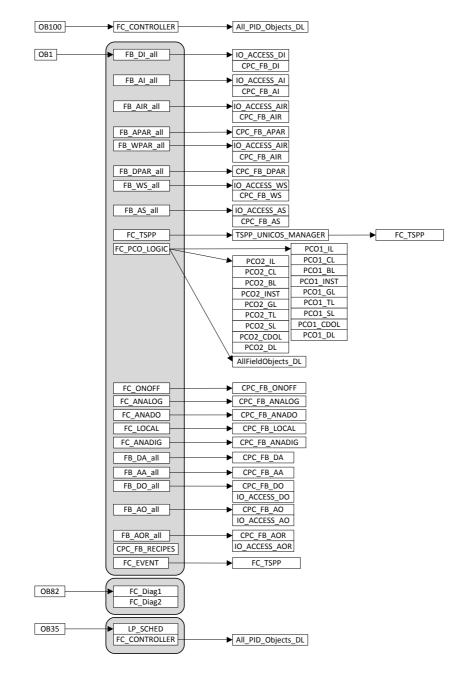

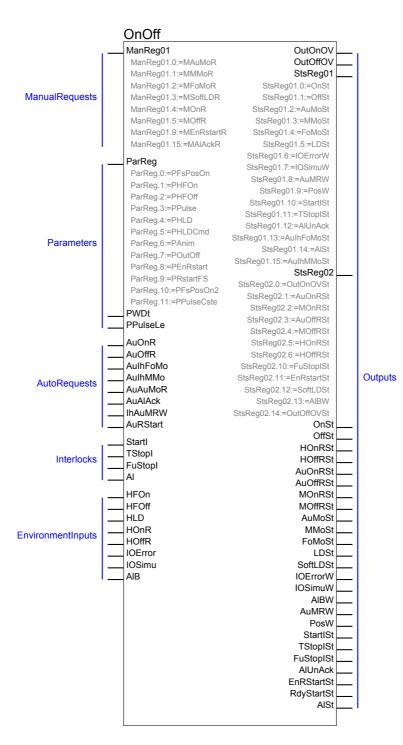

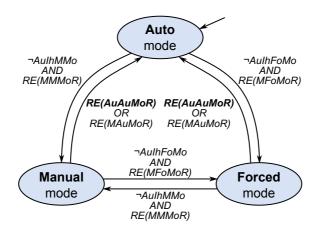

#### 2.2.3.4 UNICOS

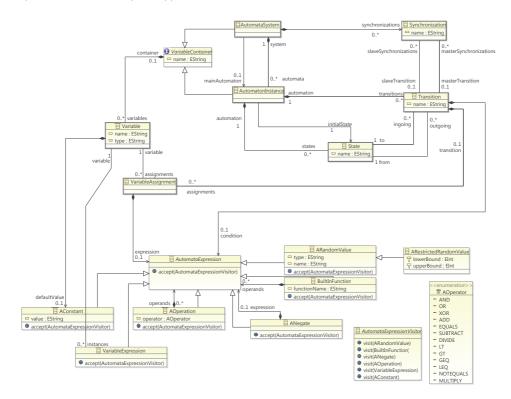

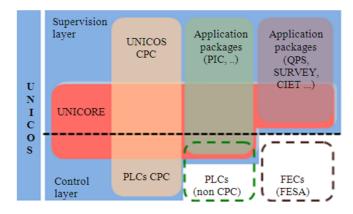

UNICOS (UNified Industrial COntrol System) is a industrial control framework developed at CERN by the EN/ICE group (CERN EN/ICE group website (2014)). This framework provides a methodology and a set of tools to develop industrial control systems. The experiments presented in Chapter 4 use PLC programs from the UNICOS library and PLC programs developed using this framework. Therefore, this framework is described in detail in Section 4.2.

Control system frameworks are important in this research as they contribute to produce more reliable control systems. However, none of the described frameworks include the use of formal methods in their development process yet. More general information about control system frameworks can be found in Lopez (2006).

## 2.2.4 PLC hardware

This section describes the main characteristics of the PLC hardware. The concepts presented in this section are fundamental to understand the modeling strategy of the PLC execution platform.

## 2.2.4.1 Execution schema

The main particularity of the PLC is its execution scheme, the socalled *scan cycle*. It consists of three main steps:

- 1. Reading the inputs from periphery to the *Input Image Memory* (IIM).

- 2. Executing the user program that reads and modifies the *Output Image Memory* (OIM) contents.

- 3. Writing the values to the output periphery.

The PLC reads the information coming from the process (sensors and actuators) and stores it either in the IIM or the OIM. The IIM values are frozen during the execution of the user program.

The execution of the scan cycle can be interrupted if an event (e.g. timer, hardware event, hardware error) triggers the execution of an interrupt handler. The interrupts are preemptive and they are assigned to priority classes in compilation time that will determine their priority.

## 2.2.4.2 PLC memory

The "data memory" of a PLC is divided into different areas depending of its purpose. The memory can be divided into two main parts (Siemens (1998a); Siemens AG (2010)).

- 1. One part of the memory is globally accessible and allocated statically. This part stores the image of the input and output values, and the internal computation results.

- 2. The rest of the memory is only accessible locally and is allocated dynamically. The so-called L Stack is in this part and it stores the temporary data of functions, separately for each priority class.

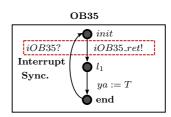

## 2.2.4.3 PLC interrupts and restarts

PLC interrupts are described by the IEC 61131 standard. In Siemens PLCs, interrupts trigger the call of Organization Blocks (OBs), which

are the interfaces between the operating system and the PLC program. They have different priorities and therefore a higher priority OB can interrupt any lower priority OB. Restarts are a special case of interrupts and they trigger a specific OB as well.

There are different kind of interrupts in Siemens PLCs, some of the main examples are:

- Time-of-day interrupts (OB10..17). These interrupts are triggered at a specific time on each day or month.

- Cyclic interrupts (OB30..38). These interrupts are triggered cyclically with a defined cyclic time.

- Hardware interrupts (OB40..47). These interrupts are triggered by hardware events (e.g. errors, diagnostics, etc.).

- Startup (OB100..102). These interrupts are triggered when a PLC restart occurs.

## 2.2.5 PLC software

The third part of the IEC 61131 (2013) standard describes the different software resources, which are necessary to build the user program in PLCs. However, there are some minor differences between the implementations provided by the PLC vendors. The following paragraphs describes the PLC resources given by Siemens PLCs.

## 2.2.5.1 PLC blocks

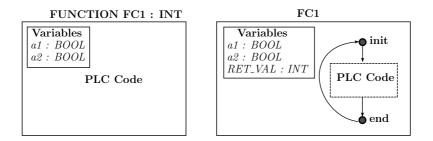

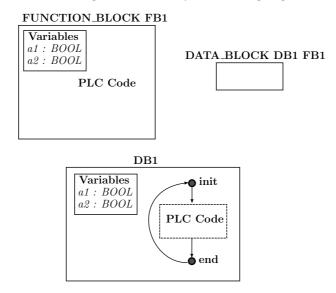

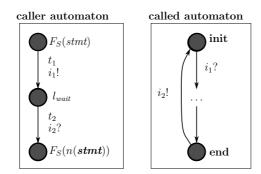

In Siemens PLCs, several kinds of program blocks are defined for various purposes Siemens AG (2010).

- A function (FC) is a piece of executable code with input, output and temporary variables. The variables are stored on the L Stack and they are deleted after the execution of the function.

- An organization block (OB) is a special function that can be only called by the system. These are the entry points of the user code. The main program and the interrupt handlers are implemented as OBs.

- A data block (DB) is a collection of static variables that can be accessed globally in the program. These variables are stored permanently. The data block does not contain any executable code.

- A function block (FB) is a piece of executable code with input, output, static and temporary variables. Static variables are stored in *instance data blocks* and these variables can be accessed globally, even before or after the execution of the FB. The temporary variables are stored on the L Stack, similarly to the FC's variables.

#### 2.2.5.2 Programming

There are five PLC languages defined by the IEC 61131 (2013) standard: *ST*, *SFC*, *Ladder*, *FBD* and *IL*. The PLC programmer can chose one or several of these languages, depending on the characteristics of the application, to build the PLC code.

ST is the most used PLC programming language at CERN. However SFC and IL are also used:

- ST is a textual high-level language that is syntactically similar to Pascal.

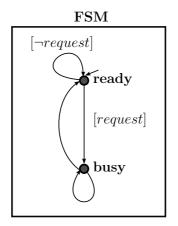

- The SFC language is a graphical programming language based on steps and transitions. It is useful when a part of the PLC program can be conveniently represented as a finite-state machine (FSM).

- The IL language is a low level language that is syntactically similar to assembly.

- The FBD language is a graphical language based on logic gates.

- The Ladder language is a graphical language based on electric circuit diagrams of relay logic hardware.

All these languages are compiled to a common byte code called MC7 and this is the code transferred to the PLC. The MC7 instructions are assumed to be atomic and they cannot be interrupted. A

single ST or SFC statement can correspond to several MC7 instructions.

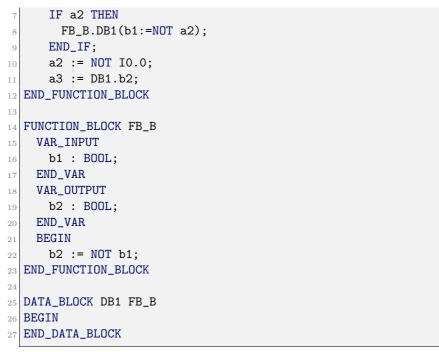

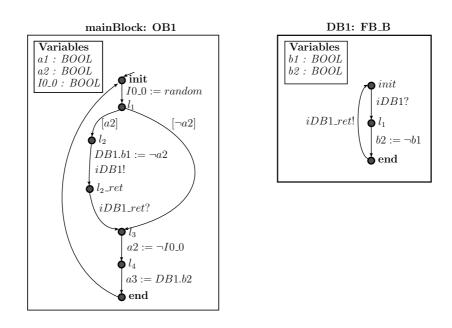

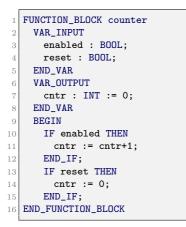

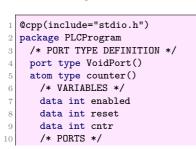

Listing 2.1 shows an example ST code. This example code defines a function block (FB100) with three variables (a, b, c). There is an instance data block (DB1) defined for FB100. In the organization block OB1, the FB100 is called using the instance data block DB1 with input parameter a=false. Then the c variable of this instance is assigned to the output Q1.0.

```

FUNCTION_BLOCK FB100

1

VAR INPUT

2

a : BOOL;

3

END_VAR

4

5

VAR_TEMP

6

b : BOOL;

7

END_VAR

8

VAR

9

c : BOOL;

END_VAR

BEGIN

b := NOT a;

13

c := b;

END_FUNCTION_BLOCK

14

DATA_BLOCK DB1 FB100

16

17

BEGIN

18 END_DATA_BLOCK

19

20 ORGANIZATION_BLOCK OB1

21

VAR_TEMP

info : ARRAY[0..19] OF BYTE; // reserved

22

END_VAR

23

24

BEGIN

25

FB100.DB1(a := FALSE);

Q1.0 := DB1.c;

26

END_ORGANIZATION_BLOCK

27

```

Listing 2.1: Example of ST code

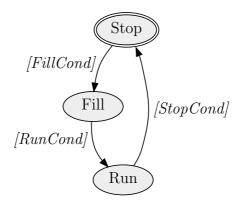

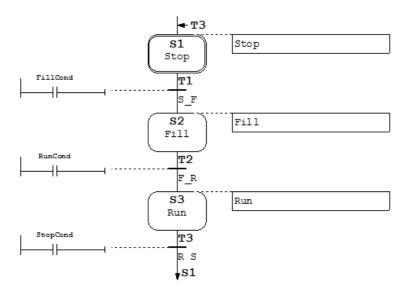

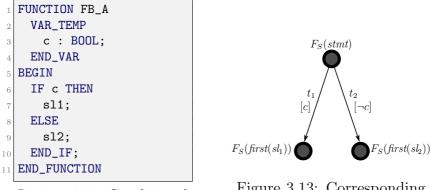

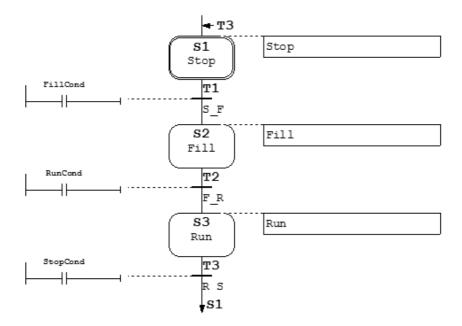

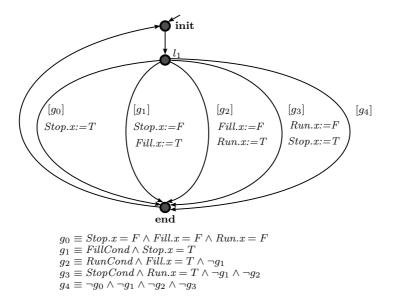

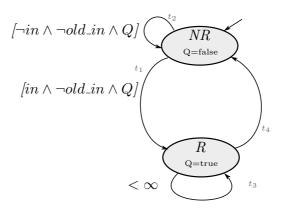

Listing 2.2 shows an example SFC code. It defines a FSM with three states (*Stop*, *Fill*, *Run*) with three possible transitions. The conditions of the transitions are Boolean input variables (*StopCond*, *FillCond*, *RunCond*) and their value is assigned outside of the FSM-representing function block. The graphical representations can be seen in Fig. 2.6 and Fig. 2.7 (this last representation corresponds with screenshot of the SIMATIC tool of Siemens).

```

1 FUNCTION_BLOCK FB101

2 VAR_INPUT

```

```

FillCond : BOOL := FALSE;

3

RunCond : BOOL := FALSE;

4

StopCond : BOOL := FALSE;

5

END_VAR

6

7

INITIAL_STEP Stop: END_STEP

8

STEP Fill: END_STEP

9

STEP Run: END_STEP

11

TRANSITION S_F

12

FROM Stop TO Fill CONDITION := FillCond

13

END_TRANSITION

14

TRANSITION F R

16

FROM Fill TO Run CONDITION := RunCond

17

END_TRANSITION

18

19

TRANSITION R_S

20

FROM Run TO Stop CONDITION := StopCond

21

END_TRANSITION

23 END_FUNCTION_BLOCK

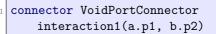

```

Listing 2.2: Example of the textual representation of SFC code

Figure 2.6: Example SFC

## 2.2.5.3 Timing behavior of PLCs

PLC control systems can perform timing operations and these operations are very common when controlling industrial processes. Un-

Figure 2.7: Example SFC (Screenshot from SIMATIC tool by Siemens)

derstanding the behavior of these operations is essential to justify the proposed modeling strategy.

In standard PLCs, the cycle time is not fixed, but there is an upper limit surveyed by a *watchdog* module. If the PLC cycle time gets longer than this upper limit, e.g. due to an infinite loop in the PLC program, the PLC executes a special part of the program responsible for handling timing errors. By contrast, safety PLCs have a fixed cycle time in order to avoid dangerous situations.

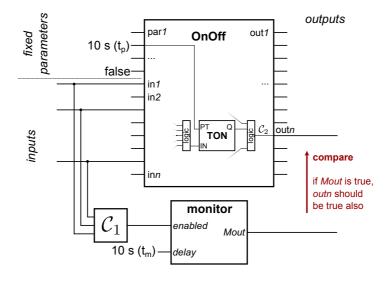

Timing operations, such as timers defined by IEC 61131 (2013), can be considered as function blocks that delay a signal or produce a pulse.

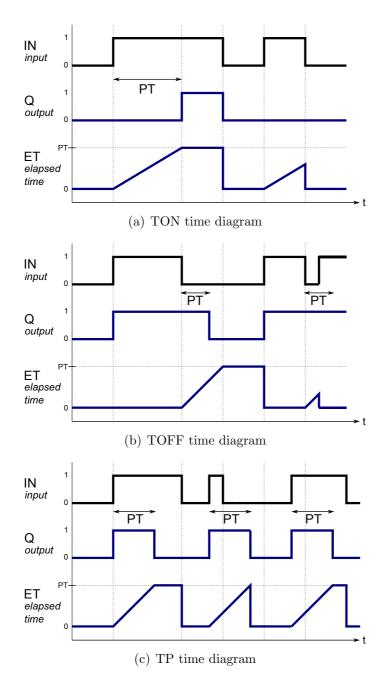

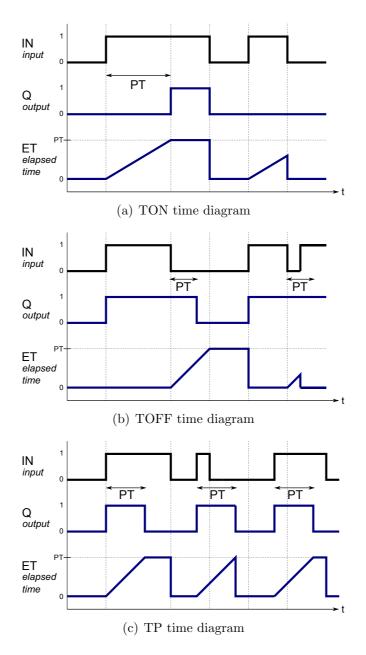

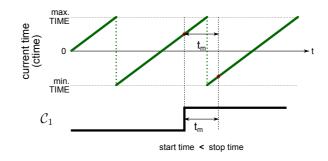

Different types of timers can be found in PLCs. The most common timers are TON (Timer On-delay), TOFF (Timer Off-delay) and TP (Pulse Timer) timers. Fig. 2.8 shows the three timer diagrams. All three timers have the same input and output variables. Two input variables: IN and PT. IN is a Boolean input signal and PT is the delay time. And two output variables: Q and ET. Q is the Boolean output variable and ET is the elapsed time.

**TON:** in this timer, the value of Q will be true after the predefined delay (PT) when IN performs a rising edge, and it will be false if IN is false. The value of ET is increased until PT, starting when a rising edge occurred on IN.

**TOFF:** in this case, the value of Q will be true if IN is true and it will be false after the predefined delay (PT) when IN performs a falling edge. The value of ET is increased until PT, starting when a falling edge occurred on IN.

**TP:** in this case, the value of Q will be true if IN is true and it will be false after the predefined delay (PT), independently of the value of IN. The value of ET is increased until PT, starting when a rising edge occurred on IN.

PLC timers use a specific data type for timing operations called TIME. The IEC 61131 (2013) standard defines this data type as a finite variable and states the following:

"The range of values and precision of representation in these data types is implementation-dependent."

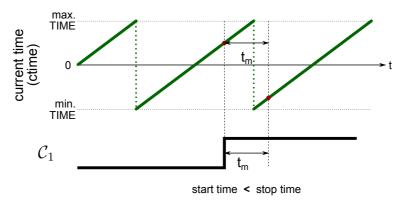

Representing time by a finite variable leads to a non-monotonic time representation as the variable can overflow (c.f. the upper part of 2.9). For example, in Siemens S7 PLCs, the *TIME* data type is defined as a signed 32-bit integer with a resolution of 1 ms (see Siemens (1998b)), having an upper limit of approximately +24 days and a lower limit of -24 days. However, in Schneider and Beckhoff PLCs, the *TIME* data type is an unsigned 32-bit integer with a resolution of 1 ms. In this thesis, the signed time interpretation as defined in Siemens PLCs is considered.

The following section presents some fundamental concepts about formal methods and formal verification.

Figure 2.8: Timer diagrams

Figure 2.9: Consequences of finite time representation

## 2.3 Formal methods and formal verification

The selected strategy to guarantee that PLC programs are compliant with the specification implies to apply formal verification to these programs. This requires the knowledge and understanding of formal methods and formal verification. This section presents a small review of these two fields of research related to this project.

## 2.3.1 Formal methods

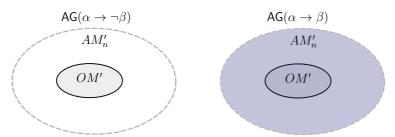

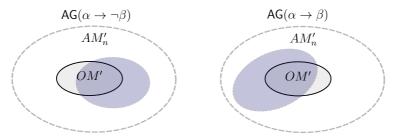

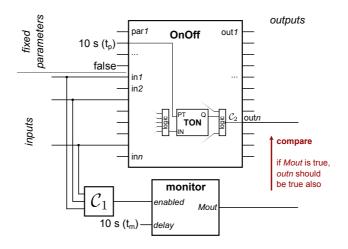

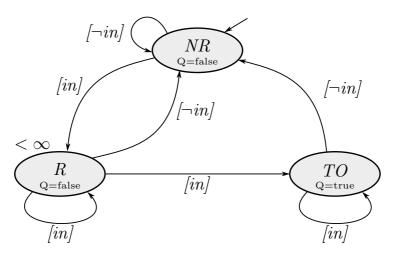

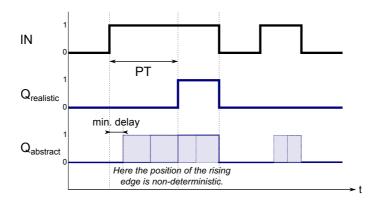

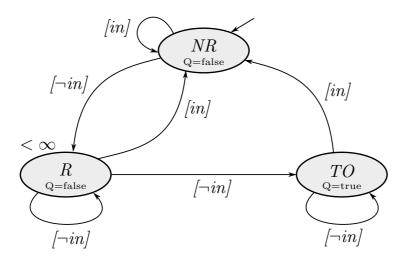

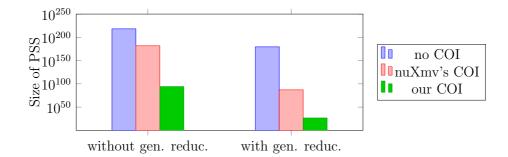

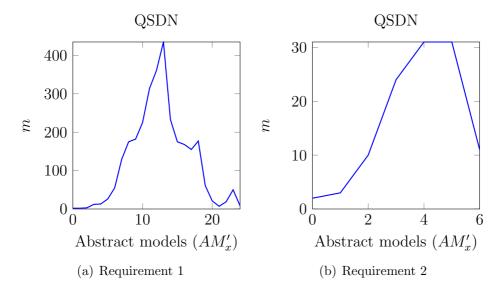

The term "formal methods" has been defined by many authors. According to NASA (1977), formal methods can be defined as follows: