# Development of an FPGA-based Controller PCB used in the Control System of a Modular Multiport Power Converter

By

Mariam Saeed Hazkial Gerges

Submitted to the Department of Electrical Engineering, Electronics, Computers and Systems

in partial fulfillment of the requirements for the degree of Master of Science in Electrical Energy Conversion and Power Systems at the

#### UNIVERSIDAD DE OVIEDO

July 2015

© Universidad de Oviedo 2015. All rights reserved.

| Author       |                          |

|--------------|--------------------------|

| Certified by |                          |

| <u> </u>     | Fernando Briz del Blanco |

|              | Full Professor           |

|              | Thesis Supervisor        |

# Development of an FPGA-based Controller PCB used in the Control System of a Modular Multiport Power Converter

by

#### Mariam Saeed Hazkial Gerges

Submitted to the Department of Electrical Engineering, Electronics, Computers and

Systems

On July 17, 2015, in partial fulfillment of the

requirements for the degree of

Master of Science in Electrical Energy Conversion and Power Systems

#### **Abstract**

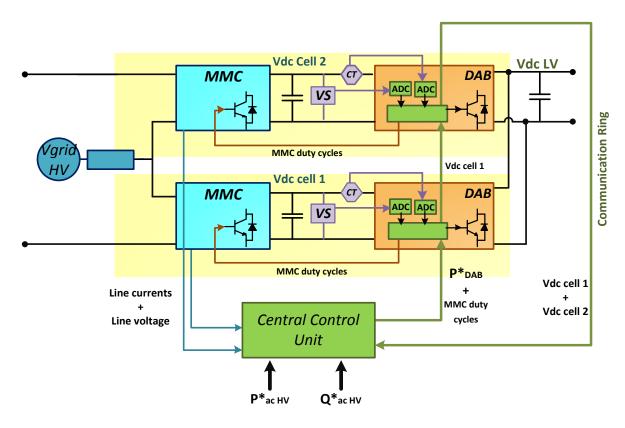

The aim of this thesis is to develop a fully functioning Field Programmable Gate Array (FPGA-based) digital controller printed circuit board to be integrated in a Dual Active Bridge (DAB) module. It will serve as the slave control unit in a partially distributed control structure of a Solid State Transformer (SST). The SST topology consists of stacked Input-Series-Output-Parallel connected modules; each module is composed of a half-bridge cell accompanied by an isolation stage formed by a DAB module.

The work is outlined by four ideas, first understanding the addressed SST topology to get an idea about the slave controller requirements and optimize its design, second, developing the FPGA-based controller PCB design and commissioning the manufactured prototype, third developing the analogue to digital converter needed to interface this digital controller with the controlled system and finally general understanding of the implemented communication link between this developed slave unit and the central control.

Thesis Supervisor: Fernando Briz del Blanco

Title: Full Professor

# Acknowledgments

I am very grateful to my Supervisor Prof. Fernando Briz. I am, in every sense, honored to have him as my Master's Thesis supervisor. Never sparing his valuable time from my help, makes me in debt of his dedication. His utmost trust in my decisions gave me unbelievable confidence and interest in my work. Especially, I would like to thank him for giving me this project experience, for opening many interesting opportunities in front of me and helping improve my skills daily.

Most importantly, I would like to thank my Mother and my Father. I believe that without them, none of this would have been possible. Their unbelievable love and support made miracles during these two years. Their faith in me gave me strength each day.

I attribute most of my success to my twin sister Sarah, for she is always beside me, encouraging, inspiring and sharing the best and the worst moments with me.

I would like to thank my fiancé, Guirguis for his care, for giving meaning to moments in my life and for the happiness he brings about.

I would like to express my gratitude to all the Professors of the Master who saved no effort in passing me their knowledge and helping me in many aspects. I would like to thank Prof. Jorge Garcia for being my mentor throughout the two years of the Master, his respect and appreciation has been inspiring.

I am also thankful to my colleagues especially Dr. Alberto Rodríguez for providing valuable advice.

# Contents

| Abstract   |                                                   | 3  |

|------------|---------------------------------------------------|----|

| Acknowl    | edgments                                          | 4  |

| List of Fi | gures                                             | 9  |

| List of Ta | ables                                             | 11 |

| Glossary   |                                                   | 12 |

| _          | One                                               |    |

| _          | duction                                           |    |

|            | ect Background                                    |    |

|            | ivation                                           |    |

|            | ect description                                   |    |

|            | eton of the document                              |    |

|            | Two                                               |    |

| -          | retical background                                |    |

|            | trol of Power electronic converters               |    |

|            | troller implementation                            |    |

| 2.2.1.     | Analog Vs Digital                                 |    |

| 2.2.2.     | Digital processor options                         |    |

| 2.2.3.     | DSP Vs FPGA control implementation choice         | 22 |

| 2.3. Proj  | ect-specific controller selection                 | 24 |

| Chapter    | Three                                             | 26 |

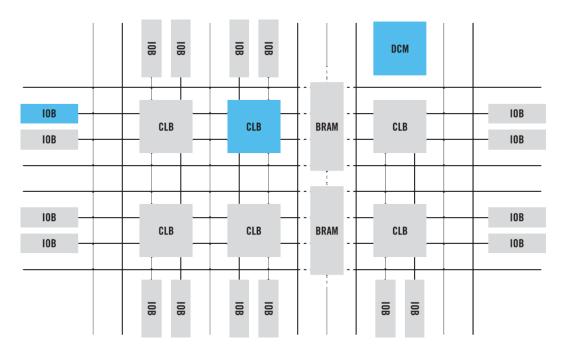

| _          | FPGA                                              |    |

|            | f understanding of FPGA technology and PCB design |    |

| 3.1.1.     | FPGA technology                                   |    |

| 3.1.2.     | State-of-the-art in FPGA                          |    |

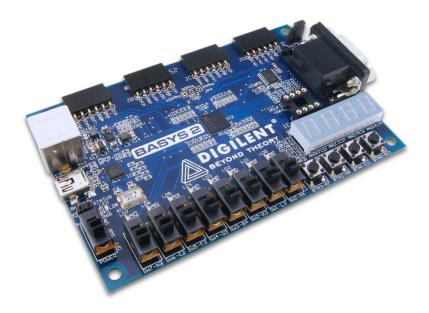

| 3.1.3.     | FPGA-based PCB design                             | 29 |

| 3.2 Deta   | niled function                                    | 30 |

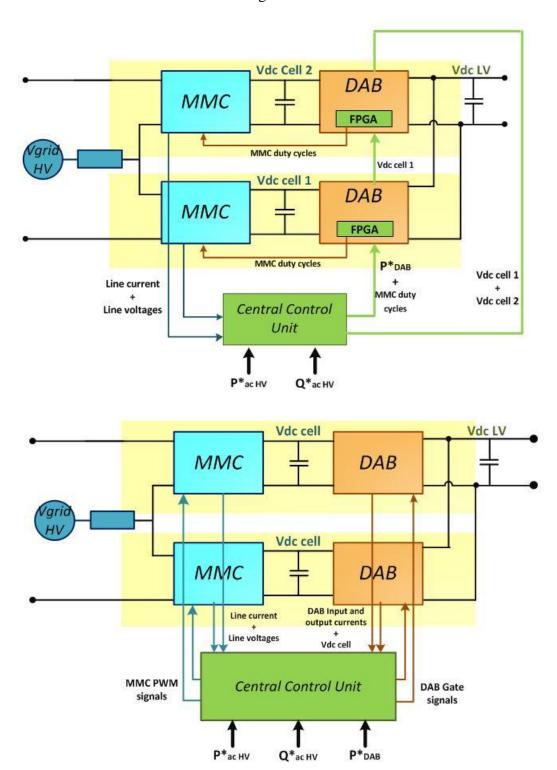

| 3.3. The 1  | reason for developing the slave FPGAs           | 34 |

|-------------|-------------------------------------------------|----|

| 3.4. Conf   | iguration of the FPGA                           | 34 |

| 3.4.1.      | JTAG configuration mode                         | 36 |

| 3.4.2.      | Master Serial configuration structure           | 37 |

| 3.4.3.      | Configuration Process                           | 38 |

| 3.5. Com    | ponents included in the slave FPGA PCB:         | 39 |

| 3.5.1.      | Digital computational device/ Processor / FPGA: | 39 |

| 3.5.2.      | Memory                                          | 42 |

| 3.5.3.      | The crystal oscillator / the clock:             | 43 |

| 3.5.4.      | Connector to the PC                             | 44 |

| 3.5.5.      | Voltage regulator                               | 44 |

| 3.5.6.      | Interface connector                             | 45 |

| 3.5.7.      | Passive elements                                | 46 |

| Chapter 1   | Four                                            | 47 |

| 4. Devel    | oping the PCB                                   | 47 |

| 4.1. Design | gn specifications                               | 47 |

| 4.2. Design | gn challenges/issues                            | 48 |

| 4.2.1.      | FPGA Package related issue                      | 48 |

| 4.2.2.      | FPGA configuration issue                        | 51 |

| 4.2.3.      | PROM configuration issue                        | 51 |

| 4.3. Deve   | eloping the Design                              | 52 |

| 4.3.1.      | Schematic of the FPGA PCB                       | 52 |

| 4.3.2.      | Layout design of the board                      | 62 |

| 4.4. Testi  | ng procedure                                    | 69 |

| 4.4.1.      | Testing the power points;                       | 69 |

| 4.4.2.      | Testing the CLOCK signal;                       | 69 |

| 4.4.3.      | Configuration signals;                          | 70 |

| 4.4.4.      | Connecting the PCB to the computer;             | 70 |

| 4.4.5.      | Configuring the FPGA and the PROM               | 70 |

| 4.5. Analo | ogue to Digital Module                                   | 70 |

|------------|----------------------------------------------------------|----|

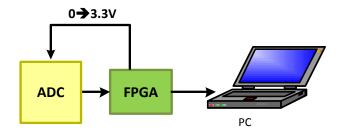

| 4.5.1.     | Role of the DAB ADC in the system                        | 71 |

| 4.5.2.     | Role of the MMC ADC                                      | 72 |

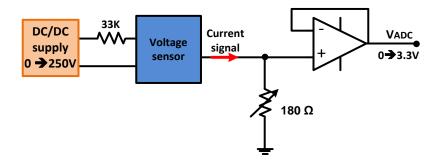

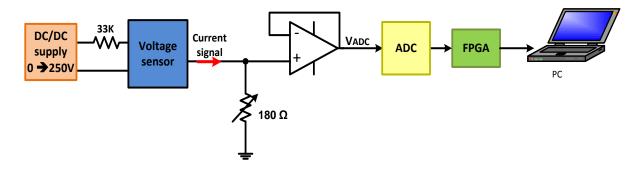

| 4.5.3.     | Design and implementation                                | 72 |

| 4.5.4.     | Testing                                                  | 75 |

| 4.6. MMC   | C cell voltage adaptation circuit                        | 76 |

| 4.7. Com   | munication with the central control unit                 | 78 |

| 4.7.1.     | Function of the communication link in the control scheme | 78 |

| 4.7.2.     | Selected protocol                                        | 79 |

| 4.7.3.     | Theoretical implementation                               | 80 |

| 4.8. Com   | missioning Process                                       | 81 |

| 4.8.1.     | Debugging or trouble shooting                            | 81 |

| 4.8.2.     | Final debugging stage /finalizing the design             | 94 |

| Chapter F  | Five                                                     | 96 |

| 5. Conclu  | usions and future work                                   | 96 |

| 5.1. Conc  | lusions                                                  | 96 |

| 5.2. Futur | re Work                                                  | 97 |

| 5.2.1.     | Enhancing the developed design:                          | 97 |

| 5.2.2.     | Integrating the Slave FPGA units into the SST prototype  | 98 |

| Reference  |                                                          | 99 |

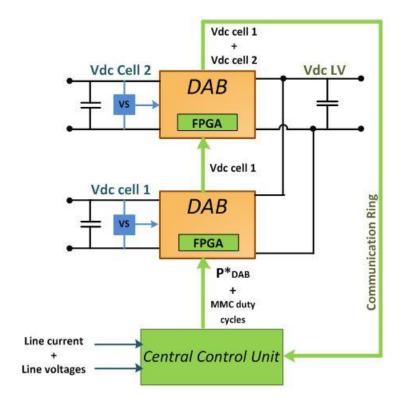

# List of Figures

| Figure 1: An overall schematic of the addressed modular multiport converter topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 2: The FPGA internal structure [18].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27        |

| Figure 3: The reference design, Basys2 PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30        |

| Figure 4: (a) upper, partially distributed control structure. (b) Lower, centralized control st                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | tructure. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31        |

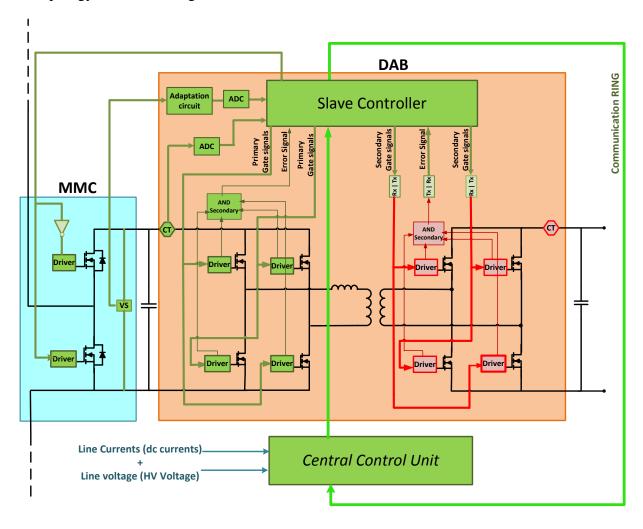

| Figure 5: A detailed scheme of one MMC-DAB module.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33        |

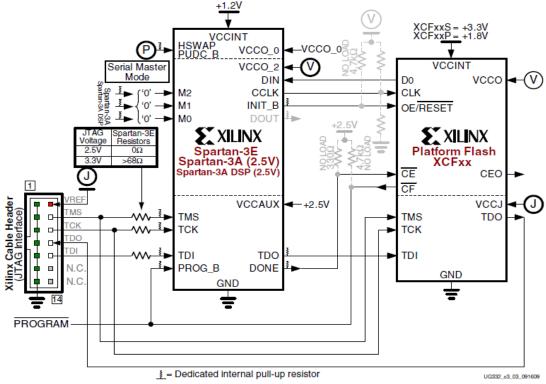

| Figure 6: the Master Serial configuration structure [27].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37        |

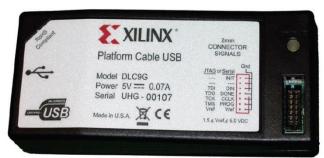

| Figure 7: The Platform USB Cable II [28].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38        |

| Figure 8: The JTAG connector pin labels [28]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39        |

| Figure 9: Design summary in the ISE <sup>TM</sup> software showing an adequate utilization perce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nt when   |

| using the 250K gates FPGA, which meets the design requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41        |

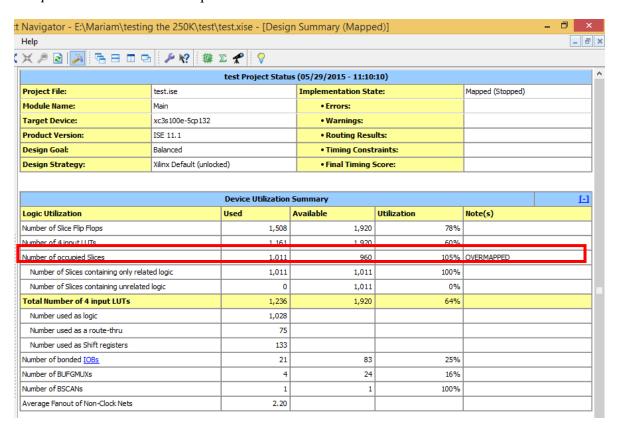

| Figure 10: Design summary in the $ISE^{TM}$ software showing an Overmapped FPGA utilization of the state of | tion due  |

| to the insufficient number of logic gates (when using the 100K gates) with respect to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e design  |

| needs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42        |

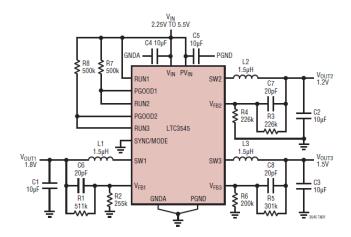

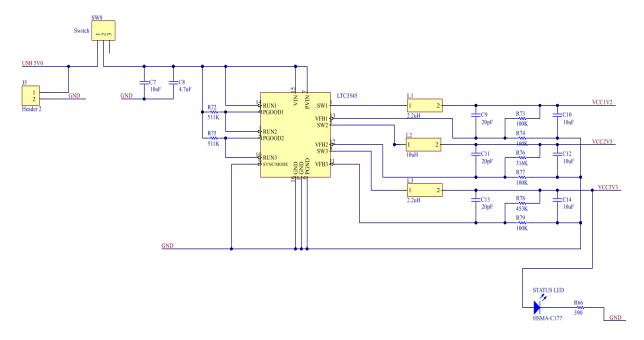

| Figure 11: Voltage regulator LTC3545 circuit recommended by its datasheet [33]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45        |

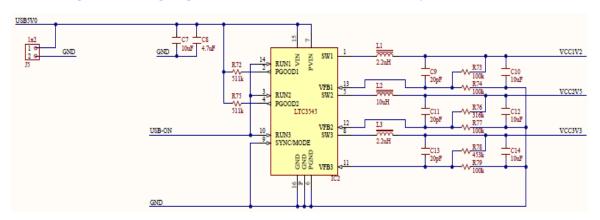

| Figure 12: voltage regulator circuit implemented in the reference design [34]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45        |

| Figure 13: The 100-pin DIMM socket.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46        |

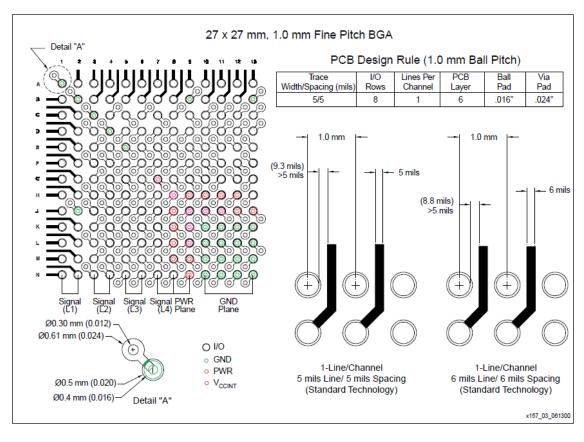

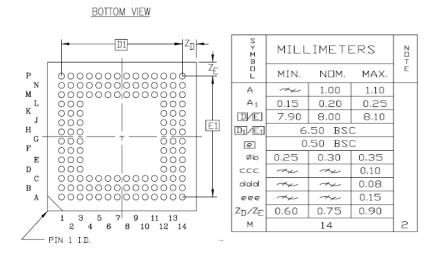

| Figure 14. Shows the FG676 PC Board Layout/Land Pattern [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48        |

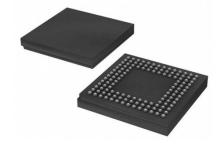

| Figure 15. The CP132 BGA package [39].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49        |

| Figure 16: shows the pad layout dimensions of the CP132 [40].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 49        |

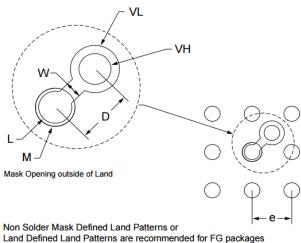

| Figure 17. Suggested board layout of soldered pads for BGA, CSP and CCGA packages. [                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | [41] 50   |

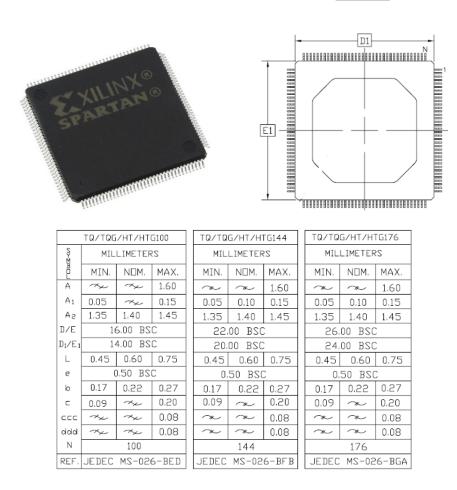

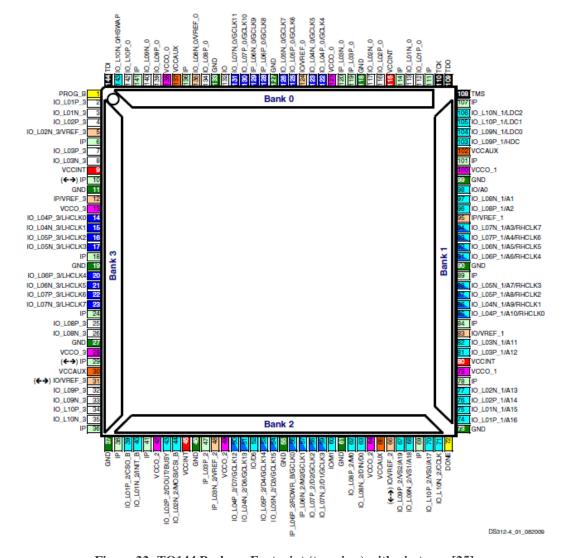

| Figure 18: The TQFP (TQ144/TQG144) Spartan FPGA Package [42]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51        |

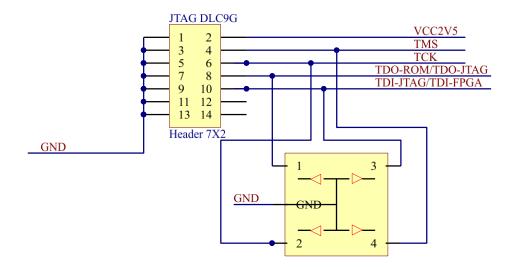

| Figure 19: The connection of the JTAG along with the ESD protection diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55        |

| Figure 20: The Voltage regulator schematic in the developed FPGA design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56        |

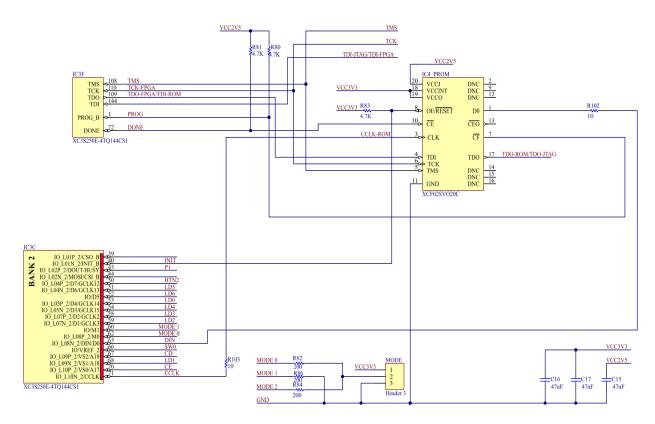

| Figure 21: The Schematic of the PROM showing the connections to the FPGA JTAG port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | and the   |

| BANK 2 which contains the serial data input and the MODE pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57        |

| Figure 22: TQ144 Package Footprint (top view) with pin types [25].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58        |

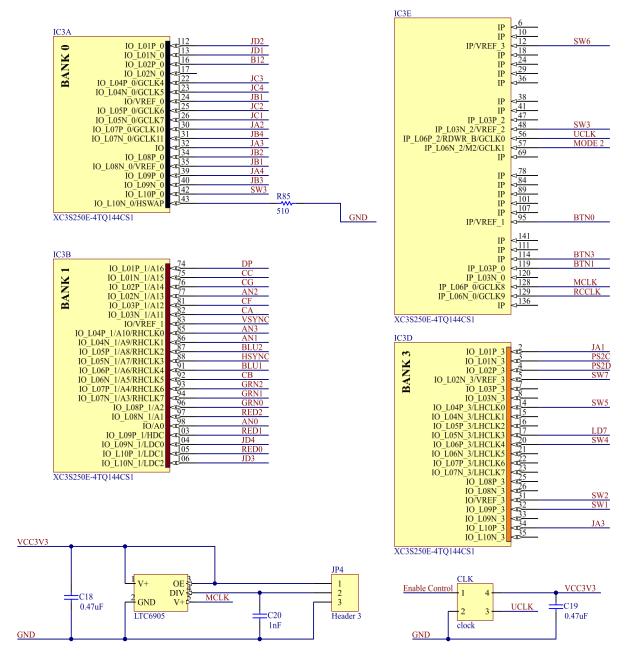

| Figure 23: The schematic of FPGA BANKs and the Clocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60        |

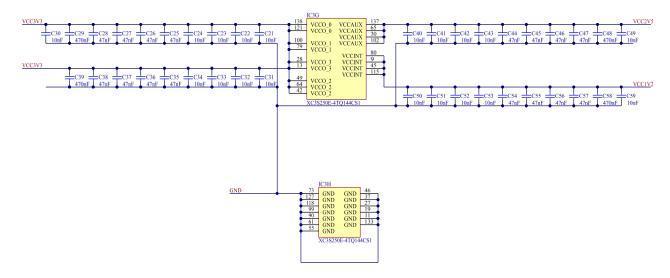

| Figure 24: The Power and Ground pins along with their relevant decoupling capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61        |

| Figure 25: The 100-pin interface connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 62        |

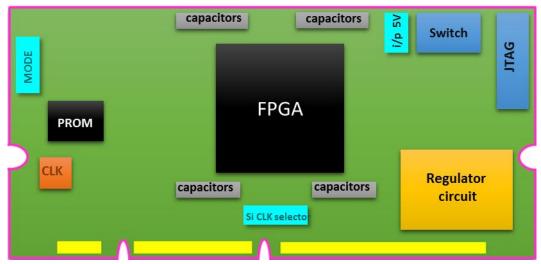

| Figure 26: The simple structure of the developed Layout Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65        |

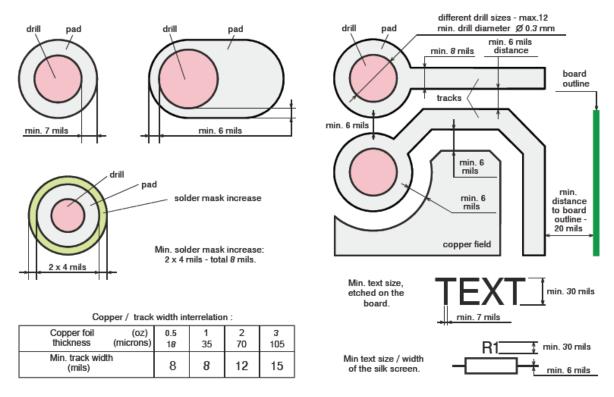

| Figure 27: The PCB manufacturer (MICRON-20) capabilities for developing the PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67        |

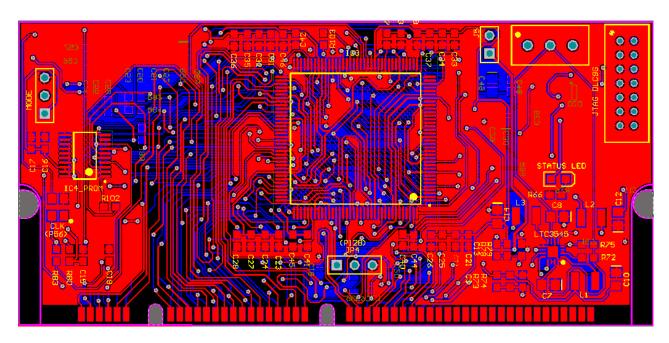

| Figure 28: The developed Layout design shown from Altium                                    |

|---------------------------------------------------------------------------------------------|

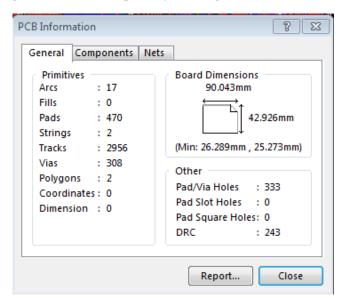

| Figure 29: The developed design PCB information report generated from Altium                |

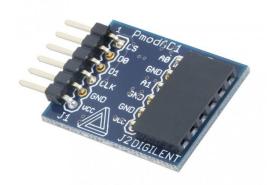

| Figure 30: The commercial AD module PmodAD1 [51]                                            |

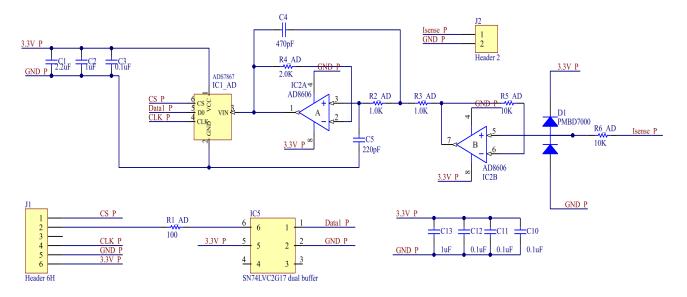

| Figure 31: The Altium Schematic of the developed ADC                                        |

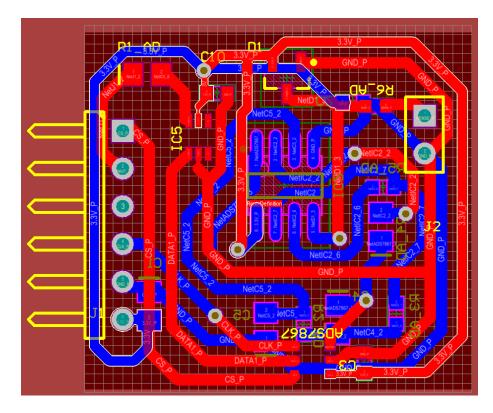

| Figure 32: The developed Altium Layout Design of the ADC                                    |

| Figure 33: The developed ADC PCB                                                            |

| Figure 34: Testing the ADC                                                                  |

| Figure 35: The adaptation circuit of the MMC cell voltage                                   |

| Figure 36: Testing the adaptation circuit with the ADC                                      |

| Figure 37: the communication ring linking the slave units with the central unit             |

| Figure 38: the developed slave FPGA-based digital controller PCB                            |

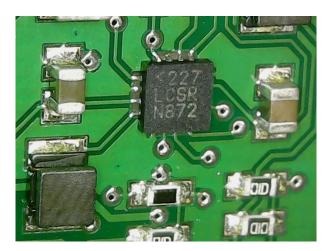

| Figure 39: the voltage regulator LTC3545 pictured from the Slave FPGA PCB                   |

| Figure 40: The Core3S250E from Waveshare TM reference design with JTAG                      |

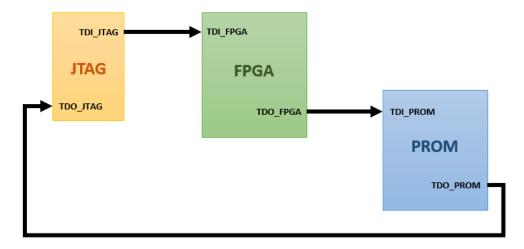

| Figure 41: the simple configuration chain connection.                                       |

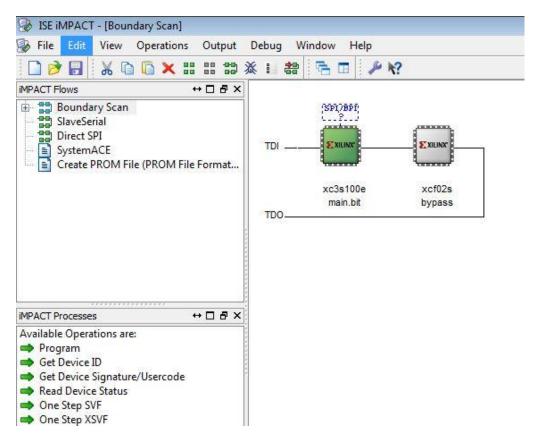

| Figure 42: the chain is initialized detecting the presence of the FPGA and the PROM 87      |

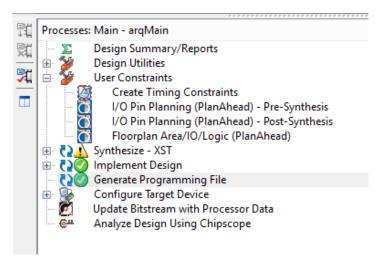

| Figure 43: the Generate Programming file option, generating the .bit file                   |

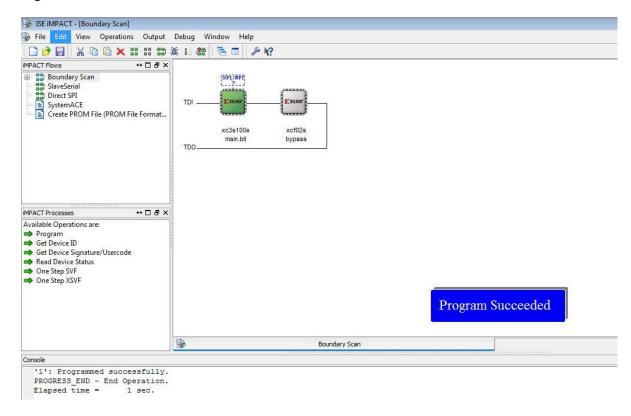

| Figure 44: Successful programming of the FPGA indicated by the iMPACT software              |

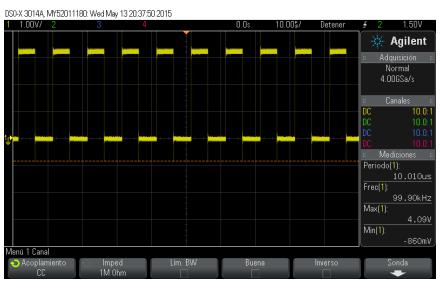

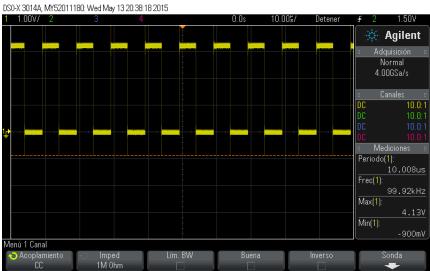

| Figure 45, the PWM signals generated on the edge connector to test the configuration of the |

| FPGA PCB                                                                                    |

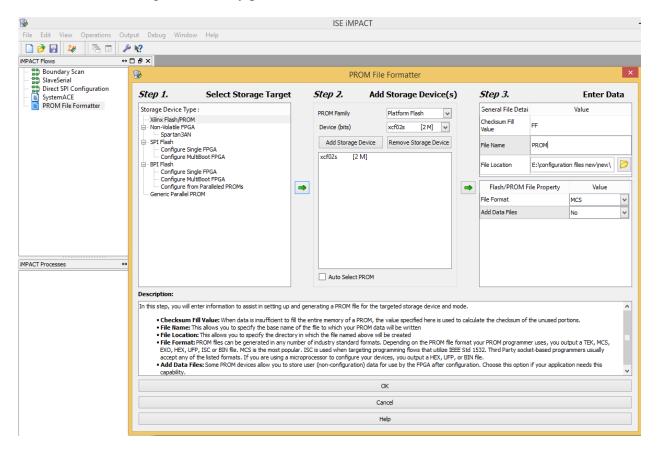

| Figure 46: Generating the .mcs file to program the PROM from the iMPACT software 90         |

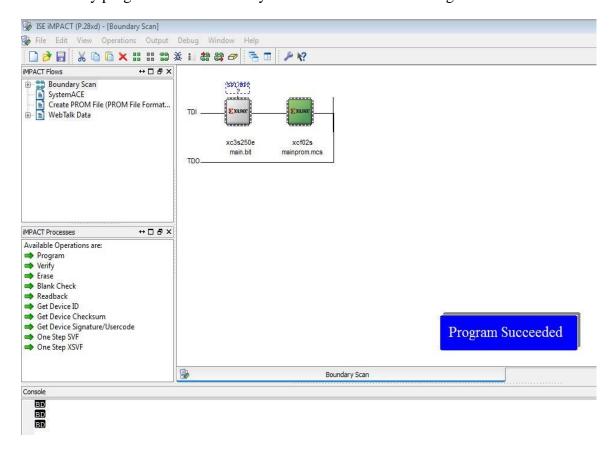

| Figure 47: The PROM is successfully programmed.                                             |

# List of Tables

| Table 1: Comparison between analog and digital Control implementations                   | 20  |

|------------------------------------------------------------------------------------------|-----|

| Table 2: the FPGA configuration pins [25].                                               | 36  |

| Table 3: Number of Bits to program a Spartan-3E FPGA and the smallest Platform Flash     |     |

| PROM [25]                                                                                | 43  |

| Table 4: Board routability guidelines with Xilinx fine-pitch BGA Packages. Recommended I | PCB |

| design rules (mm) [41].                                                                  | 50  |

| Table 5: Types of Pins on Spartan-3E FPGAs                                               | 57  |

| Table 6: The detailed PROM and Spartan-3E TQ144 package power pins.                      | 69  |

| Table 7: The connection of the configuration lines going from the FPGA to the PROM       | 92  |

| Table 8: The connection of the configuration lines going from the PROM to the FPGA       | 93  |

| Table 9: Partition of the interface connector Pins Mapping document.                     | 95  |

## Glossary

**SST** Solid-State-Transformer

**DAB** Dual-Active-Bridge

**PCB** Printed Circuit Board

**SiC** Silicon Carbide

**SPS** Single-Phase-Shift